單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。

2018-02-28 09:41:12 8339

8339

我們為了實現動態圖像的濾波算法,用串口發送圖像數據到FPGA開發板,經FPGA進行圖像處理算法后,動態顯示到VGA顯示屏上,前面我們把硬件平臺已經搭建完成了,后面我們將利用這個硬件基礎平臺

2019-01-02 16:26:23 4706

4706 根據交流采樣的原理,設計出基于FPGA開方算法,解決了實時計算電壓有效值和頻率的問題。充分發揮FPGA硬件并行計算的特性,實現高速運算和可靠性的結合, 能夠較好地解決精度與速度

2011-10-03 11:02:02 2592

2592 如何用FPGA實現串行算法?我想用FPGA做一個隨機數發生器,然后想用李世剛那個超素數法,但是要生成1024bit的01序列,它們是用第一bit順推第二bit 的產生。請問大神 ,有沒有沒有好的辦法

2013-03-11 19:23:49

流水方式對復數數據實現了加窗、FFT、求模平方三種運算。整個設計采用流水與并行方式盡量避免瓶頸的出現,提高系統時鐘頻率,達到高速處理。實驗表明此處理器既有專用ASIC電路的快速性,又有DSP器件的靈活性的特點,適合用于高速數字信號處理。

2012-08-12 11:49:01

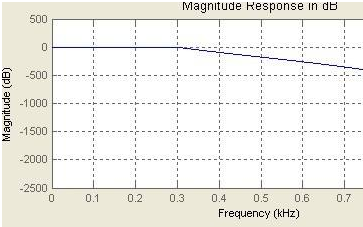

采集數據中的量化噪聲,在進行數據壓縮前采用濾波的預處理技術。介紹LZW算法和滑動濾波算法的基本理論,詳細闡述用單片FPGA實現兩種算法的方法。最終測試結果表明,該設計方案能夠有效濾除數據中的高頻噪聲

2010-04-24 09:05:21

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

4 個時鐘后連續輸出運算結果。各個單元協調一致的并行工作, 提高了系統時鐘頻率, 達到了高速處理。采用塊浮點機制, 動態擴大數據范圍, 在速度和精度之間得到折衷。模塊化設計, 易于實現更多

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統的性能。傳統的實現方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

實現各種數字信號處理算法的工程方法。本書將理論與實踐相結合,給出了相應算法的硬件結構,并配有時序圖,以幫助讀者深入理解設計思路。第1章 現場可編程邏輯門陣列(FPGA)技術現狀1.1 FPGA已進入

2012-04-24 09:33:23

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

)、離散余弦變換(DCT)、小波變換、數字濾波器(有限脈沖響應(FIR)、無限脈沖響應(IIR)和自適應濾波器)以及數字上下變頻器。這些算法中,每一種都有一些結構性的元件可以用并行方法實現。而FPGA

2021-12-15 06:30:00

傳統數字濾波器硬件的實現主要采用專用集成電路(ASIC)和數字信號處理器(DSP)來實現。FPGA內部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結構,這種結構特別適用于并行處理結構,相對于傳統方法來說,其并行度和擴展性都很好,它逐漸成為構造可編程高性能算法結構的新選擇。

2019-08-29 06:43:38

TMS320C6713.處理能力高達2400MIPS,結合該芯片的8指令并行運行的特點,對程序進行優化,可大大提高運算速度,實現“二次解調”實時處理算法。3. 數據處理3.1 PGC解調原理PGC解調

2021-07-05 11:23:33

傳輸,因而只能做需求數據較少的測向工作,并不能做實時波束形成。為了克服這些困難,這里將測向數據和波束形成數據分開進行傳輸,采用LVDS技術解決多通道高速數據傳輸,選擇內置高性能DSP內核的高密度FPGA并行實現波束形成中的大量復乘運算。

2020-11-25 06:49:42

的并行運算單元。4 結 論 本文闡述了無源雷達系統中基于FPGA的實時互相關運算器的一種實現方案。該運算器由1塊500 000門的FPGA芯片完成2路信號的互相

2009-09-19 09:25:42

基于FPGA的高速實時圖像采集和自適應閾值算法提出了基于FPGA的圖像處理自適應閾值算法,實現了激光光斑中心的高速實時檢測。采用3×3窗口模塊和自適應閾值模塊,先對CCD輸入數據進行處理,判斷光斑

2012-08-11 15:38:18

` 本帖最后由 ninghechuan 于 2017-9-1 07:04 編輯

在這一篇開篇之前,我需要解決一個問題,上一篇我們實現了基于FPGA的均值濾波算法的實現,最后的顯示效果圖上發現有

2017-09-01 07:04:36

` 本帖最后由 ninghechuan 于 2017-8-30 08:20 編輯

我們為了實現動態圖像的濾波算法,用串口發送圖像數據到FPGA開發板,經FPGA進行圖像處理算法后,動態顯示到

2017-08-28 11:34:10

:基于FPGA的均值濾波算法實現第五篇:深刻認識ShiftRAM學習筆記番外篇:數字圖像處理界標準圖像 Lena 后面的故事第六篇:基于FPGA的中值濾波算法實現第七篇:基于FPGA的Sobel邊緣檢測的實現

2017-09-22 13:20:55

基于FPGA的超高速FFT硬件實現介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA

2009-06-14 00:19:55

傳統數字濾波器硬件的實現主要采用專用集成電路(ASIC)和數字信號處理器(DSP)來實現。FPGA內部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結構,這種結構特別適用于并行處理結構,相對于傳統方法來說,其并行度和擴展性都很好,它逐漸成為構造可編程高性能算法結構的新選擇。

2019-10-22 07:14:04

跪求各位大神有沒有基于verilog HDL的高速對數運算模塊設計的CORD IC算法實現自然對數運算的代碼

2016-03-10 12:39:28

請問一下如何用FPGA實現FFT算法?

2021-04-08 06:06:26

對于自主機器人導航和其它機器視覺應用來說,實時深度感知是很關鍵的。目前通過立體圖像來計算深度的算法計算量很大,例如差異測繪,要占用CPU大量的時間,或者需要用昂貴的器件進行實時操作。

2019-10-17 08:28:30

如何用中檔FPGA實現多相濾波器?

2021-04-29 06:30:57

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。在單片機

2021-01-13 07:29:27

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。在單片機

2022-01-14 08:14:06

如何用單片機實現數字濾波,如果想要采用數字濾波算法克服隨機干擾的誤差這方法可行嗎?

2021-03-06 08:10:00

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波...

2022-01-07 06:30:56

處理器(FPGA,DSP)是一個“瓶頸”;基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在一片FPGA中實現數字信道化成為可能。

2019-08-22 08:01:34

本文利用FPGA乘累加的快速算法,可以設計出高速的FIR數字濾波器,使FPGA在數字信號處理方面有了長足的發展。

2021-05-07 06:31:21

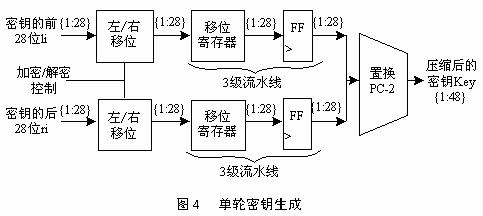

能夠充分利用有限位長。這樣處理比定點方法擴大了動態范圍,并且提高了精度,比浮點運算在速度上有了提高。塊浮點結構如圖4所示。3 結 語著重討論基于FPGA的64點高速FFT算法的實現方法。采用高基數結構和流水線

2019-06-17 09:01:35

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實現實時時鐘或時間和日期計數器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

在IPSec協議中認證使用SHA-1和MD5單向散列函數算法實現,通過使用FPGA高速實現SHA-1消息認證算法。

2021-04-13 06:02:01

并行流水結構FIR的原理是什么基于并行流水線結構的可重配FIR濾波器的FPGA實現

2021-04-29 06:30:54

本文研究的就是在FPGA設計平臺上設計硬件電路,實現數字圖像的空域濾波算法。

2021-04-30 06:29:41

現代通信信號處理發展到3G、4G時代后,每秒上百兆比特處理速度的要求對于自適應處理技術是一個極大的挑戰。使用具有高度并行結構的FPGA實現自適應算法以及完成相應的調整和優化,相比于在DSP芯片上的算法實現可以達到更高的運行速度。

2019-08-23 08:03:10

的信息并行存在,因此可以并行對其施以相同的操作,使得圖像處理的速度大大提高,這正好適合映射到FPGA架構中用硬件算法得以實現。本篇闡述了基于FPGA設計一個能夠實時采集、實時處理并實時顯示的數字圖像處理系統的設計思想和流程,分析了攝像頭接口的時序;闡述了圖像...

2021-07-28 06:06:26

想用FPGA實現雙邊濾波算法,有懂得能說一下具體的實現步驟嗎

2017-03-21 15:41:13

FPGA設計平臺上設計硬件電路,實現數字圖像的空域濾波算法。 1 數字圖像空域濾波算法 數字圖像空域濾波算法的實現步驟如圖1所示,左邊的部分是要處理的圖像的某一部分,中間是對圖像進行處理的3×3模板

2011-02-24 14:20:18

分布式的濾波器算法是什么?一種基于FPGA分布式算法的濾波器設計實現

2021-04-29 07:13:23

用FPGA硬件實現。 現在我沒有FPGA硬件實現的經驗,不知道如何用FPGA硬件實現小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。在單片機

2022-01-18 07:00:34

FIR數字濾波器分布式算法的原理及FPGA實現摘要:在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘積-積結構相比,具有并行處理的高效性特點。詳細研

2009-10-27 14:05:48 57

57 應用分布式算法在FPGA平臺實現FIR低通濾波器李明緯 黃世震(福州大學 福建省微電子集成電路重點實驗室福州 350002)摘要:在利用FPGA實現數字信號處理方面,分布式算法發揮

2009-12-14 11:09:08 29

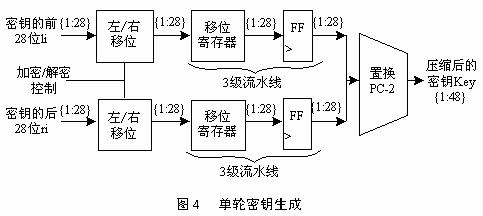

29 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 44

44 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。引 言

2006-03-13 19:36:42 651

651

如何用用FPGA實現FIR濾波器

你接到要求用FPGA實現FIR濾波器的任務時,也許會想起在學校里所學的FIR基礎知識,但是下一步該做什么呢?哪些參數是重

2009-03-30 12:25:45 4503

4503

摘要: 針對在FPGA中實現FIR濾波器的關鍵--乘法運算的高效實現進行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設計了FIR濾波器。通過FPGA仿零點驗證

2009-06-20 14:09:36 677

677

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。

關鍵詞:3-DES

2009-06-20 14:22:00 1317

1317

本文介紹的基于PCI總線的FPGA計算平臺的系統實現:通過在PC機上插入擴展PCI卡,對算法進行針對并行運算的設計,提升普通PC機對大計算量數字信號的處理速度。本設計采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

提出了一種適用于FPGA的改進型線性插值算法,該算法基于并行流水線方式實現,充分發揮了FPGA的高速并行處理能力。

2011-11-22 14:29:49 1089

1089

基于FPGA的高速實時圖像采集和自適應閾值算法

2016-05-10 13:45:28 21

21 實時圖像增強算法改進及FPGA實現,下來看看

2016-09-17 07:28:24 14

14 基于改進的引導濾波算法的多曝光圖像融合

2017-01-08 14:47:53 3

3 基于位并行DA結構的高速FIR濾波器_周云

2017-01-07 21:39:44 4

4 基于FPGA的實時圖像中值濾波算法及實現_蔣濤

2017-03-19 11:38:26 13

13 引導濾波算法被大量用于圖像處理領域中,在去雨雪、去霧、前景提取、圖像去噪、圖像增強、級聯采樣等方面有很好的處理效果。但是對于實時應用,軟件實現難以滿足需要。提出了在SDSoC環境下利用軟硬件協同開發

2017-11-16 14:40:18 1253

1253 線性相位FIR濾波器的對稱性減小了硬件規模;利用分割查找表的方法減小了存儲空間;采用并行分布式算法結構和流水線技術提高了濾波器的速度,在FPGA上實現了該濾波器。

2017-11-24 15:17:27 2942

2942 ,常規做法是利用插值和抽取的方法實現數字信號的變采樣處理,這種方法實現復雜,硬件成本高。文中提出了一種高速并行成型濾波器的FPGA實現方法,這種基于群延時結構的查找表算法,所需的查找表只需存儲單位沖擊響應的采樣值,

2018-02-23 10:14:22 0

0 本文是基于FPGA實現Cordic算法的設計與驗證,使用Verilog HDL設計,初步可實現正弦、余弦、反正切函數的實現。將復雜的運算轉化成FPGA擅長的加減法和乘法,而乘法運算可以用移位運算代替

2018-07-03 10:18:00 2349

2349

數據采集系統的總體架構如圖1所示,其中PCI核、DMA控制器與A/D控制器均在FPGA內部實現。為實現多路并行采樣,可選用多片A/D器件并行處理的方式,在FPGA的高速狀態機控制下,完成模擬信號經過

2018-08-28 10:16:07 12734

12734

開方運算作為數字信號處理(DSP)領域內的一種基本運算,其基于現場可編程門列(FPGA)的工程實現具有較高的難度。本文分析比較了實現開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

6 在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法,采用Verilog HDI 語言描述

2020-09-14 17:49:56 9

9 在視頻圖像獲取過程中“由于噪聲對圖像序列的降質”需要設計實時噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應卡爾曼濾波算法“并討論了自適應卡爾曼濾波算法的簡化”以利于硬件實現自適應卡爾曼濾波器“并進行了簡化算法仿真”完成基于FPGA實現的實時自適應卡爾曼濾波器的設計。

2021-01-22 14:29:29 22

22 在視頻圖像獲取過程中“由于噪聲對圖像序列的降質”需要設計實時噪聲濾波器。討論了視頻圖像的卡爾曼濾波問題及自適應卡爾曼濾波算法“并討論了自適應卡爾曼濾波算法的簡化”以利于硬件實現自適應卡爾曼濾波器“并進行了簡化算法仿真”完成基于FPGA實現的實時自適應卡爾曼濾波器的設計。

2021-01-22 14:29:29 13

13 提出了一種基于多相濾波器的并行有限脈沖響應(finite impulse response,FIR)濾波器結構,可以有效提高濾波器運算的吞吐率,與傳統的串行濾波器結構比,并行濾波器運算速度可以提高

2021-01-28 17:22:00 15

15 提出了一種基于多相濾波器的并行有限脈沖響應(finite impulse response,FIR)濾波器結構,可以有效提高濾波器運算的吞吐率,與傳統的串行濾波器結構比,并行濾波器運算速度可以提高

2021-01-28 17:22:00 7

7 FPGA,通過并行處理結構及流水線技術,可實時處理每秒50幀780×582×12bits的可見光圖像。在處理視頻的過程中,由前一幀圖像的直方圖信息,來增強后一幀圖像。理論分析和實驗結果均表明,該算法克服了直方圖均衡及平臺直方圖均衡增強

2021-02-03 15:21:00 10

10 出了四核心嵌入式并行處理器FPEP的結構設計并建立了FPGA驗證平臺.為了對多核處理器平臺性能進行評測,提出了基于OpenMP的3種可行的圖像處理領域的經典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 本文提出了一種用FPGA實現星載合成孔徑雷達實時成像處理器的方法,用來實現星載SAR的CS算法(或RMA算法).該實時成像處理器由7片Xilinx公司的商業FI:‘GA實現,其中4片作為并行的處理

2021-02-05 15:22:46 14

14 提出一種新的高階FIR濾波器的FPGA實現方法。該方法運用多相分解結構對高階FIR濾波器進行降階處理,采用改進的分布式算法來實現降階后的FIR濾波器。設計了一系列階數從8到1 024的FIR濾波

2021-03-23 15:44:54 30

30 及布局布線,并用ModelSim和Matlab對設計作了聯合仿真。結果表明,通過利用FPGA器件中大量的乘法器、邏輯單元及存儲器等硬件資源,采用全并行加流水結構,可在一個時鐘節拍內完成32點FFT運算的功能,設計最高運算速度可達11 ns,可實現對高速A/D采樣數據的實時處理.

2021-03-31 15:22:00 11

11 圖像濾波是圖像預處理過程中葦要的組成部分,而基于FPGA的濾波算法相對軟件算法而言具有高度的并行性。能滿足實時圖像處理的要求.同時也具有靈活的硬件可編程性;簡要說明了中值濾波的原理.介紹并比較了標準

2021-04-01 11:21:48 41

41 本文給出一種實時計算場景稠密深度圖的多目立體視覺機設計與實現方法。立體視覺機使用多個微型攝像機同步獲取場景圖像,采用圖像修正、LoG濾波、多立體圖像對匹配和稠密深度圖等并行算法,利用FPGA的大規模

2021-04-02 09:33:00 21

21 網格建模是數字幾何處理領域的基礎性硏究冋題。為了提高網格建模的簡便性和魯棒性,首先提岀了一種非線性的引導濾波算法。濾波過程在法向域進行,濾波后的法向是引導網格法向的局部二次變換;然后,應用上述算法

2021-06-03 15:24:28 2

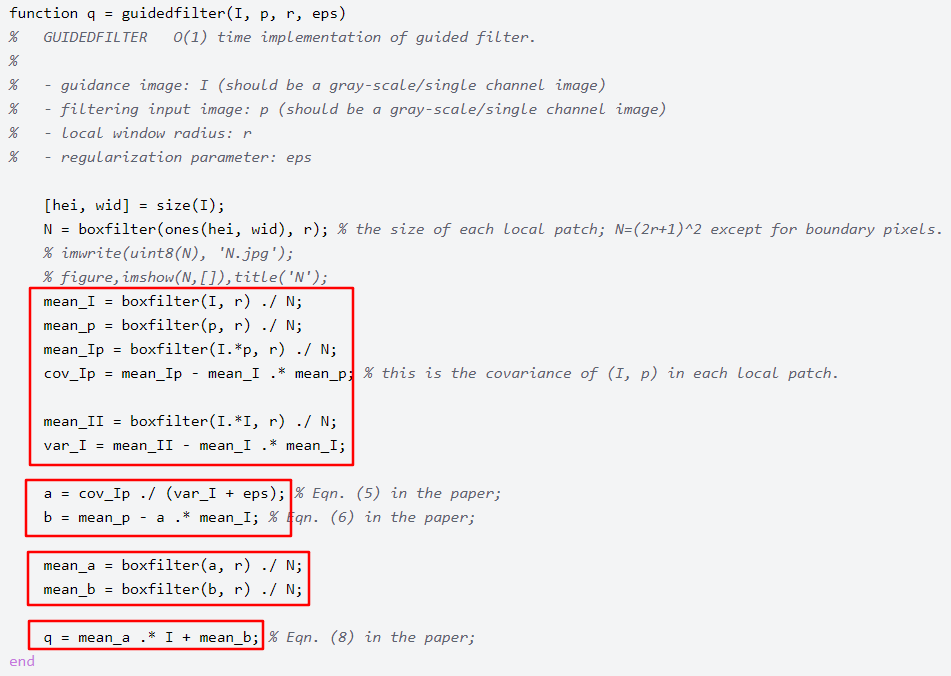

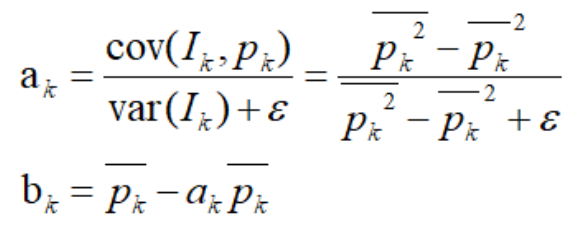

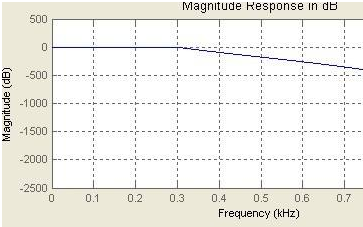

2 ,如何用FPGA并行高速運算,最小的代碼實現實時的引導濾波算法。 首先,給出上篇中最后的matlab 引導濾波的代碼,如下所示。 其中框框中為主要的計算過程,下一圖為計算a/b的最后的公式(引導圖=本身)。 雙邊濾波由于其只是在空間距

2021-08-10 14:27:15 3193

3193

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。

2022-07-03 10:55:37 2166

2166 FPGA以擅長高速并行數據處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現今火爆的AI應用,都離不開卷積、濾波、變換等基本的數學運算。

2022-10-31 14:48:15 2413

2413 和移位操作。這些結構需要占用器件較多的LE(邏輯元件)資源,設計周期長,工作頻率低,實時性差。本文提出一種基于Stratix系列FPGA器件的新的實時高速脈動FIR濾波器的快速實現方法。利 用FGPA集成的DSP(數字信號處理器)乘加模塊定制卷積運算單元,利用VHDL(甚高速集成電路硬件描述

2022-12-01 10:20:05 698

698 由于FPGA可以對算法進行并行化,所以FPGA 非常適合在可編程邏輯中實現數學運算。

2023-05-15 11:29:15 2057

2057

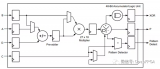

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了復現以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 653

653

點擊上方 藍字 關注我們 一、前言 FPGA以擅長高速并行數據處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現今火爆的AI應用,都離不開卷積、濾波、變換等基本的數學運算。但由于FPGA

2023-07-19 14:25:02 794

794

FPGA以擅長高速并行數據處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現今火爆的AI應用,都離不開卷積、濾波、變換等基本的數學運算。但由于FPGA的硬件結構和開發特性使得其對很多算法

2023-09-05 11:45:02 267

267 引言 LMS(最小均方)算法因其收斂速度快及算法實現簡單等特點在自適應濾波器、自適應天線陣技術等領域得到了十分廣泛的應用。為了發揮算法的最佳性能,必須采用具有大動態范圍及運算精度的浮點運算,而浮點

2023-12-21 16:40:01 228

228

電子發燒友App

電子發燒友App

評論