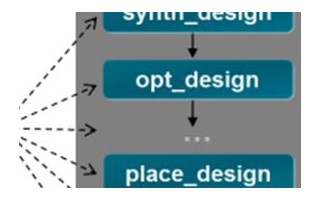

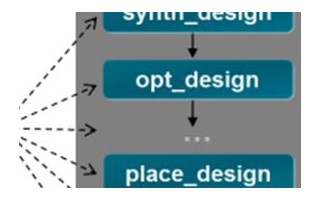

FPGA開發(fā)基本流程包括:設(shè)計(jì)輸入、設(shè)計(jì)仿真、設(shè)計(jì)綜合、布局布線,它們的連接關(guān)系如圖1 所示。

2010-06-10 08:24:15 1687

1687 設(shè)計(jì)人員選擇具有優(yōu)秀調(diào)試能力的FPGA器件,可以縮短開發(fā)周期并降低成本,同時(shí)顯著加快上市速度。

2016-11-10 01:14:11 1617

1617

如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPG

2017-10-24 10:43:09 7183

7183

的事?很可能從來就沒有過。隨著FPGA變得越來越強(qiáng)大,處理的任務(wù)范圍也越來越廣,縮短設(shè)計(jì)周期并且最小化風(fēng)險(xiǎn)變得前所未有的重要。 Pentek公司作為一家商用現(xiàn)貨(COTS)FPGA的數(shù)據(jù)處理和采集產(chǎn)品制造商,通常是FPGA技術(shù)與最終用戶應(yīng)用之間的接口。這使得Pentek處于

2020-12-20 10:04:00 1715

1715 FPGA 的設(shè)計(jì)流程簡(jiǎn)單來講,就是從源代碼到比特流文件的實(shí)現(xiàn)過程。大體上跟 IC 設(shè)計(jì)流程類似,可以分為前端設(shè)計(jì)和后端設(shè)計(jì)。

2023-04-23 09:08:49 1577

1577

藥的研發(fā)周期從數(shù)年縮短至1個(gè)月,研發(fā)成本降低70%。 ? 近段時(shí)間,以ChatGPT為代表的大模型掀起新一輪人工智能熱潮,除了在娛樂、問答聊天、寫程序的應(yīng)用之外,大模型產(chǎn)業(yè)化的應(yīng)用也備受關(guān)注。 ? 2021年4月,華為云盤古大模型正式發(fā)布。

2023-03-31 01:19:00 3514

3514

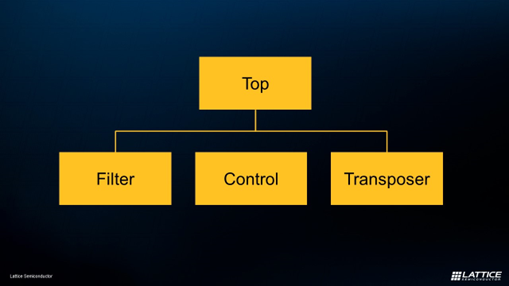

PLL、專用時(shí)鐘沿和I/O gearing邏輯解決了高速串行傳感器接口。最后,萊迪思半導(dǎo)體(Lattice)的 XP2提供了具有成本效益的8×8mm面積。此外,由于其非易失的特性,LatticeXP2系列

2011-05-24 14:17:00

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般如圖1-10所示,包括電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真

2021-07-23 09:12:07

FPGA應(yīng)用設(shè)計(jì)中一種嶄新的硬宏開發(fā)流程是怎樣的

2021-05-06 06:49:19

如圖1.6所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPGA功能的需求分析,然后進(jìn)行模塊的劃分,比較復(fù)雜和龐大的設(shè)計(jì),則會(huì)通過模塊劃分把工作交給一個(gè)

2019-01-28 04:24:37

和萊迪思半導(dǎo)體的Mach XO / ICE40。中端FPGA這些類型的FPGA是低端和高端FPGA之間的最佳解決方案,它們是在性能和成本之間取得平衡而開發(fā)的。中端FPGA的示例是來自Altera

2018-12-14 17:39:44

FPGA的發(fā)展現(xiàn)狀如何?賽靈思推出的領(lǐng)域目標(biāo)設(shè)計(jì)平臺(tái)如何簡(jiǎn)化設(shè)計(jì)、縮短開發(fā)時(shí)間?

2021-04-08 06:18:44

FPGA的圖像傳感器的優(yōu)勢(shì)公司Ing Arndt Bussmann,萊迪思半導(dǎo)體公司圖像采集是安全和監(jiān)控視頻鏈中最關(guān)鍵的部 分,這是因?yàn)閷?duì)于從視頻流提取有效信息的圖像信號(hào)處理能力是與獲取的圖像質(zhì)量

2012-08-11 11:27:45

第二章 FPGA 開發(fā)流程FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

開發(fā)流程FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般如圖2所示,包括電路設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真、板級(jí)

2017-01-10 15:50:15

的一條或多條路徑。在 FPGA 設(shè)計(jì)中主要有四種類型的時(shí)序約束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)約束。賽靈思FPGA設(shè)計(jì)時(shí)序約束指南[hide][/hide]`

2012-03-01 15:08:40

`低功耗的賽靈思 FPGA 系列使總線供電的 USB 器件設(shè)計(jì)垂手可得憑借在市場(chǎng)中數(shù)十億的端口數(shù)量,通用串行總線 (USB) 成為實(shí)現(xiàn)主機(jī)與外設(shè)之間千兆位以下連接的首選接口。不過,由于 USB 規(guī)范

2016-07-27 17:14:50

描述萊迪思HX4K FPGA 突破這款 FPGA 分線板旨在記錄如何開始 FPGA 編程,從硬件設(shè)計(jì)文件到加載比特流。為了嘗試將其作為一個(gè)項(xiàng)目進(jìn)行訪問,該板的一個(gè)設(shè)計(jì)目標(biāo)是使其能夠僅使用烙鐵進(jìn)行手工

2022-08-23 07:21:04

萊迪思半導(dǎo)體公司和SiFive,Inc。最近,他們同意共同合作,通過萊迪思FPGA產(chǎn)品系列(包括最新的28 nm CrossLink-NX?FPGA),為開發(fā)人員輕松提供SiFive可擴(kuò)展核心IP

2020-07-27 17:57:36

(G.8275.2)T-BC、T-TSC C類的ITU定時(shí)特性(G.8273.2)基于萊迪思FPGA的全新開發(fā)平臺(tái)也已添加到萊迪思ORAN方案中。包括了FPGA板和定時(shí)源開發(fā)板的安全定時(shí)和同步套件旨在簡(jiǎn)化新的電信應(yīng)用的測(cè)試、演示和開發(fā)。

2023-03-03 16:52:10

ASIC的設(shè)計(jì)流程是怎樣的?FPGA的開發(fā)流程又是怎樣的?

2021-11-01 07:08:47

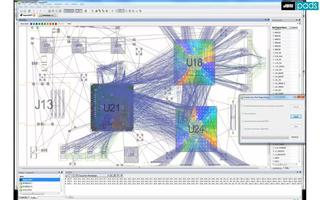

PADS 制造準(zhǔn)備可幫助您優(yōu)化產(chǎn)品質(zhì)量,縮短周期時(shí)間和節(jié)省成本。

2019-05-06 11:01:48

國(guó)產(chǎn)有哪些FPGA入門?萊迪思半導(dǎo)體?高云半導(dǎo)體?

2023-12-05 16:05:38

我們正在開發(fā)基于 imx8mp 處理器的產(chǎn)品。它通過 i2c 總線將程序加載到萊迪思 CrossLink FPGA。FPGA 二進(jìn)制數(shù)據(jù)大小(.ied 文件)為 149KB,使用 400 KHz

2023-05-16 06:28:53

{:1:}推薦一種設(shè)計(jì)流程,它在電機(jī)控制設(shè)計(jì)中利用了 Altera FPGA 強(qiáng)大的適應(yīng)能力、精度可調(diào)數(shù)字信號(hào)處理 (DSP) 以及集成系統(tǒng)設(shè)計(jì)工具。工業(yè)電機(jī)驅(qū)動(dòng)設(shè)備的設(shè)計(jì)人員可

2013-11-14 00:36:28

本帖最后由 廣州虹科_FPGA技術(shù)支持 于 2020-10-29 17:44 編輯

VSTAR是一款輔助FPGA開發(fā)的調(diào)試工具,能夠大幅縮短debug階段的調(diào)試時(shí)間。對(duì)于使用Xilinx

2020-10-29 17:35:56

,FPGA能否在以便攜產(chǎn)品為主體的消費(fèi)電子領(lǐng)域占到一席之地呢?對(duì)于這個(gè)問題,萊迪思半導(dǎo)體公司給出了肯定的答案。

2019-09-03 07:55:28

1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實(shí)現(xiàn)、布線后仿真與驗(yàn)證和下班調(diào)試等步驟。如下圖所示。1)電路設(shè)計(jì)

2021-05-27 09:28:40

,加速產(chǎn)品上市進(jìn)程,大大降低風(fēng)險(xiǎn) 美國(guó)俄勒岡州希爾斯波羅市 — 2015年3月2日 —萊迪思半導(dǎo)體公司(NASDAQ: LSCC)—超低功耗、小尺寸客制化解決方案市場(chǎng)的領(lǐng)導(dǎo)者,今日宣布推出三款可免費(fèi)下載

2019-06-17 05:00:07

前言 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成風(fēng)格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設(shè)計(jì)流程指南本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

的處理器,優(yōu)化了性能和成本通過不同的電壓和各種接口,如SPI、I2C、SDIO、PCI和LPC之間的橋接,最大化組件選擇的靈活性萊迪思FPGALCMXO2-640HC-4TG100C可編程邏輯器件FPGA

2019-09-20 15:13:30

又不足以提供全面的動(dòng)態(tài)保護(hù)和恢復(fù)。萊迪思此次所推出的全面、真正并行、納秒級(jí)響應(yīng)的安全方案可完美解決以上痛點(diǎn),提供動(dòng)態(tài)信任。 安全問題貫穿了設(shè)備整個(gè)生命周期,每一環(huán)節(jié)都至關(guān)重要,尤其固件正逐漸成為常見

2020-09-07 17:16:48

I2C 通道替代其中一個(gè) I2S 接口。”理想的解決方案是采用低成本的現(xiàn)場(chǎng)可編程門陣列(FPGA),如萊迪思半導(dǎo)體的 iCE40 UltraPlus?器件( 圖 3)。圖 3. FPGA 價(jià)格較低且非常

2020-10-22 11:30:53

接口。”理想的解決方案是采用低成本的現(xiàn)場(chǎng)可編程門陣列(FPGA),如萊迪思半導(dǎo)體的 iCE40UltraPlus?器件(圖 3)。圖 3.FPGA 價(jià)格較低且非常靈活使用 FPGA 實(shí)現(xiàn)單線聚合功能

2020-10-23 09:16:56

I2C 通道替代其中一個(gè) I2S 接口。”理想的解決方案是采用低成本的現(xiàn)場(chǎng)可編程門陣列(FPGA),如萊迪思半導(dǎo)體的 iCE40 UltraPlus?器件( 圖 3)。圖 3. FPGA 價(jià)格較低且非常

2021-05-25 14:36:00

的應(yīng)用。采用FPGA技術(shù)構(gòu)造雙口RAM,實(shí)現(xiàn)高速信號(hào)采集系統(tǒng)中的海量數(shù)據(jù)存儲(chǔ)和時(shí)鐘匹配。功能仿真驗(yàn)證該設(shè)計(jì)的正確性,該設(shè)計(jì)能減小電路設(shè)計(jì)的復(fù)雜性,增強(qiáng)設(shè)計(jì)的靈活性和資源的可配置性能,降低設(shè)計(jì)成本,縮短

2010-04-24 09:44:28

位色深)。 萊迪思實(shí)現(xiàn)了同時(shí)支持DVI TX和RX功能的參考設(shè)計(jì)。該設(shè)計(jì)利用了LatticeECP3或LatticeECP2M FPGA系列中的CML SERDES通道,來支持更高速率的DVI傳輸

2019-06-05 05:00:17

本文以FPGA為核心構(gòu)建了一種通用的雷達(dá)回波信號(hào)實(shí)時(shí)模擬系統(tǒng)。該系統(tǒng)采用FPGA作為回波信號(hào)模擬的運(yùn)算單元,充分利用了FPGA資源豐富、并行處理能力強(qiáng)的特點(diǎn),提高了系統(tǒng)的實(shí)時(shí)性;采用System

2021-04-29 06:14:20

本文采用atelra公司的可編程芯片FPGA設(shè)計(jì)了一款周期和輸出個(gè)數(shù)可變的脈沖發(fā)生器。經(jīng)過板級(jí)調(diào)試獲得良好的運(yùn)行效果。

2021-04-29 07:08:33

如何利用STM32F103X的串口對(duì)迪文屏發(fā)送及接收數(shù)據(jù)?

2021-12-06 07:04:09

求助高手,怎樣在labview中獲取周期波形中的一個(gè)周期的數(shù)據(jù),方便后面的計(jì)算,我初步想法是利用matlab和labview結(jié)合使用,利用matlab的圖像處理技術(shù)不知是否可行

2013-07-14 14:37:30

全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司 (Xilinx Inc.) 宣布,為推進(jìn)可編程勢(shì)在必行之必然趨勢(shì),正對(duì)系統(tǒng)工程師在全球發(fā)布賽靈思新一代可編程FPGA平臺(tái)。和前代產(chǎn)品相比,全新的平臺(tái)功耗降低

2019-08-09 07:27:00

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

根據(jù)新的NIST SP 800 193標(biāo)準(zhǔn)、在硬件上使用基于FPGA的可信根器件來實(shí)現(xiàn)平臺(tái)硬件保護(hù)和恢復(fù)(PFR), 可讓服務(wù)器固件免受網(wǎng)絡(luò)攻擊,保護(hù)性能更上一層樓。萊迪思全新PFR開發(fā)工具套件能夠簡(jiǎn)單快速實(shí)現(xiàn)基于FPGA的PFR解決方案。

2019-10-08 09:31:04

按照相對(duì)論的理論,時(shí)間也是可以被拉長(zhǎng)縮短的,只不過需要巨大的能量支撐著您達(dá)到一個(gè)和光速可比擬的高速度而已。這話說著輕松,你我心里都明白,估計(jì)咱們的有生之年是看不到這樣的情景的…… 回到

2019-11-11 07:03:58

來自處理器或其他顯示控制輸出設(shè)備的RGB(紅色,綠色/藍(lán)色)像素總線數(shù)據(jù)。設(shè)計(jì)的輸出連接到D-PHY接口IP內(nèi)核,允許FPGA直接驅(qū)動(dòng)DSI接收設(shè)備,例如顯示器。并行RGB至DSI發(fā)送設(shè)計(jì)說明了萊迪思超低

2020-04-30 07:58:35

和工業(yè)安全等巨大商機(jī)更是鋪天蓋地而來。嵌入式系統(tǒng)作為兵家必爭(zhēng)的灘頭陣地,主控芯片商戰(zhàn)況火熱。 隨著賽靈思、阿爾特拉、萊迪思等一眾 FPGA 全球頂級(jí)大廠攜更高集成度、靈活、延遲小、處理速度快和整體成本

2014-07-22 13:49:58

這正是低功耗FPGA發(fā)揮作用的地方。與增強(qiáng)處理器來處理算法的方式不同,萊迪思iCE40 UltraPlus FPGA可以作為MCU的協(xié)處理器,處理MCU無法解決的復(fù)雜任務(wù)之余,將功耗保持在要求范圍內(nèi)

2020-10-23 11:43:04

我正在使用 i.MX RT 1064 MCU 通過 NXP 的 FlexSPI 控制器通過 Quad SPI 連接到萊迪思 FPGA。FPGA 正在處理我們的外圍設(shè)備并將它從這些設(shè)備獲得的測(cè)量

2023-03-27 06:23:57

了解賽靈思產(chǎn)品的機(jī)會(huì),利用賽靈思FPGA器件,開發(fā)設(shè)計(jì)產(chǎn)品,進(jìn)一步提高FPGA設(shè)計(jì)能力和水平。 大賽參與情況 本次大賽主題是基于賽靈思(xilinx)FPGA芯片進(jìn)行作品設(shè)計(jì)(芯片型號(hào)和應(yīng)用領(lǐng)域不限

2012-09-06 11:52:48

專家進(jìn)行探討交流的機(jī)會(huì),提高對(duì)技術(shù)知識(shí)的應(yīng)用和產(chǎn)品商業(yè)化的認(rèn)知;為廣大電子愛好者深入了解賽靈思產(chǎn)品的機(jī)會(huì),利用賽靈思FPGA器件,開發(fā)設(shè)計(jì)產(chǎn)品,進(jìn)一步提高FPGA設(shè)計(jì)能力和水平。 大賽參與情況

2012-09-06 11:54:16

經(jīng)歷過和牛人一起進(jìn)行FPGA設(shè)計(jì)比賽的激烈競(jìng)爭(zhēng)嗎?你感受過FPGA原廠開發(fā)板和fpga行業(yè)泰斗直接帶來的強(qiáng)烈震撼嗎? 沒經(jīng)歷過沒關(guān)系,電子發(fā)燒友網(wǎng)主辦,賽靈思贊助的“賽靈思FPGA方案開發(fā)設(shè)計(jì)大賽”已經(jīng)為

2012-04-23 09:31:16

只要有數(shù)字電路的基礎(chǔ),還是能較容易和快速地學(xué)會(huì)利用 CPLD/FPGA 設(shè)計(jì)數(shù)字系統(tǒng)的。 數(shù)字系統(tǒng)的基本部件比較簡(jiǎn)單,它們是一些與門、或門、非門、觸發(fā)器和多路選擇器等,宏器件是一些加法器、乘法器等

2019-02-28 11:47:32

本人手中有款LATTICE(萊迪思)100腳的貼片IC ,不知道其型號(hào),底部印著AW44E開頭的,請(qǐng)那位高手指點(diǎn)一下是什么型號(hào)

2014-09-01 23:48:46

。ROHM與安富利公司共同開發(fā)賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評(píng)估套件Mini-Module Plus 用的電源模塊。安富利公司已經(jīng)開發(fā)出多款賽靈思

2018-12-04 10:02:08

1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實(shí)現(xiàn)、布線后仿真與驗(yàn)證和下班調(diào)試等步驟。如下圖所示。1)電路設(shè)計(jì)

2019-05-03 08:00:00

每一版本都提供了完整的FPGA設(shè)計(jì)流程,并且專門針對(duì)特定的用戶群體(工程師)和特定領(lǐng)域的設(shè)計(jì)方法及設(shè)計(jì)環(huán)境要求進(jìn)行了優(yōu)化。那大家知道賽靈思ISE? 設(shè)計(jì)套件11.1版對(duì)FPGA有什么優(yōu)化作用嗎?

2019-07-30 06:52:50

【來源】:《電子設(shè)計(jì)工程》2010年02期【摘要】:<正>賽靈思公司與聯(lián)華電子共同宣布,采用聯(lián)華電子高性能40nm工藝的Virtex-6FPGA,已經(jīng)完全通過生產(chǎn)前的驗(yàn)證

2010-04-24 09:06:05

國(guó)內(nèi)超過100億元的FPGA市場(chǎng)中,國(guó)產(chǎn)市占率僅為4%。目前,全球FPGA市場(chǎng)基本被四大巨頭壟斷:Xilinx(賽靈思)、Intel(英特爾,此前收購了Altera)、Lattice(萊迪思)、Mic...

2021-07-30 06:32:06

。此外,FPGA通常有很寬的溫度范圍,并有很長(zhǎng)的產(chǎn)品生命周期。 針對(duì)ECP2M和ECP3器件系列,萊迪思(Lattice)半導(dǎo)體公司最近推出了DVI/HDMI接口的參考設(shè)計(jì)。萊迪思半導(dǎo)體公司

2019-06-06 05:00:34

章禮宏 范全潤(rùn)1 引言隨著電路規(guī)模不斷擴(kuò)大,以及競(jìng)爭(zhēng)帶來的上市時(shí)間的壓力,越來越多的電路設(shè)計(jì)者開始利用設(shè)計(jì)良好的、經(jīng)反復(fù)驗(yàn)證的電路功能模塊來加快設(shè)計(jì)進(jìn)程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

我們的客戶進(jìn)行創(chuàng)新并加快其設(shè)計(jì)開發(fā)。萊迪思展臺(tái)展示了各類汽車級(jí)解決方案的最新演示,可用于打造基于萊迪思低功耗FPGA技術(shù)的各種車載應(yīng)用。我們與行業(yè)領(lǐng)先的合作伙伴合作,展示了車載信息娛樂、電氣/電子架構(gòu)

2023-02-21 13:40:29

`時(shí)代的發(fā)展衍生出了很多新的產(chǎn)品,近幾年流行于各大高級(jí)商務(wù)酒店、咖啡廳、西餐廳里的LED燈絲燈,在LED燈絲的點(diǎn)膠工藝上也是要求極高的。深圳市阿萊思斯科技有限公司從事全自動(dòng)點(diǎn)膠機(jī)的研發(fā)生產(chǎn)已有10年

2018-07-14 10:09:47

嵌入式IC - FPGA(現(xiàn)場(chǎng)可編程門陣列), 197 I/O 256CABGA

2022-06-16 14:09:08

基于FPGA高速、可編程的優(yōu)點(diǎn),設(shè)計(jì)了一款可以靈活改變脈沖輸出周期和輸出個(gè)數(shù)的周期脈沖發(fā)生器。利用VHDL語言編寫了全部模塊,并在Altera公司提供的QuartusⅡ4.1開發(fā)軟件上實(shí)現(xiàn)了

2010-12-08 15:58:00 52

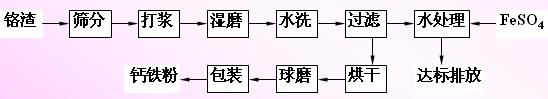

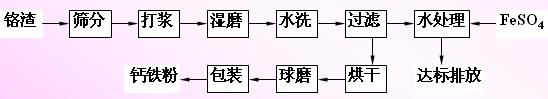

52 利用鉻渣制鈣鐵粉工藝流程

圖 利用鉻渣制鈣鐵粉工藝流程鉻渣制成的鈣鐵粉

2009-03-30 20:13:30 702

702

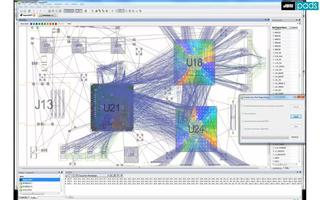

Mentor Graphics的FPGA Advantage是享譽(yù)業(yè)界,具有FPGA設(shè)計(jì)黃金組合的全流程設(shè)計(jì)工具。本次課程將使用戶體驗(yàn)FPGA Advantage如何最大化地加速設(shè)計(jì)的實(shí)現(xiàn)以及復(fù)用。同時(shí)掌握如何利用FPGA Advantage快速實(shí)現(xiàn)設(shè)計(jì)從創(chuàng)建、理解、仿真驗(yàn)證、綜合以及布局布線的全過

2011-03-15 13:39:56 97

97 WP409利用Xilinx FPGA打造出高端比特精度和周期精度浮點(diǎn)DSP算法實(shí)現(xiàn)方案: High-Level Implementation of Bit- and Cycle-Accurate Floating-Point DSP Algorithms with Xilinx FPGAs

2012-01-26 18:03:05 25

25 Alter FPGA的設(shè)計(jì)流程以及DSP設(shè)計(jì).

2012-03-16 15:52:07 127

127 FPGA開發(fā)流程,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:17:27 32

32 FPGA的學(xué)習(xí)流程,有需要的朋友下來看看

2016-05-10 10:46:40 22

22 FPGA設(shè)計(jì)的流程,步驟,選型,仿真,軟硬件設(shè)計(jì),調(diào)試流程。

2016-05-11 14:33:02 29

29 提高FPGA設(shè)計(jì)生產(chǎn)力的工具、技巧和方法,9影響FPGA設(shè)計(jì)周期生產(chǎn)力的最大因素是什么?

2017-02-11 12:22:06 587

587

1. FPGA 開發(fā)流程: 電路設(shè)計(jì)與設(shè)計(jì)輸入 ;仿真驗(yàn)證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10000

10000 不斷 從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì) 1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程 利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15820

15820

本文首先介紹了FPGA發(fā)展由來,其次介紹了FPGA的硬件設(shè)計(jì)技巧及FPGA設(shè)計(jì)者的5項(xiàng)基本功,最后介紹了FPGA設(shè)計(jì)流程及工程師FPGA設(shè)計(jì)心得體會(huì)。

2018-05-31 09:35:06 11241

11241 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載內(nèi)容包括了:1.基于HDL 的FPGA 設(shè)計(jì)流程概述2.Verilog HDL 設(shè)計(jì)3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 29

29 Abhishek Kapoor與X-Microwave首席執(zhí)行官John Richardson共同探討ADI與X-Microwave之間的合作X-Microwave工具和評(píng)估板將縮短設(shè)計(jì)周期時(shí)間,減少使用多個(gè)評(píng)估板。

2019-07-04 06:10:00 2336

2336 在遵循管腳特定的規(guī)則和約束的同時(shí),可以在 PCB 上的多個(gè) FPGA 之間自動(dòng)優(yōu)化信號(hào)管腳分配。減少布線層數(shù),最大限度地減少 PCB 上的交叉數(shù)量并縮短總體走線長(zhǎng)度,以及減少信號(hào)完整性問題,從而提高完成率并縮短 FPGA 的布線時(shí)間。

2019-05-14 06:23:00 3276

3276

Vishay宣布,為了兌現(xiàn)公司支持多層陶瓷片式電容器(MLCC)客戶的承諾,宣布縮短MLCC供貨周期。

2019-07-15 15:37:10 844

844 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-20 15:06:28 1545

1545 最新才流行的嵌入式C程序。 FPGA的開發(fā)流程即是利用EDA開發(fā)軟件以及編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。EDA ( Electronic Design Automation,電子設(shè)計(jì)自動(dòng)化

2020-11-12 18:22:28 5791

5791 FPGA設(shè)計(jì)流程指南

2021-11-02 16:29:21 9

9 第二章 FPGA 開發(fā)流程FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過程。原理圖和HDL(Hardware description language,硬件

2021-12-29 19:40:15 9

9 FPGA 的設(shè)計(jì)流程就是利用 EDA 開發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過程。原理圖和HDL(Hardware description language,硬件描述語言)是兩種最常用的數(shù)字

2023-03-21 10:26:50 2624

2624 FPGA的設(shè)計(jì)流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態(tài)時(shí)序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計(jì)的流程圖。

2023-07-04 12:06:08 795

795

??FPGA 的詳細(xì)開發(fā)流程就是利用 EDA 開發(fā)工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過程,所以 FPGA 芯片開發(fā)流程講的并不是芯片的制造流程,區(qū)分于 IC 設(shè)計(jì)制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 2387

2387

根據(jù)瑞銀分析師最近提供給投資者的備忘錄,英偉達(dá)已經(jīng)顯著縮短了其AI GPU的交付周期。這一周期已經(jīng)從去年年底的8-11個(gè)月迅速縮短至目前的3-4個(gè)月。這一變化引發(fā)了市場(chǎng)的廣泛關(guān)注,分析師們普遍認(rèn)為這背后有兩種可能的原因。

2024-02-18 17:31:09 451

451 電子發(fā)燒友網(wǎng)站提供《FPGA的PL端固化流程.pdf》資料免費(fèi)下載

2024-03-07 14:48:58 0

0 FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場(chǎng)可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論