在數(shù)字IC設(shè)計中,重要的ASIC設(shè)計約束分為兩類,主要是:

1.優(yōu)化約束

2.設(shè)計規(guī)則約束(DRC)

根據(jù)ASIC邏輯設(shè)計,優(yōu)化的約束是速度和面積。在物理設(shè)計中,我們需要對面積、速度和功率進行優(yōu)化設(shè)計。根據(jù)所需的技術(shù)節(jié)點和策略進行更好的功耗規(guī)劃,總是有助于獲得芯片的布局。

DRC是晶圓鑄造規(guī)則,主要是傳輸、扇出和容量。

約束可用于在邏輯和物理綜合的各個綜合階段優(yōu)化設(shè)計。

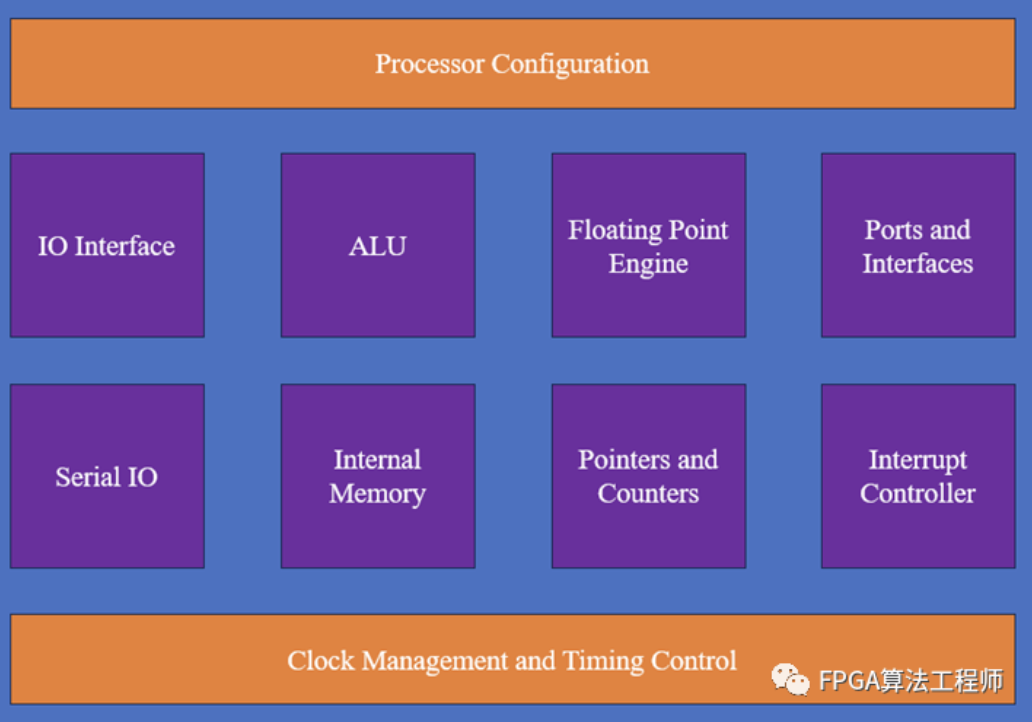

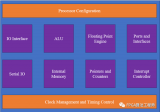

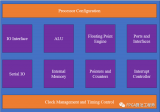

這些約束在設(shè)計的模塊、頂層和芯片級別。例如考慮如圖所示的處理器架構(gòu),可以為各種功能塊指定塊級約束,這些功能塊包括ALU、浮點引擎、高速接口等。頂層約束將在綜合過程中使用,它們用于集成所有功能塊。

處理器頂層架構(gòu)

如果滿足模塊級約束,并不意味著設(shè)計將滿足頂層約束。在物理設(shè)計期間,需要滿足干凈布局的芯片級約束。

對于處理器的綜合,以下可能是較好的策略:

- 為不同的時鐘組執(zhí)行綜合。

- 使用自底向上的綜合并提取模塊級約束。

- 在模塊級綜合過程中優(yōu)化設(shè)計,以滿足面積和速度的要求。

- 指定頂層約束。

- 執(zhí)行頂層綜合并優(yōu)化設(shè)計以滿足頂層約束。

- 如果不滿足約束條件,則使用策略來調(diào)整RTL架構(gòu)。

1. 重要設(shè)計概念

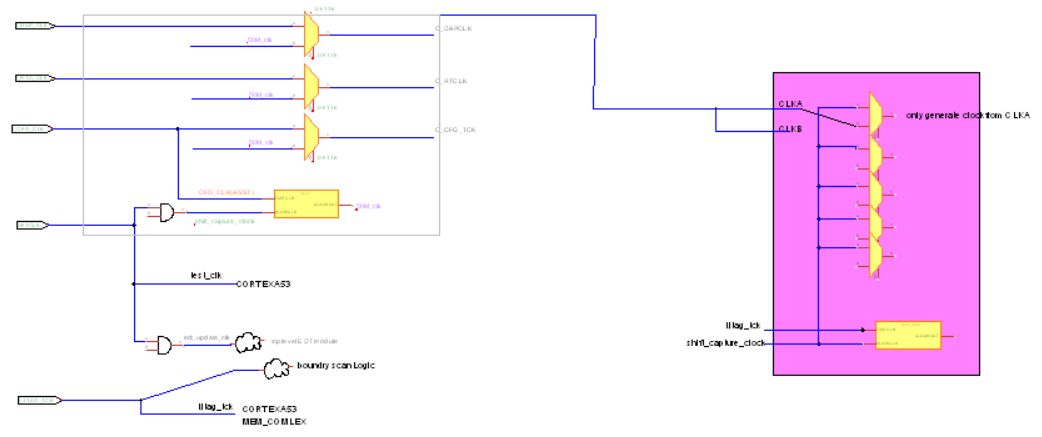

1.1 時鐘樹

時鐘樹綜合是在物理設(shè)計流程中進行的,而在邏輯設(shè)計流程中我們沒有時鐘分布的信息。也就是說,我們將嘗試使用具有可用統(tǒng)計數(shù)據(jù)的Synopsys DC設(shè)置來指定時鐘和時鐘延遲。

1.2復位樹

具有多個功能塊初始化復位的設(shè)計需要與主復位同步。如果復位是在時鐘的有效邊緣期間產(chǎn)生的,則復位樹可用于避免亞穩(wěn)態(tài)輸出。

要考慮的重要參數(shù)是:

1.復位恢復時間

2.復位移除時間

1.3 時鐘和復位策略

在邏輯設(shè)計過程中,以下策略可能會對復位和時鐘有所幫助。

1.對于多個時鐘域,在數(shù)據(jù)和控制路徑中使用同步器。

2.使用統(tǒng)計數(shù)據(jù)來引入時鐘延遲,并指定邏輯綜合過程中的設(shè)置和保持不確定性。

3.在邏輯設(shè)計期間手動實例化時鐘。

4.使用復位同步器將復位與主復位同步。

1.4 影響設(shè)計性能的是什么?

ASIC設(shè)計應(yīng)滿足速度和面積的優(yōu)化約束。我們將在物理設(shè)計期間使用功率限制和DRC。以下是在綜合過程中需要解決的要點:

- 模塊級約束 :對于復雜的ASIC設(shè)計,如果我們考慮多個功能塊或IP,那么應(yīng)該指定塊級約束。功能塊的塊級約束應(yīng)該滿足。例如,處理器邏輯工作在250MHz的工作頻率,但整個芯片工作在500MHz。在這種情況下,與頂層約束相比,設(shè)置和保持的總體不確定性是不同的。因此,應(yīng)該在塊級綜合期間使用塊級Tcl腳本。

- 頂層約束 :在完成所有功能塊的綜合后,對于自底向上的綜合,進行頂層集成。需要為特定的時鐘組指定頂層約束,主要在Tcl腳本中,應(yīng)該使用以下命令:

(a)時延信息

(b)輸入時延

(c)輸出時延

(d)setup不確定性

(e)hold不確定性

如果滿足模塊級約束,但不能保證滿足頂層約束。可能原因是這樣的:

1. 如果設(shè)計分區(qū)不在順序邊界上,則會產(chǎn)生額外的延遲。

2. 數(shù)據(jù)到達速度快,且設(shè)計中存在缺陷。

3. 數(shù)據(jù)到達緩慢,并且設(shè)計存在設(shè)置沖突。

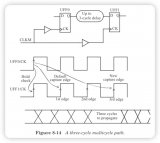

4. 如果在綜合過程中,由于多循環(huán)和假路徑,會出現(xiàn)定時異常。

5. 由于同步策略不佳導致數(shù)據(jù)完整性降低。

6. 如果設(shè)計有層次結(jié)構(gòu),并且DC不能優(yōu)化粘合邏輯。在這種情況下,設(shè)計需要扁平化以提高優(yōu)化。

2. 約束說明

需要為Verilog文件指定的模塊和頂層綜合的重要約束是面積、速度和功率。讓我們排除功率,因為功率優(yōu)化不是使用DC進行的。作為一名設(shè)計師和綜合團隊成員,我們的目標是對設(shè)計有功能性的理解,以及對設(shè)計的整體面積和速度要求。

2.1 面積約束

在邏輯綜合期間,該區(qū)域是由于使用的邏輯和宏。標準單元信息在庫中可用,并且需要特定的宏來實現(xiàn)設(shè)計的低級抽象。整體面積優(yōu)化可以在過程中進行:

- RTL設(shè)計 :使用資源共享、資源分配、消除死區(qū)、使用括號和摸索等概念。

- 綜合 :通過使用工具指定的命令和使用區(qū)域優(yōu)化命令,可以優(yōu)化區(qū)域。

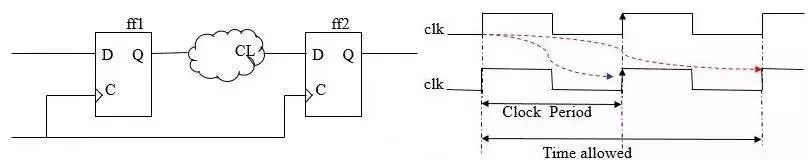

2.2 速度約束

速度是特別重要的因素,因為它決定了設(shè)計的整體性能。設(shè)計的速度約束需要根據(jù)特定技術(shù)節(jié)點的庫中可用的統(tǒng)計數(shù)據(jù)來制定,并且要滿足這些約束。由于實際的布局布線在邏輯綜合期間不可用,因此目標是仔細查看以消除塊和頂層設(shè)計的設(shè)置沖突。綜合和STA團隊需要指定以下內(nèi)容:

1. 時鐘

2. 時鐘延遲

3. 建立并保持不確定性

4. 輸入和輸出最大和最小延遲

5. 選擇多周期路徑

6. 指定偽路徑

2.3 功率約束

功率是另一個約束條件,在功率規(guī)劃中,我們將約束條件指定為漏電和動態(tài)功率。為了實現(xiàn)低功耗感知架構(gòu)和設(shè)計,我們將在各個設(shè)計階段使用統(tǒng)一功率格式(UPF)。以下是一些優(yōu)化功率的策略:

- 架構(gòu)設(shè)計 :具有低功耗架構(gòu)設(shè)計,具有上電順序和電源關(guān)閉策略。

- 使用低功率單元 :在設(shè)計過程中使用低功率單元,但設(shè)計師需要更好地了解單元的特性,因為這些單元的使用對設(shè)計速度有重大影響。

- RTL設(shè)計 :在RTL設(shè)計中,使用時鐘門控單元來降低動態(tài)功率。

3. 設(shè)計中的問題

以下是ASIC綜合過程中的重要挑戰(zhàn):

1. 邏輯的修改。

2. 未連接的端口和網(wǎng)絡(luò)滿足了模塊級速度限制,但在頂層設(shè)計上失敗了。

3. 雖然RTL驗證成功,但設(shè)計的模塊級連接存在缺失。

4. 綜合期間的重要SDC命令

本節(jié)討論在綜合過程中使用的重要DC命令,這些命令對于指定約束很有用。

4.1 Synopsys DC命令

在ASIC綜合過程中使用的一些SDC命令記錄在本節(jié)中。

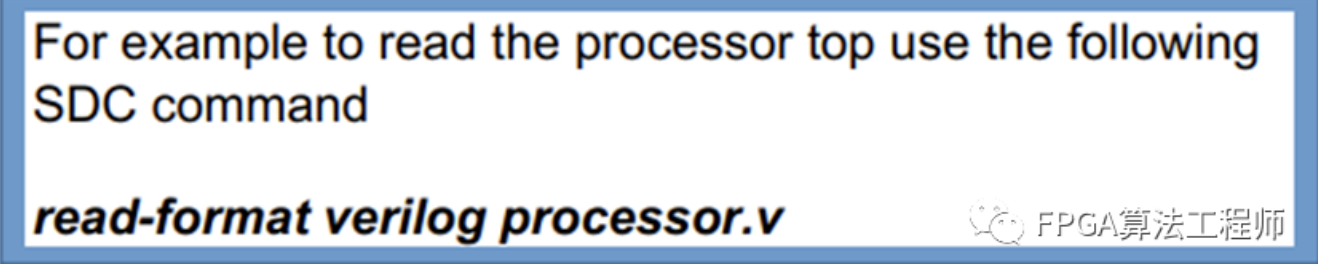

1.Reading the design(讀取設(shè)計)

以上命令用于讀取設(shè)計。

2. Analyze the design(分析設(shè)計)

**analyze –format < format_type > **

用于分析設(shè)計。它用于報告語法錯誤,并在擁有通用邏輯之前執(zhí)行設(shè)計轉(zhuǎn)換。通用邏輯是synopsys通用技術(shù)獨立庫的一部分。這些組件被命名為GTECH。這個邏輯是布爾函數(shù)的未映射表示。

3. Elaborate the design(細化設(shè)計)

**elaborate –format < format_type > **

用于細化設(shè)計,并可用于在細化過程中為相同的分析設(shè)計指定不同的架構(gòu)。

重要的是要了解Read、Analyze和Elaborate命令的區(qū)別。以下是關(guān)鍵點:

1. 在進行細化設(shè)計的同時,通過分析和細化來傳遞所需的參數(shù)。

2. 在輸入DC中預編譯的設(shè)計或網(wǎng)絡(luò)列表時使用讀取。

3. 使用analyze和elaboration命令,可以在精化過程中為相同的分析設(shè)計指定不同的架構(gòu)。

4. read命令不允許使用不同的架構(gòu)。

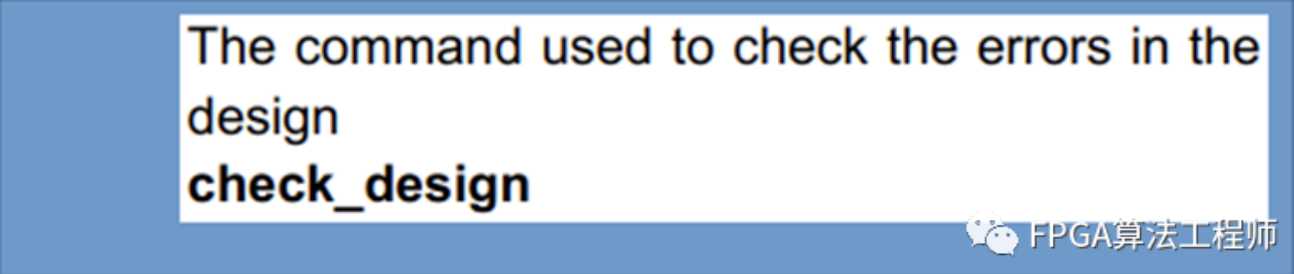

4.2 設(shè)計檢查

在使用DC讀取設(shè)計之后,使用check_design來檢查設(shè)計問題,如短路、斷路、多個連接、實例化和無連接。

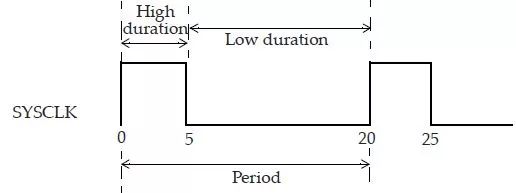

4.3 clock定義

需要使用命令create_clock指定時鐘,并且在時序分析期間將其用作參考時鐘。使用create_clock命令定義時鐘的示例如下。

**create_clock–name -period **

該命令用于為設(shè)計創(chuàng)建時鐘,作為時序分析時的參考時鐘。如果設(shè)計沒有時鐘,那么它將被視為虛擬時鐘。

時鐘有不同的占空比

如果設(shè)計者希望使用具有0.5 ns上升沿和2 ns時鐘周期的可變占空比時鐘,則create_clock命令可以修改為

create_clock –name clock - period 2 –waveform {0.5,2} –name processor_clock

虛擬時鐘

如果設(shè)計沒有時鐘引腳,則使用以下命令創(chuàng)建虛擬時鐘。

下列命令生成頻率為500mhz,占空比為50%的虛擬時鐘。

create_clock –name clock -period 2

下列命令生成頻率為500mhz的虛擬時鐘,具有可變占空比,上升沿為0.5 ns,下降沿為2 ns。

create_clock –name clock -period 5 –waveform {0.5,2}

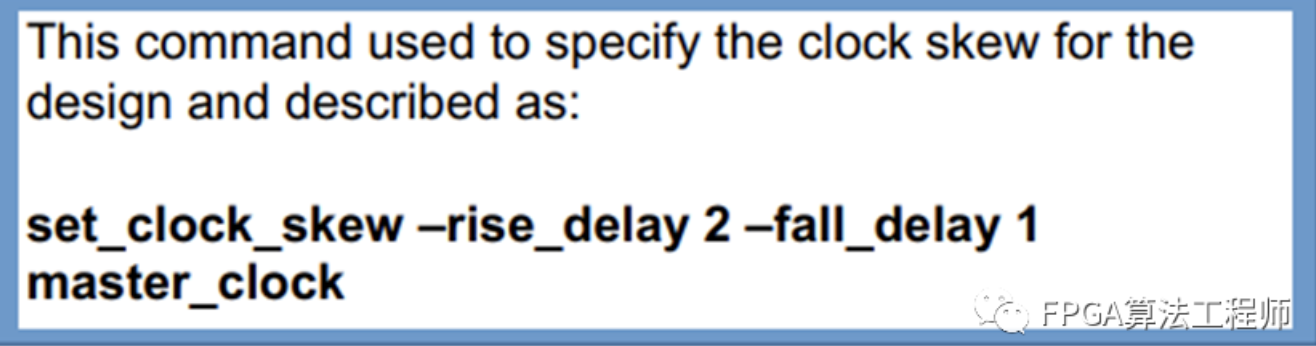

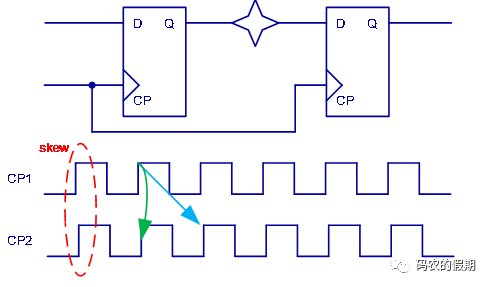

4.4 skew定義

正如前面的文章所討論的,偏差是時鐘信號到達之間的差異。如果源觸發(fā)器的時鐘相對于目標觸發(fā)器延遲,則該偏差稱為負時鐘偏差,對hold有用。如果與源觸發(fā)器相比,目標觸發(fā)器的時鐘延遲,則該偏差稱為正時鐘偏差,對setup很有用。原因是目標觸發(fā)器的時鐘延遲,數(shù)據(jù)可能由于偏差而延遲到達。

設(shè)計編譯器將無法綜合時鐘樹,所以為了克服這個問題,時鐘傾斜是用來指定延遲的!

下列命令由設(shè)計編譯器用于指定設(shè)計的時鐘傾斜

**set_clock_skew –rise_delay -fall_delay **

4.5 Input /output delay 定義

可以分別使用set_input_delay和set_output_delay命令指定輸入和輸出延遲。用于指定輸入和輸出延遲的命令如下所示。

**set_input_delay –clock **

用于定義輸入延遲。

**set_output_delay –clock **

用于定義輸出延遲。

4.6 指定min/max delay

輸入和輸出延遲可以根據(jù)設(shè)計需要指定為最小或最大。

Maximum Input Delay

**set_input_delay –clock -max **

用于定義最大輸入延遲。

Minimum Input Delay

**set_input_delay –clock -min **

用于定義最小輸入延遲。

**set_output_delay –clock -max **

用于定義最大輸出延遲。

Minimum Output Delay

**set_output_delay –clock -min **

用于定義最小輸出延遲。

4.7 設(shè)計綜合

compile命令用于執(zhí)行設(shè)計綜合。如前一節(jié)所討論的,我們需要將設(shè)計約束、庫和Verilog文件作為綜合工具的輸入。設(shè)計綜合可以使用不同的努力水平(如低、中、高)來執(zhí)行。

編譯命令指定為:

**compile –map_effort **

4.8 保存設(shè)計

write命令用于保存設(shè)計。設(shè)計人員可以將綜合輸出保存為Verilog (.v)或數(shù)據(jù)庫(.ddc)格式。該命令可以如下所示指定:

**write –format -output **

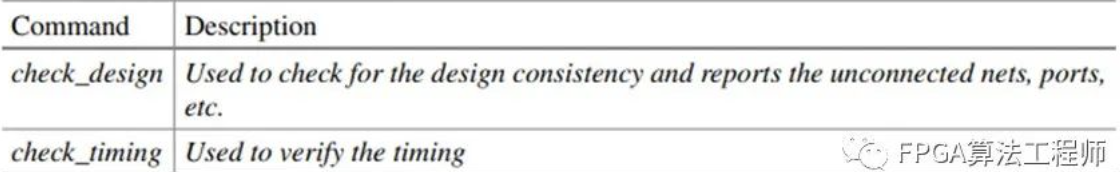

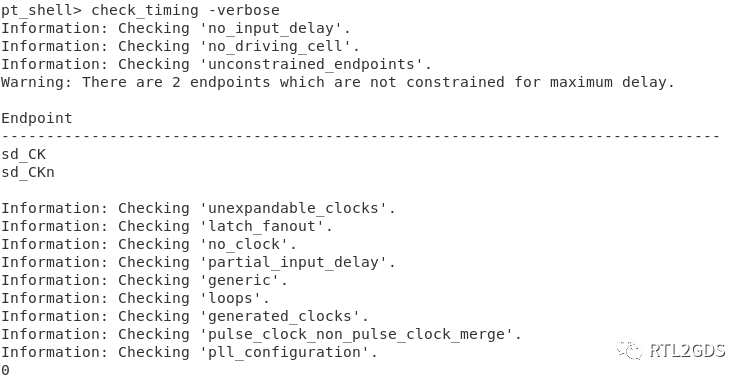

5. 約束驗證

下表列出了用于驗證設(shè)計的重要命令。

6. DRC、功率和優(yōu)化約束

下表列出了用于指定設(shè)計規(guī)則、功率和優(yōu)化約束的重要命令。

7. 本文總結(jié)

總結(jié)本文的要點:

- 設(shè)計約束包括優(yōu)化約束和設(shè)計規(guī)則約束。

- 綜合是從較高層得到較低層設(shè)計抽象的過程。

- 綜合工具使用Verilog文件、庫和約束作為輸入。

- 綜合工具的輸出是門級網(wǎng)表。

- 模塊級和頂層設(shè)計的約束應(yīng)該記錄在單獨的Tcl文件中。

- Synopsys DC沒有針對功率進行優(yōu)化。

- 在邏輯綜合過程中,目標是優(yōu)化設(shè)計的面積和速度。

電子發(fā)燒友App

電子發(fā)燒友App

評論