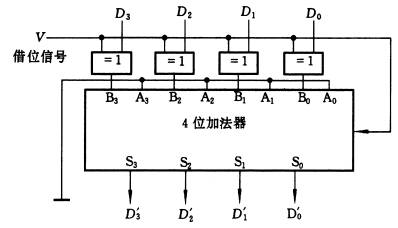

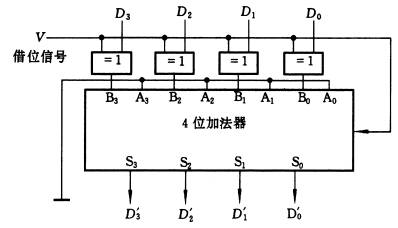

多位二進制減法器,是由加法電路構成的;在加法電路的基礎上,減法與加法采用同一套電路,實現加減法共用。

2020-09-01 16:02:09 20233

20233

運算放大器之所以被稱為運算放大器,沒有叫A放大器或者B放大器,那是因為這種結構可以做運算,比如積分,微分,加法,減法呀等等。

2022-07-13 14:16:14 4389

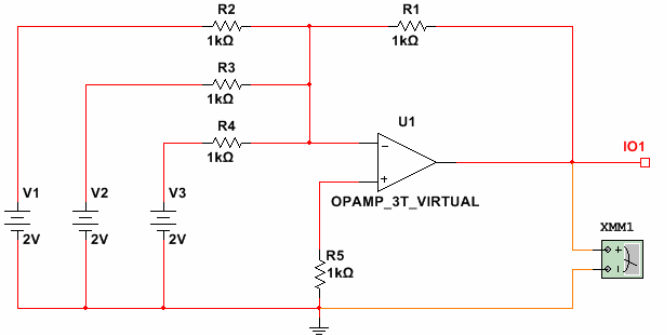

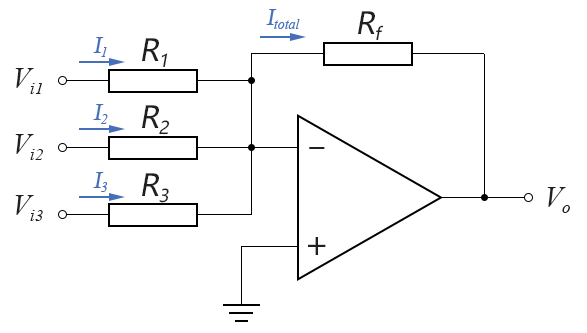

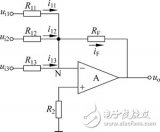

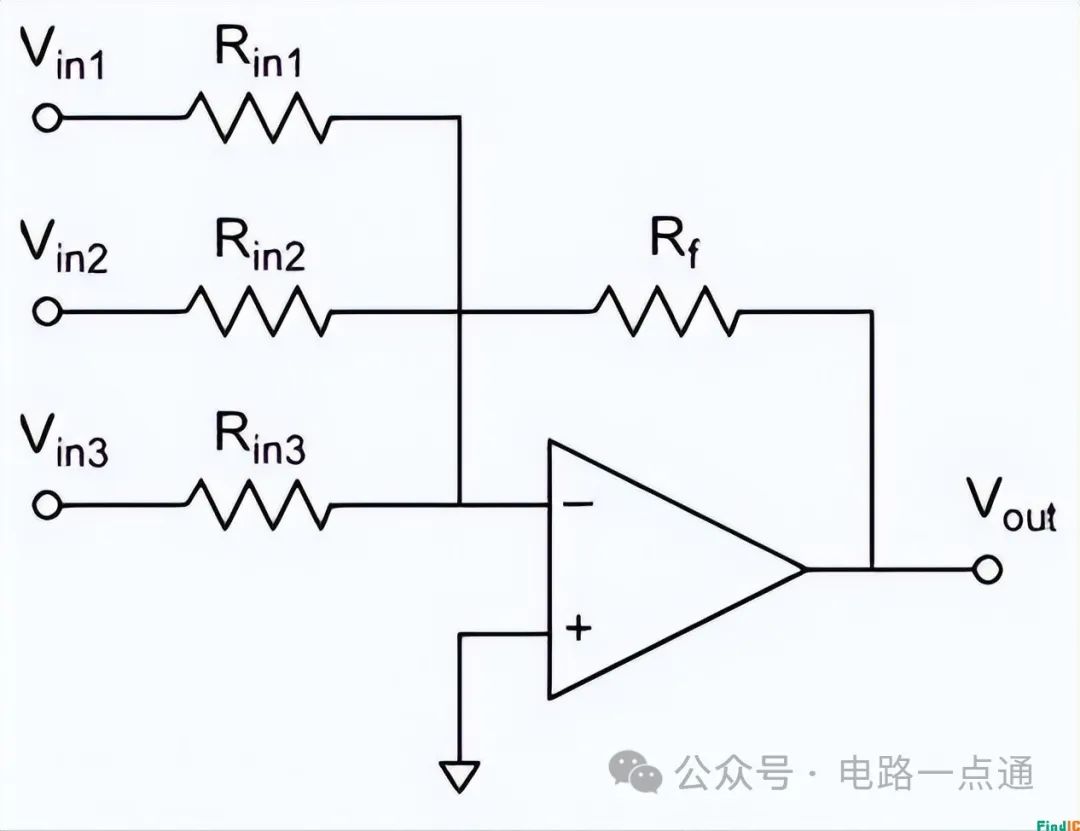

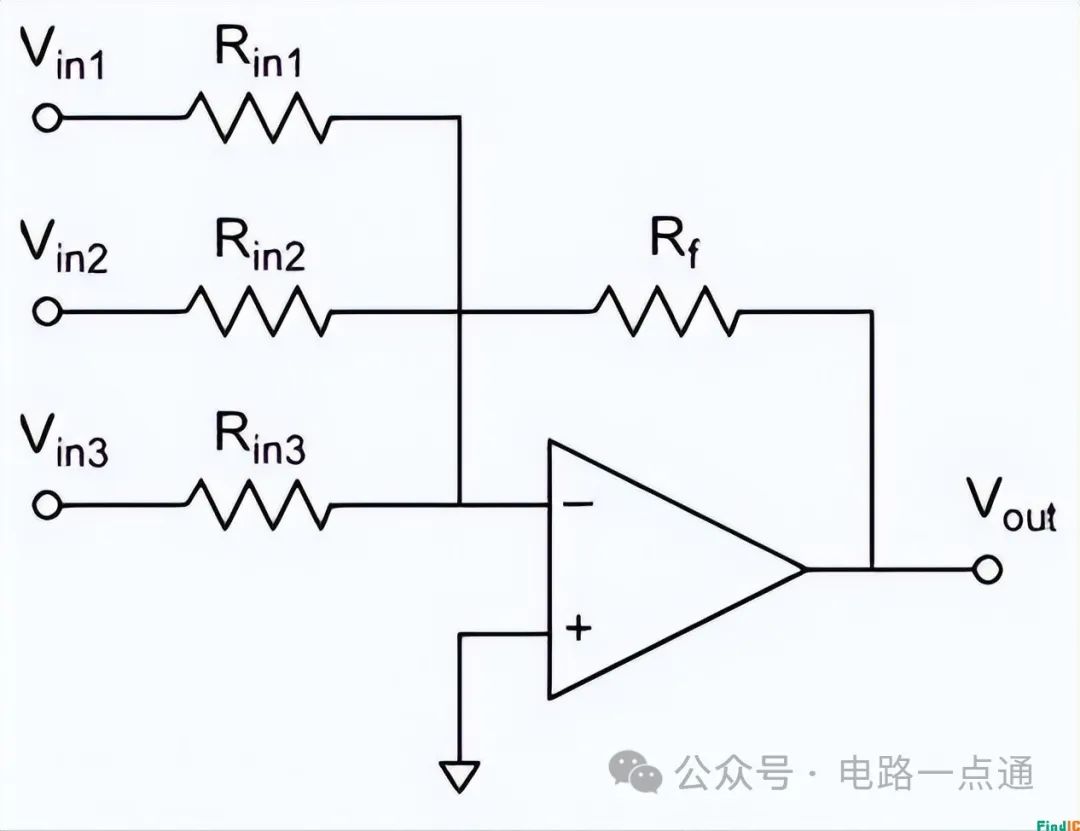

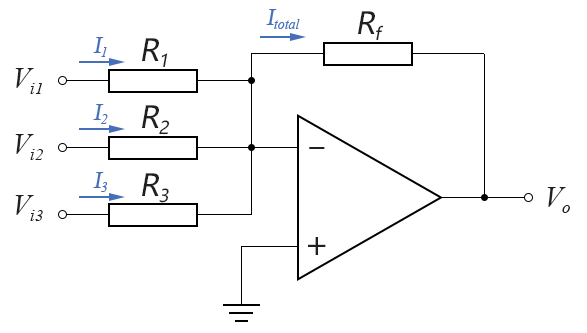

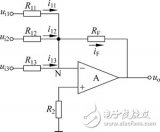

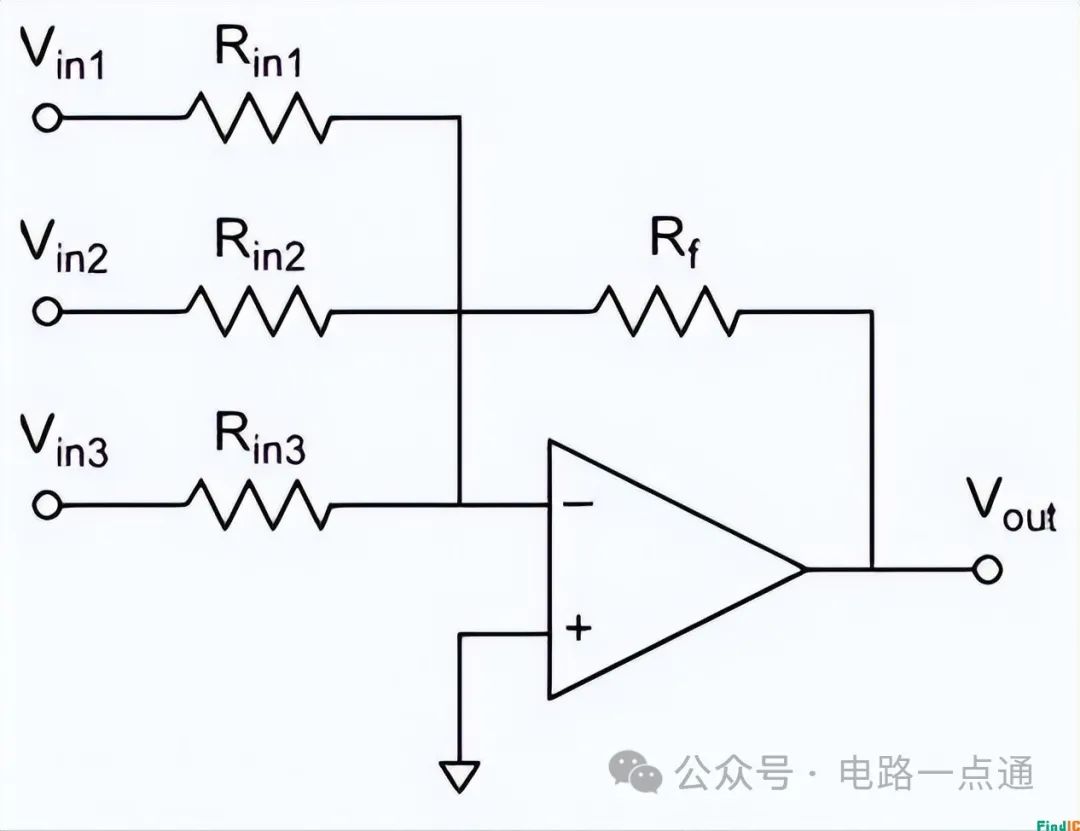

4389 運算放大器構成加法器 可以分為同相加法器和反相加法器

2022-08-05 17:17:38 22398

22398

理想運算放大器特性如下:(1)開環增益 Aud=∞;(2)輸入阻抗 Ri = ∞;(3)輸出阻抗 Ro = 0;(4)帶寬Fbw = ∞;(5) 失調與漂移為零。

2022-09-06 16:40:44 12407

12407

前面的反相放大器和同相放大器可以實現乘法運算的功能,這一小節我們來看如何用運放實現加減法運算。

2023-02-02 14:12:24 22816

22816

可看出輸出值與輸入值的和成反比關系,所以叫反相加法運算電路。

2023-08-08 15:41:56 3817

3817

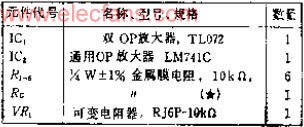

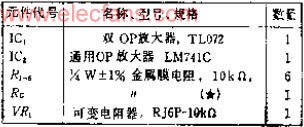

掌握用集成運算放大器組成的比例、加法、減法、積分等運算電路的性能及其測試方法。

2023-10-10 16:23:22 3558

3558

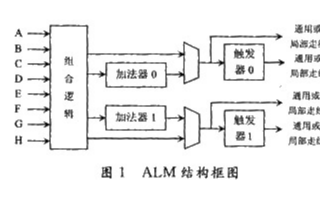

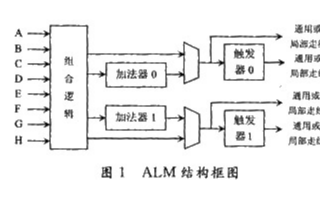

大規模的整數加法在數字信號處理和圖像視頻處理領域應用很多,其對資源消耗很多,如何能依據FPGA物理結構特點來有效降低加法樹的資源和改善其時序特征是非常有意義的。

2023-11-08 09:06:32 636

636

減法器是一種電路,它可以實現二進制數字的減法運算。減法器的工作原理基于位運算和進位/借位機制。

2024-02-19 09:36:37 563

563

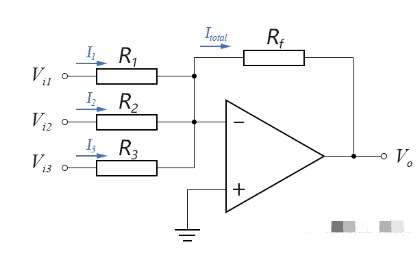

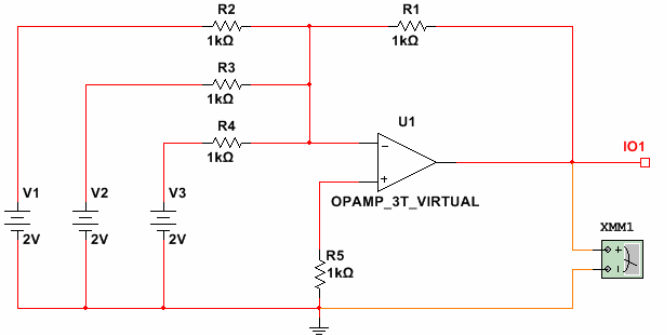

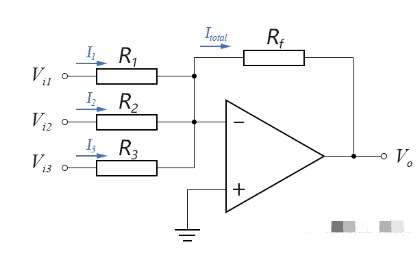

加法運算的電路如下圖所示,輸出電壓為若干個輸入電壓的比例和

2024-02-19 09:52:06 713

713

減法電路是基本集成運放電路的一種,算術運算電路主要包括數字**加法器電路、數字減法器電路、數字乘法器電路和數字除法器電路。

2024-02-19 10:00:17 311

311

如何用multisim軟件仿真雙時鐘加/減計數器CT74LS192和譯碼器CC4511和譯碼器SM4205構成的30進制加法計數器和30進制減法計數器,求仿真接線圖。PCB打樣找華強 http://www.hqpcb.com/3 樣板2天出貨

2012-10-07 21:13:28

前段時間動手做了個小項目,跟大家分享一下!可實現4位帶進位加法/減法計算。目前負值無法顯示,只顯示負數絕對值。對實例1中的顯示部分有優化。目前已實現計算器功能,但程序有待優化。遙控板測試說明(紅外):—:表示減法+: 表示加法EQ:表示計算/等于

2015-01-20 17:15:24

剛學匯編看加法有點糊涂求個最簡單的加法匯編程序像直接寫36+37=73 這樣直接運算的并且可以在數碼管顯示的 最好有注釋新手求看懂

2013-04-20 04:02:18

,51單片機處理浮點數會浪費大量時間。2、本例使用單片機的P0口和P1口分別顯示兩個無符號字符型數據的加法和減法的運算結果3、在kei c51中新建工程文件ex6,輸入如下的程序代碼,編譯并生成

2012-03-21 16:55:33

在FPGA中一般減法是怎么處理的呢?比如A-B是采用A+B的補碼,還把A和B都定義成有符號的類型,直接進行減法運算呢?

2014-12-24 09:46:57

/ C51中的復合賦值運算符 /變量 復合運算符 表達式先把變量與后邊的表達式進行某種運算,然后將運算的結果賦給前面的變量。+= 加法賦值 ?+ 減法賦值*= 乘法賦值 /= 除法賦值%= 取模賦值 &= 邏輯與賦值|= 邏輯或賦值 ~=邏輯非賦值 >>= 右移位賦值

2021-12-07 08:09:34

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-17 08:10:29

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-10 07:04:46

嗨,我正在盡可能使用壓縮邏輯來執行加法或減法。我有兩個8位數據,我想有時添加或有時減去這兩個數字。它看起來像是Elelment有一個叫做“CYINIT”的輸入,根據它的值,它可以執行加法或減法。我

2019-03-28 06:07:39

請教大家怎么用VHDL語言實現減法運算?在FPGA設計時又該怎么操作呢?

2012-05-17 20:07:12

Windows -編程-數值運算Rust 支持所有數字類型的基本數學運算:加法、減法、乘法、除法和余數。以下代碼顯示了如何在let語句中使用每一個:誠接Windows驅動開發外包文件名:src

2021-08-24 14:36:35

20以內加減法訓練機基于單片機實現 20 以內整數加減法訓練,要求具有加法、減法(結果不出現負數)、加減法三種訓練模式,每次訓練隨機產生題目。可以選擇每次訓練題目的數目,可分為每組 5 題、10 題

2021-07-15 07:51:35

matlab 矩陣運算矩陣運算MATLAB對矩陣的運算包括算術運算,關系運算和邏輯運算。算術矩陣運算矩陣的基本算術運算(當然標量是矩陣的特殊情況)有:+ 加法- 減法* 乘法/ 右除\ 左除^ 取冪

2009-09-22 15:32:42

處理等方面受到了限制,由于FPGA中關于浮點數的運算只能自行設計,因此,研究浮點加法運算的FPGA實現方法很有必要。

2019-07-05 06:21:42

第21章 DSP矩陣運算-加法,減法和逆矩陣本期教程主要講解矩陣運算中的初始化,加法,逆矩陣和減法。目錄第21章 DSP矩陣運算-加法,減法和逆矩陣21.1 初學者重要提示21.2 DSP基礎運算

2021-08-17 07:11:32

處理等方面受到了限制,為什么研究浮點加法運算的FPGA實現方法很有必要? 因為FPGA中關于浮點數的運算只能自行設計 。

2019-08-15 08:00:45

為通用計算機的算法單元,本文特別關注嵌入式系統的實踐。在介紹章之后,該出版物分為兩部分。第一部分,數學方面和算法,包括數學背景,數字表示,加法和減法,乘法,除法,其他算術運算和有限域中的操作。第二部分,算法

2018-12-20 16:14:53

fpga:Spartan-6 xc6slx150-3fgg484我在資源密集型處理系統中使用了幾百個8位加法器,因此資源使用很重要。用于加法器減法器的核心生成器為具有2個8位輸入和8位輸出,0延遲

2019-04-03 15:55:35

介紹一種在FPGA上實現的單精度浮點加法運算器,運算器算法的實現考慮了FPGA器件本身的特點,算法處理流程的拆分和模塊的拆分,便于流水設計的實現。

2021-04-29 06:27:09

的加法樹里我們定義的是將兩個電路對象相加,當然你也可以用來實現其他的方法,只要符合op方法定義即可。levelBridge: (T, Int) => T 樹層級間的調用方法,該方法依賴兩個

2022-08-01 14:29:09

矩陣運算中的初始化/加法/逆矩陣和減法,看完你就懂了

2021-11-19 07:02:39

一:算術運算符算術運算符非常地簡單,就是小學數學里面的一些加減乘除操作。不過呢,還是有一些語法細節需要注意的。1.加法運算符 + 1 在第3行利用加法運算符 + 進行了加法運算,再將和賦值給了變量b

2021-11-30 06:09:47

FPGA如何實現32位減法運算

2019-02-28 04:59:09

運算放大器一般是用來做反向放大用嗎?除了做這個放大之外,它做加法與減法、積分運算的場合多不多?

2019-05-16 06:08:44

hValue = (u16)(-Theta);hValue = 0x166-hValue;//我想在這一步實現減法運算,但是使用ST-link 進行仿真的時候發現,hValue 的值并沒有發生變化?請教大家一下,在STM32中,如何實現減法運算呢?

2019-01-17 01:04:46

請問一下高速流水線浮點加法器的FPGA怎么實現?

2021-05-07 06:44:26

8位單片機能夠實現超長數計算嗎?我說:"只要存儲器夠大,按照下面的方法設計的加減法運算器及指令,就能夠編寫程序完成。"1。用全加器搭建一個8位加法器;2。將最低下進位前連接一個1位寄存器,輸入端連接

2014-09-22 03:09:55

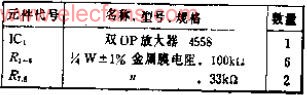

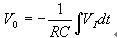

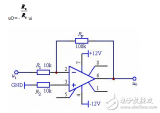

集成運算放大電路實驗實驗目的1. 了解集成運算放大器的特點。2. 掌握集成運算放大器在信號運算方面的應用。實驗原理集成運算放大器按照輸入方式可以分為同相、反相、差分三種接法,按照輸入電壓與輸出電壓的運算關系可以分為比例、加法、減法、積分、微分等,輸入方式和運算關系組合起來,可以構成各種運算放大器。

2008-12-11 23:27:49

集成運算放大電路實驗實驗目的1. 了解集成運算放大器的特點。2. 掌握集成運算放大器在信號運算方面的應用。實驗原理集成運算放大器按照輸入方式可以分為同相、反相、差分三種接法,按照輸入電壓與輸出電壓的運算關系可以分為比例、加法、減法、積分、微分等,輸入方式和運算關系組合起來,可以構成各種運算放大器。

2008-09-22 12:18:59

。二、框圖三、加減乘除加法:因為FPGA硬件資源里有加法器,所以我們就直接用加了。減法:我們都知道二進制數的負數就是它的補碼,所以A減B就可以寫成加法的形式乘法:首先,判斷操作數B(乘數)是否為零,不為

2016-09-01 09:03:33

介紹了用VHDL 語言在硬件芯片上實現浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產品為硬件平臺,以Maxplus II 為軟件工具,實現了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

37 集成運算放大器是一種高增益的直流放大器。它有兩個輸入端,一個輸出端。外接負反饋電路后能夠完成反相比例,同相比例,加法、減法、乘法,微分、積分等運算功能。現

2008-09-24 22:07:42 18609

18609

加法運算放大器電路包含有

2008-09-27 17:33:18 27291

27291

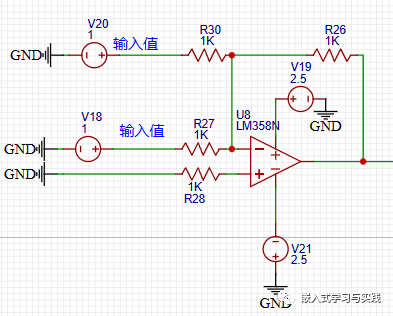

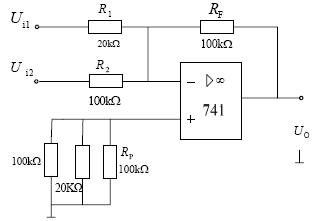

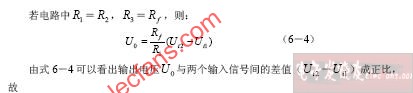

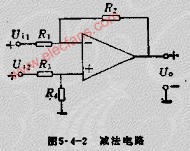

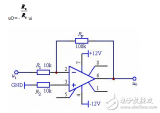

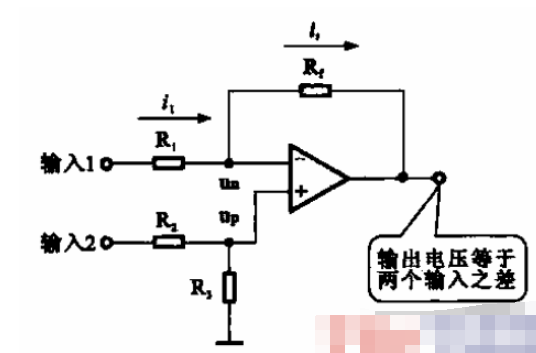

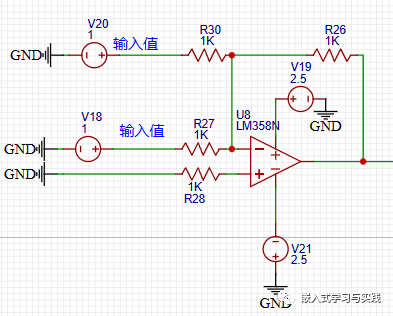

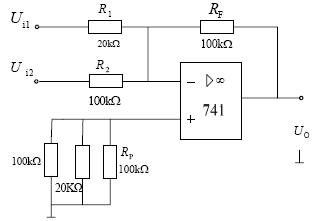

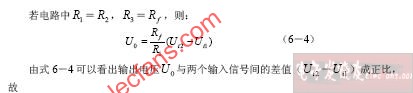

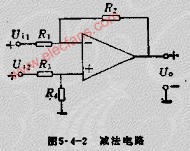

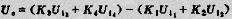

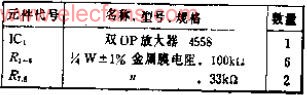

減法運算電路

圖6-4 減法運算電路

2009-03-09 10:11:43 5254

5254

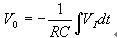

減法運算

同加法運算一樣,減法運算可采用減法器來實現。半減器和全減器的設計方法和步驟與設計加法器相同。實用上,為了簡化系統結構,通常不另外設計減

2009-04-07 10:38:39 12841

12841

高速流水線浮點加法器的FPGA實現

0 引言現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操

2010-02-04 10:50:23 2042

2042

本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸

2010-04-13 11:11:55 5132

5132 多功能算術/邏輯運算單元(ALU) ,什么是多功能算術/邏輯運算單元(ALU)

由一位全加器(FA)構成的行波進位加法器,它可以實現補碼數的加法運算和減法運算。但是這種加法/

2010-04-13 11:24:11 26139

26139 補碼加法,補碼加法計算原理 負數用補碼表示后,可以和正數一樣來處理。這樣,運算器里只需要一個加法器就可以了,不必為了負數的加法運算,再配一個減

2010-04-13 11:41:28 17214

17214 補碼減法,補碼減法原理是什么? 負數的減法運算也要設法化為加法來做,其所以使用這種方法而不使用直接減法,是因為它可以和常規的加法運算使用同一

2010-04-13 11:45:46 6326

6326 減法電路

減法電路和加法電路實質相同,在求和電路中預先將某些信號倒相就可以成為求差電路或混合電路。

差動輸入運算放大器

2010-04-22 17:46:36 19723

19723

加減法電路

利用一個差動輸入的運放就可同時實現加減法運算,這種運算電路如圖5.4-3所示。

2010-04-22 17:50:08 9986

9986

由輸入端選擇運算方式的加、減法運算電路

電路的功能

這是一種配

2010-05-08 11:32:23 1518

1518

高輸入電阻減法運算電路(A-B)

電路功能

因為輸入電阻高,所以信

2010-05-08 13:16:38 5357

5357

加法運算是數字系統中最基本的算術運算。為了能更好地利用加法器實現減法、乘法、除法、碼制轉換等運算,提出用Multisim虛擬仿真軟件中的邏輯轉換儀、字信號發生器、邏輯分析儀

2011-05-06 15:55:07 82

82 電子發燒友為您提供了運算放大加法器電路圖!

2011-06-27 09:28:50 7732

7732

該ALU采取層次化設計方法,由控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊組成,能實現32位有符號數和無符號數的加減乘除運算,另外還能實現9種邏輯運算、6種移位運算以

2012-02-09 15:24:55 80

80 浮點運算器的核心運算部件是浮點加法器,它是實現浮點指令各種運算的基礎,其設計優化對于提高浮點運算的速度和精度相當關鍵。文章從浮點加法器算法和電路實現的角度給出設計

2012-07-06 15:05:42 47

47 8位加法器和減法器設計實習報告

2013-09-04 14:53:33 133

133 為了縮短加法電路運行時間,提高FPGA運行效率,利用選擇進位算法和差額分組算法用硬件電路實現32位加法器,差額分組中的加法單元是利用一種改進的超前進位算法實現,選擇進位算

2013-09-18 14:32:05 33

33 基于FPGA的開方運算實現 ,的技術論文

2015-10-30 10:59:01 5

5 加法運算電路能實現多個模擬量的求和運算。圖1所示為一個3個輸入信號的反相加法運算電路。

2017-05-15 09:41:34 195023

195023

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網絡所構成的運算電路來實現。

2017-08-16 11:09:48 159697

159697

集成運算放大器是一種具有高電壓放大倍數的直接耦合多級放大電路。當外部接入不同的線性或非線性元器件組成負反饋電路時,可以靈活地實現各種特定的函數關系。在線性應用方面,可組成比例、加法、減法、積分、微分、對數等模擬運算電路。

2017-08-18 17:26:18 22855

22855

針對一類乘同余運算,提出了一種快速算法。采用1個32位乘法、2個32位加法、少量移位操作和一個最高位分離操作方法,避免了連續減法和除法運算。

2017-09-07 20:10:57 3

3 運算電路是集成運算放大器的基本應用電路,它是集成運放的線性應用。討論的是模擬信號的加法、減法積分和微分、對數和反對數(指數)、以及乘法和除法運算。

2017-11-27 15:55:10 0

0 結構復雜,采用DSP實現會增加系統負擔,降低系統速度。在某些對速度要求較高的情況,必須采用專門的浮點運算處理器。 EDA/FPGA技術不斷發展,其高速、應用靈活、低成本的優點使其廣泛應用數字信號處理領域。在FPCA技術應用的初期,

2018-04-10 14:25:53 17

17 本文是基于FPGA實現Cordic算法的設計與驗證,使用Verilog HDL設計,初步可實現正弦、余弦、反正切函數的實現。將復雜的運算轉化成FPGA擅長的加減法和乘法,而乘法運算可以用移位運算代替

2018-07-03 10:18:00 2349

2349

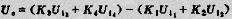

4.1.3加法和減法運算電路

2019-04-18 06:03:00 15197

15197

我通常會喜歡簡潔化。有些人設計喜歡做加法,我們設計喜歡做減法。

2019-03-21 15:52:45 3718

3718 本文檔的主要內容詳細介紹的是模擬電路實驗教程之基本運算電路的詳細資料說明。一。實驗目的1.掌握反相比例運算、同相比例運算、加法、減法運算電路的原理,設計方法及測試方法。2.能正確分析運算精度與運算電路中各元件參數之間的關系。

2019-05-27 17:26:51 22

22 圖2列出了和傳統的4輸入LUT結構的FPGA相比較,采用ALM的StratixⅡFPGA器件例化3輸入加法器的優勢。從圖2中可以清楚地看出,對于同樣3個2 b數據相加的邏輯結構,傳統4輸入LUT結構

2020-03-03 10:45:37 1015

1015

開方運算作為數字信號處理(DSP)領域內的一種基本運算,其基于現場可編程門列(FPGA)的工程實現具有較高的難度。本文分析比較了實現開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

6 所示是減法運算電路,訛通過Ri加到運算放大器的反相輸入端,蚰通過R2、R3分壓后加到同向輸入端,而抽通過Rf反饋到反相輸入端。為了使運算放大器兩輸入端平衡,則}Rl/,RrRzllR3。

2020-09-10 11:07:12 31519

31519

1、集成運算放大器是一種電壓放大倍數極高的直接耦合多級放大電路。當外部接入不同的線性或非線性元器件組成負反饋電路時,可以靈活地實現各種特定的函數關系。在線性應用方面,可組成比例、加法、減法、積分、微分、對數等模擬運算電路。

2020-11-16 08:00:00 26

26 (1) 標號: BCDA 功能:多字節BCD碼加法 給大家介紹一個單片機匯編語言寫的多字節BCD碼加法減法子程序 入口條件:字節數在R7中,被加數在[R0]中,加數在[R1]中。出口信息:和在[R0]中,最高位進位在CY中。

2020-12-06 17:31:00 8019

8019 有些FPGA中是不能直接對浮點數進行操作的,只能采用定點數進行數值運算。對于FPGA而言,參與數學運算的書就是16位的整型數,但如果數學運算中出現小數怎么辦呢?要知道,FPGA對小數是無能為力

2021-08-12 09:53:39 4504

4504 一:算術運算符算術運算符非常地簡單,就是小學數學里面的一些加減乘除操作。不過呢,還是有一些語法細節需要注意的。1.加法運算符 + 1 在第3行利用加法運算符 + 進行了加法運算,再將和賦值給了變量

2021-11-20 20:06:09 2

2 FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 6098

6098 指針的加法操作我們見過很多,但是減法操作遇到的好像很少。

2023-03-29 10:12:35 388

388 本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:13:57 2625

2625

真空衰減法是一種無損、定量的檢測非多孔、剛性或柔性包裝泄漏的方法。壓力衰減測試是一種用于檢測無孔、剛性或柔性包裝中泄漏的定量測量方法。如果加壓氣體的引人導致包裝壁或密封件破裂,則該測試是破壞性

2023-07-27 15:21:41 732

732

,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。 但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方

2023-09-22 10:40:03 394

394

前段時間和幾個人閑談,看看在FPGA里面實現一個Mem加法器怎么玩兒

2023-10-17 10:22:25 279

279

在電子技術的海洋中,有一種電路如同數學中的加法器一樣,能夠將不同的信號進行相加處理。這就是被廣泛應用于信號處理領域的反相加法運算電路。

2024-02-17 15:34:00 378

378

反相加法運算電路利用運算放大器(通常簡稱為Op-Amp)的特性來實現多個輸入信號的加法運算。每個輸入信號都通過一個電阻連接到運算放大器的反相輸入端,而運算放大器的同相輸入端則接地或虛擬接地。輸出電壓

2024-01-31 15:53:51 270

270

異或門可以用于實現二進制數的加減法。例如,我們可以使用異或門來實現兩個二進制數的加法,如果兩個相應的輸入端上輸入的數相同時則進行減法運算。

2024-02-04 14:47:09 740

740

元器件的限制。當時,計算機的電路設計主要采用位操作(二進制)來實現。為了能夠有效地表示負數,人們引入了反碼的概念。使用反碼可以使計算機系統在進行加法和減法運算時使用相同的邏輯電路,從而降低了硬件成本和復雜度。 2.

2024-02-19 15:10:32 147

147

電子發燒友App

電子發燒友App

評論