前言

本系列整理數(shù)字系統(tǒng)設(shè)計的相關(guān)知識體系架構(gòu),為了方便后續(xù)自己查閱與求職準備。時鐘作為數(shù)字系統(tǒng)中的“心臟”,其設(shè)計的質(zhì)量好壞直接關(guān)乎整個系統(tǒng)的穩(wěn)定性,本文主要介紹了數(shù)字設(shè)計中的常見的時鐘產(chǎn)生電路和時鐘類型,并進行相關(guān)分析簡介。

時鐘產(chǎn)生電路

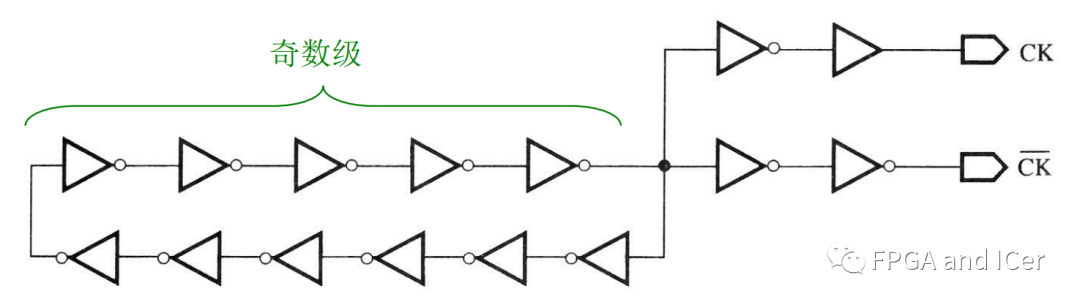

奇數(shù)個反相器首尾相連即構(gòu)成環(huán)形振蕩器(簡稱 「“環(huán)振”」 ),每個反相器兩端出現(xiàn)周期性振蕩信號。

環(huán)形振蕩器

假定每個反相器都相同,所產(chǎn)生的時 鐘周期T或頻率f取決于反相器鏈的級數(shù)N和反相器的傳播延時tp

可通過改變反相器的級數(shù)以及每個反相器的面積來改變輸出的時鐘頻率。

「環(huán)形振蕩器的優(yōu)缺點如下:」

「優(yōu)點:」 電路簡單,無需外接元器件,完全片上集成。

「缺點:」 頻率精度差,隨工藝、電源電壓離散的變化大;頻率穩(wěn)定性差,隨時間、 溫度的變化大。

針對該時鐘的特點,因此該時鐘適用于對精度和穩(wěn)定度要求都不高的片上時鐘產(chǎn)生器。

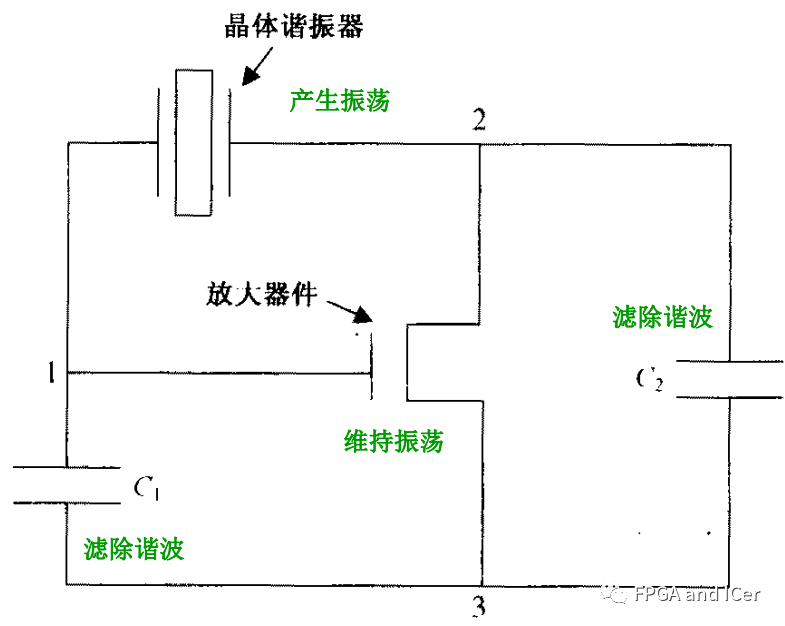

晶體振蕩器

晶體震蕩電路主要構(gòu)成如下,主要由晶體諧振器產(chǎn)生震蕩,電容進行濾除振蕩產(chǎn)生的諧波,放大器將篩選出的頻率進行維持并進行放大,從而產(chǎn)生穩(wěn)定的時鐘信號。

石英晶體兩端加上電壓后,就會產(chǎn)生振蕩電流(機械能 電能),振蕩頻率由晶體的尺寸與形狀決定(晶體越薄越小,頻率越高)。

「晶體振蕩器的優(yōu)缺點如下:」

「優(yōu)點:」 晶體振蕩器頻率穩(wěn)定性高,可達10 ^ -6 (ppm), 而環(huán)形振蕩器只能達到 10 ^ -2(ppm)。

「缺點:」 晶體振蕩器輸出頻率范圍一般不超過100MHz,難以滿足現(xiàn)代高速數(shù)字IC的更高時鐘頻率要求;而且采用非硅工藝的石英諧振器,無法片內(nèi)集成;輸出頻率難以調(diào)節(jié),只能產(chǎn)生單一頻率。

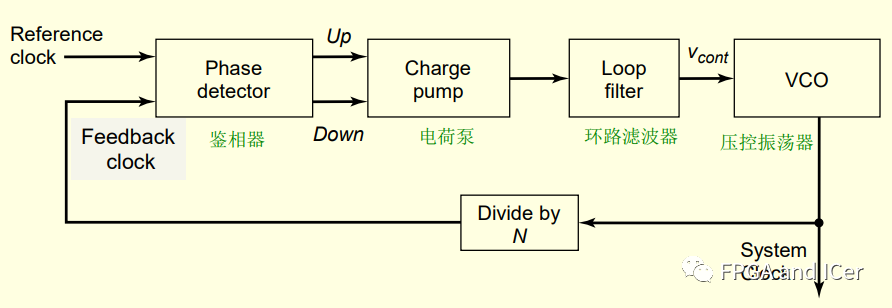

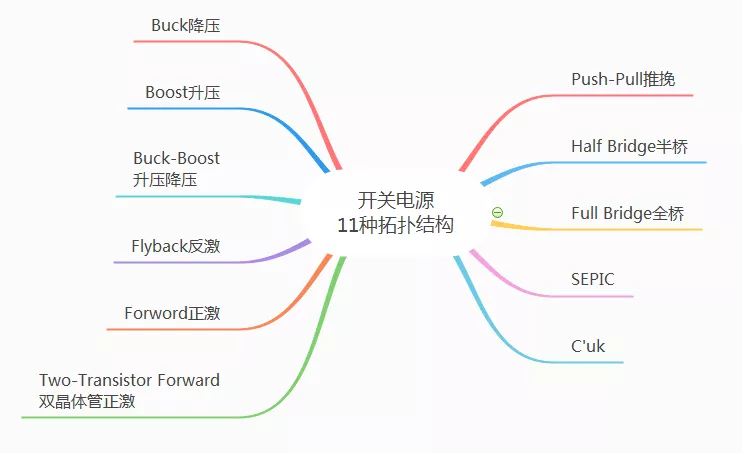

PLL鎖相環(huán)電路

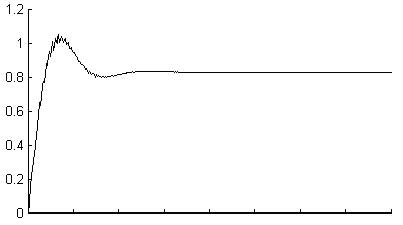

鎖相環(huán) (PLL) 是一種反饋電路,且為模擬電路,性能受工藝、電源噪聲、溫度等的 影響顯著,設(shè)計難度較大。

PLL電路的工作原理是將外部信號的相位與壓控晶體振蕩器 (VCXO) 產(chǎn)生的時鐘信號的相位進行比較。然后,電路調(diào)整振蕩器時鐘信號的相位以匹配參考信號的相位。因此,原始參考信號和新信號彼此是精確同相的。

PLL鎖相環(huán)電路

一個鎖相環(huán)PLL電路通常由以下模塊組成:

「鑒相鑒頻器PFD(Phase Frequency Detector):」 將分頻后的反饋時鐘與參考時鐘的相位進行比較,若反饋時鐘滯后/領(lǐng)先參考時鐘,則發(fā)生一個Up/Down信號。該信號的大小正比于所檢測到的相位差。

**電荷泵: ** 電荷泵將Up/Down信號轉(zhuǎn)換為一個較大/較小的模擬控制電壓Vcont,以便加速/減慢VCO, 從而消除反饋時鐘與參考時鐘的相位差。

「低通濾波器(環(huán)路濾波器)LPF(Low-Pass Filter、Loop Filter):」 用于濾除Vcont中的高頻成分并平滑其響應,減少本地時鐘的抖動。

「壓控振蕩器VCXO(Voltage Controlled Oscillator):」 壓控振蕩器產(chǎn)生系統(tǒng)時鐘信號,信號的頻率受輸入電壓Vcont的控制。利用變?nèi)?a target="_blank">二極管(偏置電壓的變化會改變耗盡層的厚度,從而影響電容大小)與電感構(gòu)成的LC諧振電路構(gòu)成,提高變?nèi)荻O管的逆向偏壓,二極管內(nèi)耗盡層變大,電容變小,LC電路的諧振頻率提高,反之,降低逆向偏壓時,二極管內(nèi)電容變大,頻率降低。

DLL和PLL具有類似的功能,可以完成時鐘高精度、低抖動的倍頻和分頻,以及占空比調(diào)整和移相等功能。DLL即Delay Lock Loop,主要是用于產(chǎn)生一個精準的時間延遲,且這個delay不隨外界條件如溫度,電壓的變化而改變。PLL利用壓控振蕩器調(diào)整頻率來改變相位,DLL利用壓控延遲線調(diào)整延時來改變相位。

DLL調(diào)整相位的方法是用壓控延遲線(VCDL,Votage-Controlled Delay Line)而非 VCO,通過改變延時而非頻率。

「PLL/DLL電路的優(yōu)缺點如下:」

「優(yōu)點:」 穩(wěn)定性好,無需積分運算,極點少;鎖定速度快,PLL需要先鎖定頻率再鎖定相位,DLL直接鎖定相位;抗抖動與噪聲性能好,無環(huán)振VCO 那樣的反饋路徑,對工藝與環(huán)境波動不敏感;可直接產(chǎn)生多相時鐘。

「缺點:」 無法改變輸出頻率,不能倍頻,不 能產(chǎn)生多個時鐘頻率;調(diào)節(jié)范圍較大時,可能產(chǎn)生錯誤鎖定。

時鐘類型

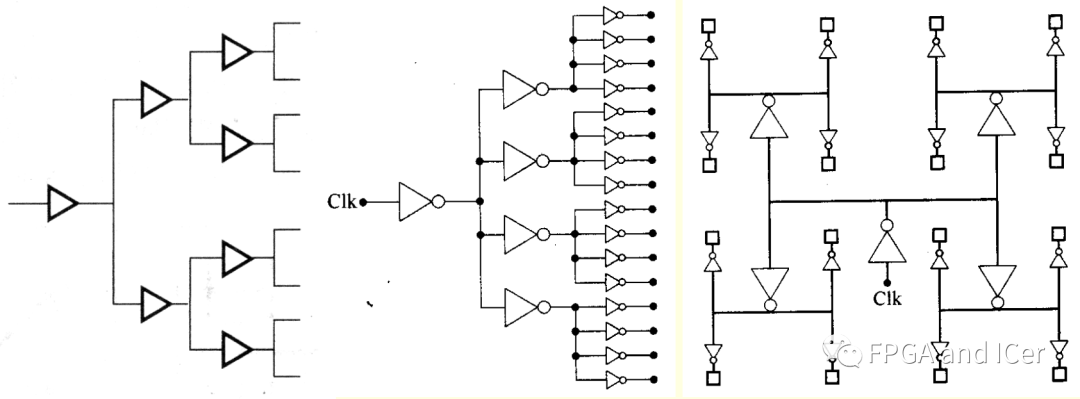

全局時鐘

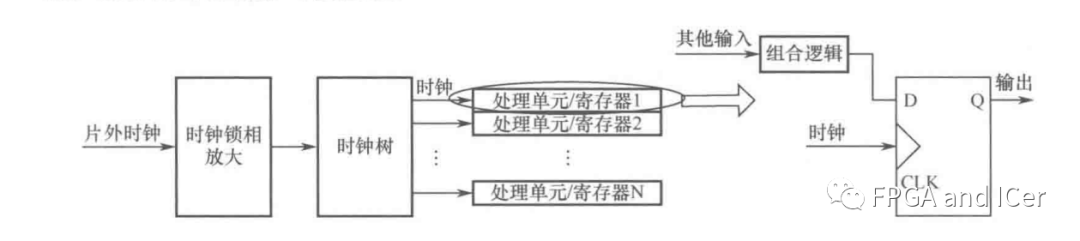

全局時鐘(Global Clock)。一般的時鐘都指的是全局時鐘,全局時鐘在芯片中的體現(xiàn)形式是時鐘樹。

時鐘樹

它是由片上的時鐘管腳引入,經(jīng)過鎖相和放大之后進入時鐘樹,輸出給寄存器的穩(wěn)定、可靠的時鐘信號。這種時鐘的時延通常被設(shè)計得最小,相對抖動也最小。

內(nèi)部時鐘

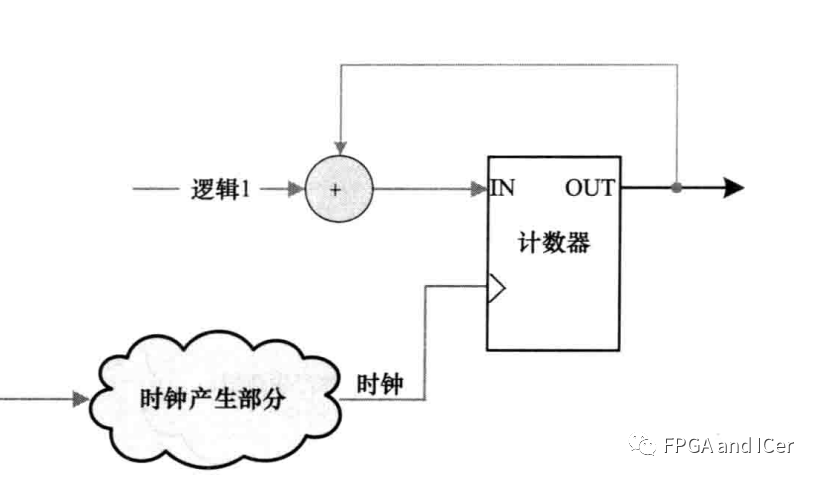

對于內(nèi)部時鐘最早的接觸應該就是使用計數(shù)器輸出的計數(shù)值的相關(guān)邏輯做分頻時鐘。但如果設(shè)計不當,該部分會導致設(shè)計功能和時序問題。組合邏輯電路的常見的引起設(shè)計錯誤的問題:毛刺和延時,同時也是組合邏輯搭建的時鐘所面對的問題。往簡單了說,組合邏輯的毛刺會引起功能的異常,降低系統(tǒng)的穩(wěn)定;延時會引起在時鐘進行時序分析的相關(guān)問題,下面就這兩方面進行說明。

組合邏輯搭建的時鐘產(chǎn)生器會引入毛刺,使功能出現(xiàn)問題,此外由組合邏輯所導致的延遲也會導致時序方面的問題。在同步設(shè)計中,數(shù)據(jù)輸入端的毛刺不會引起任何問題,因為數(shù)據(jù)是在時鐘邊沿處捕獲的,所以可以將毛刺自動濾掉。然而,如果毛刺或尖峰脈沖出現(xiàn)在時鐘輸入端(或者寄存器的異步輸入端)就會產(chǎn)生明顯的影響。

下圖通過邏輯設(shè)計產(chǎn)生了時鐘,時鐘產(chǎn)生部分包含一些組合邏輯,而計數(shù)器的寄存器是對邊沿敏感的,這就導致下圖的設(shè)計毛刺會明顯影響到計數(shù)器的值。

邏輯設(shè)計時鐘產(chǎn)生

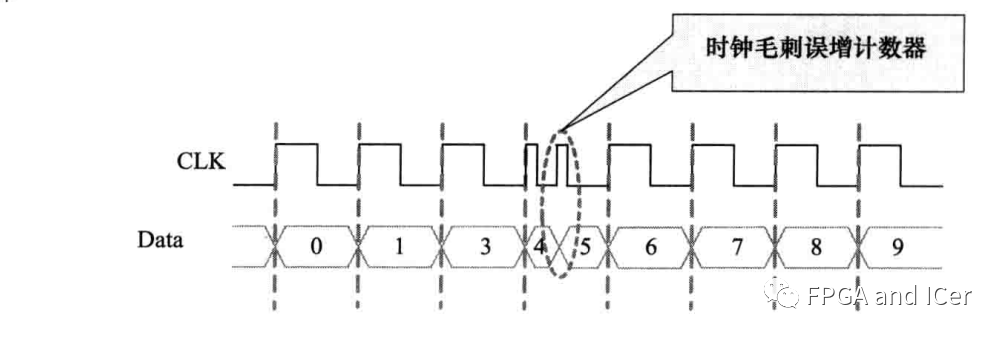

在下面這個例子中可以看到,由于時鐘沿處的毛刺,計數(shù)器在所示的時鐘周期上遞增了兩次。由于時鐘毛刺的作用,計數(shù)器增加了額外的計數(shù)值,這樣就可能導致功能出現(xiàn)問題。

毛刺導致邏輯錯誤

窄毛刺會違背寄存器的最小脈沖寬度要求。在毛刺到達時鐘輸入端時,如果寄存器的數(shù)據(jù)輸入變化,會違背建立和保持時間。即使設(shè)計沒有違背時序要求,寄存器也可能輸出意料之外的值,使整個設(shè)計功能出現(xiàn)風險。

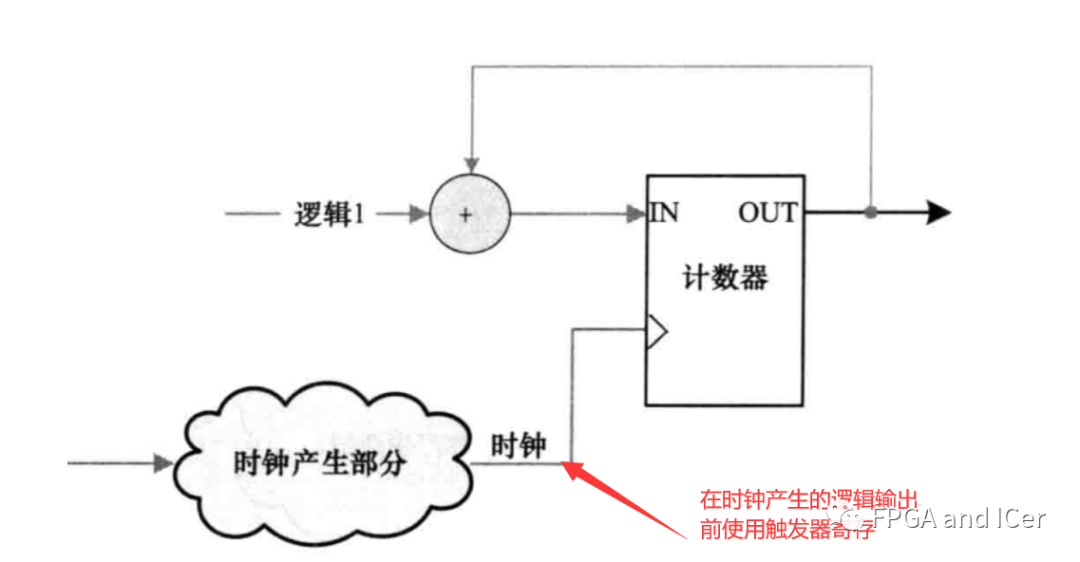

解決毛刺引發(fā)的設(shè)計功能問題,最簡單的辦法就是使用寄存器在時鐘產(chǎn)生邏輯后寄存輸出,這樣無論前級的時鐘產(chǎn)生部分的代碼是否存在毛刺,都使用觸發(fā)器做了寄存,降低了毛刺引起功能錯誤的風險。

解決方法

分析完毛刺的影響,下面分析下組合邏輯構(gòu)建的時鐘引入的延遲問題。

用來產(chǎn)生內(nèi)部時鐘的組合邏輯也會增加時鐘線上的延遲。在某些情況下,時鐘線上的邏輯延遲會導致時鐘偏移比兩個寄存器之間的數(shù)據(jù)路徑延遲更大。如果時鐘偏移大于數(shù)據(jù)延遲,就會違背寄存器的時序要求,設(shè)計的功能也不會正確。

因此,就需要設(shè)計時鐘時盡量減少時鐘偏斜,一種減少時鐘偏移的方法是將產(chǎn)生的時鐘放到SoC中高扇出且低偏移值的時鐘樹上。「使用低偏移值時鐘樹有助于減少信號整體的時鐘偏移。」

分頻時鐘

許多設(shè)計需要來自于主時鐘的分頻時鐘。在設(shè)計中要保證大多數(shù)時鐘來自于PLL。使用PLL能避免由異步時鐘分頻邏輯引起的許多問題。在對主時鐘進行分頻時,應該始終使用同步計數(shù)器或狀態(tài)機。

此外,設(shè)計應該保證總是由寄存器直接產(chǎn)生分頻時鐘信號。不要對計數(shù)器或狀態(tài)機的輸出進行解碼,然后產(chǎn)生時鐘信號;這種實現(xiàn)方式常會導致毛刺和尖峰脈沖。可參考內(nèi)部時鐘的舉例。

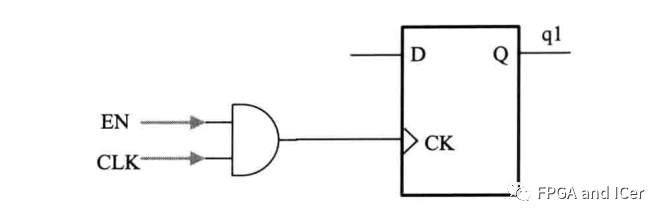

門控時鐘

門控時鐘的時鐘線上的門控單元會導致時鐘偏移,并會引入尖峰脈沖作用于觸發(fā)器。但在涉及到低功耗設(shè)計時(通常ASIC中),門控時鐘還是比較常用的。

門控時鐘

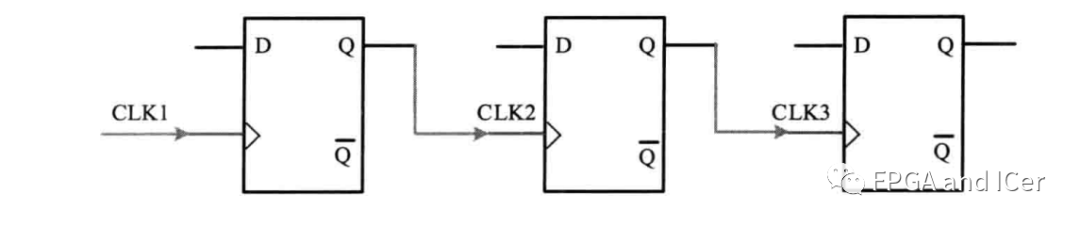

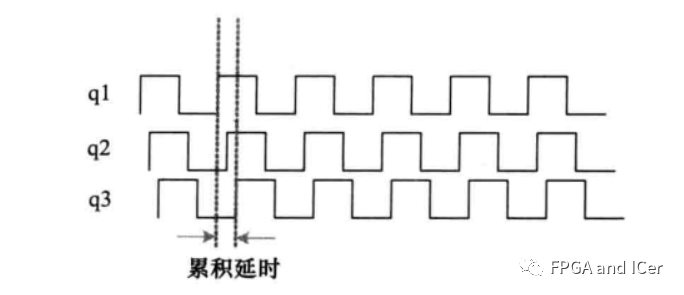

行波時鐘

行波計數(shù)器:將觸發(fā)器前級輸入引腳連接至下個寄存器的輸入引腳,依次級聯(lián)。由于第一個觸發(fā)器時鐘到Q的延遲而使第二個觸發(fā)器的時鐘輸入產(chǎn)生偏移,而且不能在每個時鐘邊沿都激活。此時,延時逐漸累積會在引入時序分析和綜合麻煩,因此需要盡量避免使用這種結(jié)構(gòu),

行波計數(shù)器

積累延時

盡管使用行波計數(shù)器(或者行波時鐘)存在各種問題,但是在功耗較高的系統(tǒng)中很適合使用這種計數(shù)器,因為這樣能大量降低由邏輯或SoC所引起的峰值功耗。

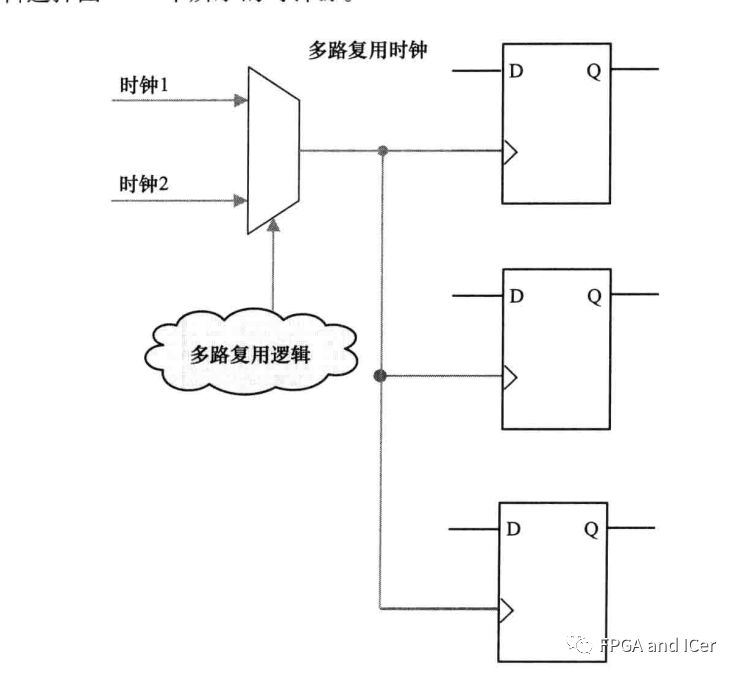

多路時鐘

時鐘多路器用于使同一個邏輯功能具有不同的時鐘。某些類型的多路邏輯選擇如下圖所示的時鐘源。

多路邏輯選擇時鐘源

例如,需要處理多個頻率標準的通信應用常常使用多個時鐘。雖然在時鐘信號上引入邏輯上的問題,是在不同的應用中對多路時鐘的要求差別很大。

在能滿足下面的標準,時鐘多路操作就是可接受的:

在初始化配置后,時鐘多路邏輯就不再改變。

在測試時,設(shè)計會繞過功能時鐘多路邏輯而選擇普通時鐘。

在時鐘切換時,寄存器始終處于復位狀態(tài)。

在時鐘切換時產(chǎn)生的短暫錯誤響應沒有負面影響。

如果設(shè)計中時鐘切換很頻繁,并且不在復位時切換,設(shè)計也不能容忍芯片中出現(xiàn)短暫的錯誤響應,就必須使用同步設(shè)計以確保寄存器沒有違背時序,時鐘信號上不出現(xiàn)毛刺同時沒有競爭條件或其他麻煩。

為了實現(xiàn)時鐘切換,在xilinx的原語中,存在CLK選擇的結(jié)構(gòu)以供設(shè)計者進行選擇設(shè)計,按下面的原語示例,設(shè)計時需要控制信號S滿足建立時間和保持時間,可實現(xiàn)時鐘的無毛刺切換。

?

?

???BUFGMUX?#(

??????.CLK_SEL_TYPE("SYNC")??//?ASYNC,?SYNC

???)

???BUFGMUX_inst?(

??????.O(O),???//?1-bit?output:?Clock?output

??????.I0(I0),?//?1-bit?input:?Clock?input?(S=0)

??????.I1(I1),?//?1-bit?input:?Clock?input?(S=1)

??????.S(S)????//?1-bit?input:?Clock?select

???);

?

?

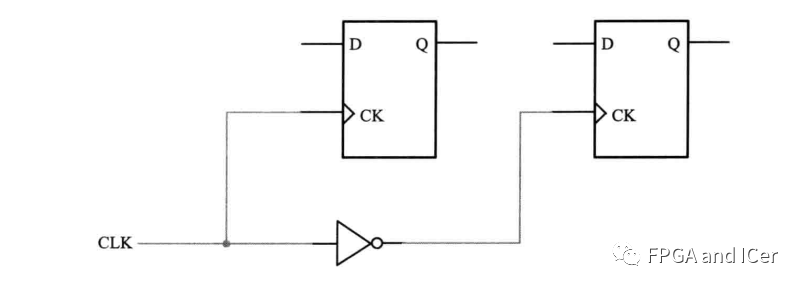

雙邊沿或混合邊沿時鐘

雙邊沿時鐘是指在時鐘的上升沿和下降沿都進行數(shù)據(jù)傳輸,兩個觸發(fā)器由兩個相位相反的時鐘信號控制。

雙邊沿或混合邊沿時鐘

這樣操作會為使用同步復位和使用插入掃描鏈這樣的測試方法帶來麻煩,同時也會增加確定關(guān)鍵信號的路徑的難度。

但雙沿采樣時鐘也是有好處的。

雙沿時鐘使得原本一個周期輸出/輸入一個數(shù)據(jù)的架構(gòu),改變?yōu)橐粋€周期輸出/輸入兩個數(shù)據(jù),這樣在不升高時鐘頻率的前提下,提升了信號的吞吐率,從而帶來「性能的提升」。另外一個使用雙沿時鐘的優(yōu)勢是「降低功耗」,因為時鐘頻率減半,所以系統(tǒng)的功耗只有等效同步電路的一半。

但一般情況下,不建議使用雙邊沿時鐘,這是因為:

由于上下沿都用,要求時鐘的質(zhì)量很高,一般的時鐘源很難達到,成本高。

由于時鐘的抖動等不確定因素的存在,容易使時鐘的占空比發(fā)生改變,因此容易引起建立時間和保持時間的違規(guī)。

?

在FPGA中的通常高速傳輸時會用到雙沿采樣時鐘,DDR存儲同樣也是使用的雙沿采樣,但在常規(guī)情況下不使用雙沿采樣時鐘。

?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論