在遠程更新的時候,有時候需要雙鏡像來保護設計的穩定性。在進行更新設計的時候,只更新一個鏡像,另一個鏡像在部署之前就測試過沒問題并不再更新。當更新出錯時,通過不被更新的鏡像進行一些操作,可以將更新失敗的數據重新寫入Flash。這樣即使更新出錯,也能保證設計至少可以被遠程恢復。

Xilinx的雙鏡像方案成為Multiboot。本文對Xilinx 7系列的Multiboot做一些簡單介紹。

Multiboot直接操作的是兩個鏡像,但實際上可以用于多個鏡像。為了便于描述,Multiboot中的兩個鏡像分別成為G鏡像(Golden)和M鏡像(Multiboot)。

遠程更新的方案,有一些是通過FPGA來讀寫Flash的,例如Xilinx平臺下需要自己實現的Flash讀寫控制器,Altera平臺下的ASML IP。當無法提供JTAG等其他連接時,Flash的更新就只有FPGA一種方案。

當寫入Flash的操作出現錯誤,或者Flash中部分地址中的數據出現錯誤,導致無法正確寫入或者存儲的數據出現錯誤,這樣會導致FPGA無法加載成功。

當FPGA無法加載成功或者工作不正常的時候,Flash的讀寫操作也就無法得到保證。此時也就不能重新通過遠程更新方案來重新讀寫Flash,糾正之前的錯誤。所以可以看到,如果Flash直接由FPGA控制,當遠程更新出現錯誤時,很可能導致遠程更新徹底失效,只能安排現場更新來修復。

對應方案就是使用雙鏡像(多鏡像),更新的時候只更新M鏡像,更新后直接使用M鏡像。當出現M鏡像更新出現錯誤的時候,則啟動G鏡像。通過G鏡像中的設計來重新更新Flash中M鏡像部分的數據。

由于G鏡像從來沒有被更新過,這樣出現錯誤的概率也就非常小。這樣即使M鏡像出現錯誤,可以通過G鏡像來完成一些工作(例如Flash讀寫操作),由此來保證設計一直可以使用。

從這個分析可以看出,雙鏡像的方案,需要完成兩個任務。

1.正常情況下,加載完成時應該是M鏡像在運行

2.出現錯誤的時候,需要返回G鏡像

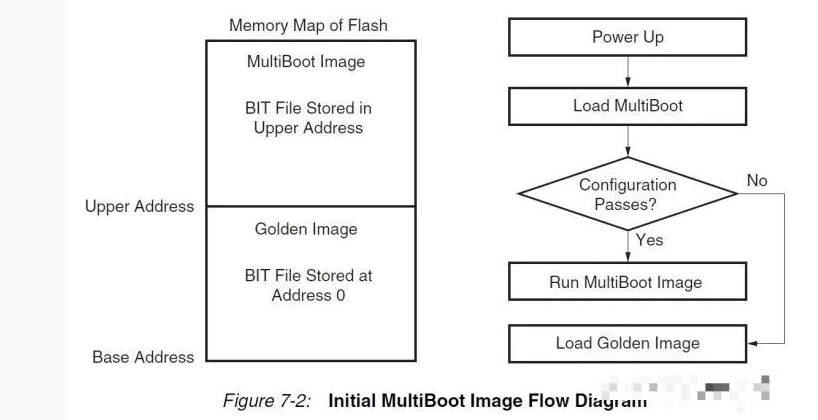

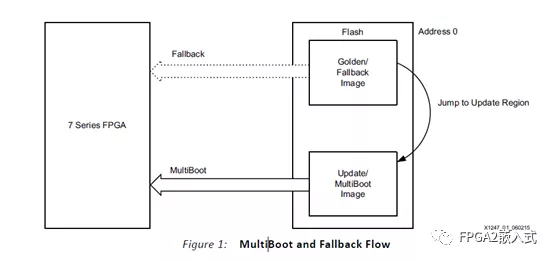

圖片來自UG470

從上圖可以看到,Xilinx 7系列FPGA的Multiboot方案是從基地址開始存放G鏡像,后續存放M鏡像。加載過程中是先加載M鏡像,配置完成后如果成功,則運行M鏡像;如果運行失敗,則重新加載G鏡像。

下面就從需要完成的兩個任務,結合上圖來進行介紹。

先看第一個任務,加載M鏡像。

上電完成之后,FPGA就會按照設置,進行加載操作。在主動模式下,FPGA會開始對Flash的操作,嘗試讀取Flash中存儲的配置鏡像數據。需要注意的是,主動模式下的這一系列操作都是FPGA自動完成的,用戶無法控制。

所以就出現了第一個問題。既然讀取操作是自動的,那么FPGA是如何知道M鏡像存儲在哪里,并先加載M鏡像呢?如果是從0地址開始讀取,那么應該先完成G鏡像的加載。否則,是否使用Multiboot及M鏡像的地址,是如何傳遞給FPGA、讓FPGA知曉呢?

Xilinx的Multiboot方案中的解決辦法是使用一條加載命令:IPROG。而這條命令,是放在G鏡像中。

具體說,對于FPGA直接從0地址開始讀取,先開始加載G鏡像,但是這個G鏡像是經過特別處理的,在鏡像數據剛開始的部分添加了IPROG命令和M鏡像的地址。當FPGA讀取到這個命令之后,就會直接跳過后面的數據,從設置的地址開始繼續加載。這樣的操作,導致G鏡像只是運行了最前面的幾條加載命令,而M鏡像也只是等了幾條命令的操作就開始加載了,保證了M鏡像的直接加載。

需要說明的是IPROG這是一條命令,所以既可以在G鏡像中生效,也可以在設計中任意使用。用戶可以將IPROG命令發給ICAP,來實現任意時間觸發重新加載的需求。通過設置合適的地址,可以實現多個鏡像的切換。

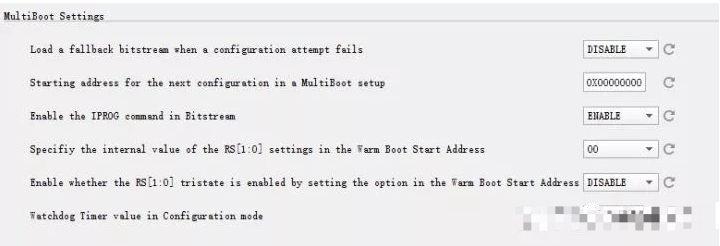

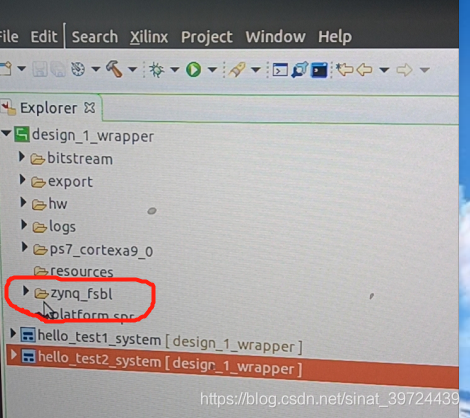

圖片截取自Vivado

從vivado中的設置可以看出,Multiboot的主要設置只有這6個。第一個成為Fallback,最后一個成為Watchdog。這兩個下文會做介紹。第四個第五個是關于RS pin。等熟悉Multiboot理解之后可以查看文檔進行理解,本文不做深入介紹。

第二個是設置跳轉到的地址、第三個是在G鏡像中加入IPROG命令。這兩個操作可以以命令的形式發給ICAP接口,從而觸發Multiboot中轉跳并加載新的鏡像數據。

看完上述的分析,應該明白如何實現先加載M鏡像這個需求了。下一步就是,在加載失敗時如何回退到G鏡像。

M鏡像加載不成功,需要回退到G鏡像的操作,Multiboot方案稱這一步驟為Fallback。

Fallback在四種條件下會被觸發:

1. ID Code錯誤

2. CRC錯誤

3. Watchdog超時

4. BPI地址越界

ID Code錯誤是指配置文件中的器件型號和當前器件不匹配。CRC校驗是指配置數據送入FPGA之后會進行校驗,如果數據不一樣則會提示CRC錯誤。這兩個基本原理比較容易理解,至于具體細節,需要能解析bit文件的內容之后才能充分理解。

Watchdog超時是指在規定的時間內如果無法配置成功,則觸發Watchdog超時,進而會導致Fallback。

BPI地址越界是指發現逐步增長的BPI地址超過最大值,發生溢出,回到0,則除法Fallback。

大概理解一下四個條件之后可以看到,BPI是只針對BPI模式的,和Watchdog有一點類似,都是在一段時間內如果沒有加載成功,地址會逐步增加,計時器會逐步增加,超過范圍后就觸發Fallback,所以BPI就不做進一步解釋了。

ID Code也不做進一步解釋了,因為ID Code不對,大概率是用錯鏡像文件了。所以也沒有太多可以分析的。

重點是2和3,當存在Multiboot鏡像的時候,如M鏡像的內容出現問題,則會觸發CRC校驗錯誤,這樣可以保證鏡像加載成功之后,數據是沒有問題的。

但是如果沒有Multiboot鏡像,則CRC校驗無法進行,或者加載到一半就掛死了。這個時候就需要Watchdog來觸發Fallback。只要一定時間內加載沒有完成,就一定會觸發Watchdog超時。

所以CRC是用來保證加載正確的,Watchdog是用來保證一定會提示加載失敗的。

注意,Watchdogd的計時設置,請設置好然后實際測試一下,而不要僅僅憑經驗/文檔來推斷一個合適的值。

當發生了Fallback之后,工程會反跳回0地址開始加載,從新加載G鏡像。這里,FPGA內部的配置寄存器會做記錄,當發生Fallback之后,會自動忽略IPROG命令,直接加載G鏡像后續的部分,來保證G鏡像有機會被完整的加載。

FPGA自帶一些寄存器,記錄了FPGA加載時的一些狀態,通常稱為device status寄存器。當初出現加載失敗的問題時,可以通過JTAG查看相關寄存器來尋找一些線索,幫助定位問題。

通過這一系列復雜的操作,可以實現雙鏡像的配置切換。這種方法最大的優點就是速度快。在配置完成之后可以快速的跳轉、加載和返回。最關鍵的雙鏡像選擇這一步是在加載初期就進行轉跳,所以跳轉非常迅速,適合一些對配置時間有要求的場合。缺點就是原理和設置都相對麻煩了一些。

和上述方法不一樣的一個雙鏡像切換的方法就是用戶自行做切換。大致原理是用戶利用FPGA的可編程邏輯資源對ICAP模塊進行控制,輸入需要跳轉的地址然后輸入IPROG命令,來觸發跳轉操作。這個操作是需要先加載好G鏡像并開始運行,然后由用戶來控制什么時候進行跳轉。

這樣操作的優點有:

1.跳轉地址由用戶自行選擇,所以可以在多個鏡像中跳轉,而不限于兩個;

2.可以選擇在合適的時間進行加載,用戶選擇性更大。

主要缺點:

1.需要對配置過程、ICAP端口和控制命令有更多的理解

2.需要加載完至少一個鏡像才能使用,所以對配置時間要求高的場景無法使用

如果僅僅是為了遠程更新,那么這個方案,并不合適。用自動的雙鏡像方案更簡單易用一些。只要G鏡像調試完畢,整個方案對M鏡像的要求比較低。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論