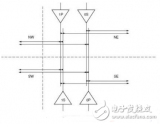

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 6343

6343

FPGA引腳信號指配有什么原則?

2021-04-30 07:04:56

最近買了一個特權的FPGA開發板 ,FPGA型號是EP4CE6E22C8,利用開發板產生PWM波。學習過程中發現一個問題,假如用同一個bank組的IO口產生互補的PWM波是沒問題的。但是分別使用兩個

2016-07-30 11:01:45

小弟剛買的FPGA核心板,打算自己畫底板的說。買的核心板沒有給引腳配置,只給了原理圖,原理圖上雖然標明了FPGA的引腳,可是……這個東西怎么看呀?它不像是買的開發板那種,什么A11,W8這種,而是IO,DIFFO_T13P這種。我是該找賣家要一份,還是說要自己看,慢慢去對它的引腳呢?

2017-06-12 08:27:50

FPGA如何對引腳進行分塊?是由VCC的電壓不同進行自行設計分塊?還是每個塊的引腳都是固定的?在進行DDR3與FPGA的硬件連接時,由FPGA的芯片手冊得采用SSTL_15電壓標準,即VDDQ

2021-11-29 16:10:48

分配fpga管腳時該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-06-17 08:55:43

各位發燒友好,我是一位FPGA初學者,使用AS模式把程序下載到FPGA中,輸出的電平全是高電平,我也把不用的引腳設置成As input tri-stated,是不是FPGA短路燒毀了,先感謝大家

2015-09-11 20:58:46

FPGA配置引腳說明使用EMCCLK引腳,全速加載程序FPGA加載時序

2021-02-03 06:47:35

一、FPGA配置引腳說明1、CFGBVS如果VCCO0連接至2.5V或3.3V,CFGBVS連接至VCCO0。如果VCCO0連接至1.5V或1.8V,CFGBVS連接至GND。建議bank...

2022-02-08 06:52:31

一、FPGA配置引腳說明 1、CFGBVS 如果VCCO0連接至2.5V或3.3V,CFGBVS連接至VCCO0。 如果VCCO0連接至1.5V或1.8V,CFGBVS連接至GND

2021-01-15 16:43:43

用tcl文件配置引腳后 點擊 Run 后就退出到代碼界面,然后查看了引腳是否分配成功發現沒有分配,這是怎么回事呢?要怎么解決?

2013-09-25 20:00:30

我是fpga開發板的新手,我想知道如何開始使用引腳分配,特別是u*** / serial引腳連接。任何其他pin信息都會有所幫助謝謝

2020-07-19 11:47:31

當未使用的輸出在約束文件中注釋掉并且顯然未在項目中聲明時,fpga板上的輸出引腳狀態是什么 - 特別是對于Vivado 14.4 Verilog。在一些示例中,未使用的輸出端口在約束文件中明確聲明

2019-04-01 07:26:06

本帖最后由 zht24kobe 于 2013-4-20 14:23 編輯

請教一下各位,fpga的引腳電平(I/O standard)應該設置為多少呢,當然和芯片連接的時候可以參考芯片的說明,其他時候,比如LED,外接晶振,按鍵啊,這些時候電平設為多少合適,是不是越低越好,這樣功耗少一些?

2013-04-20 14:21:33

FPGA中的引腳門,那些有著特殊用途的引腳,都有哪些能用作普通IO

2012-10-27 15:34:42

Altera FPGA中NC引腳連接電源或者地會不會有影響?

2021-01-08 14:31:07

嗨, 我想把晶體振蕩器的CLK帶到FPGA里面的數字設計。該CLK連接到FPGA的I / O引腳。如果我在映射中運行Impliment設計,我將得到錯誤。所以我將在UCF文件中將網名命名如下。NET

2019-01-29 10:05:43

嗨,我想用相同的xc7k325 FPGA來設計定制板而不是kc705評估板,并試圖理解配置引腳(見附件1)。但我不明白FPGA_VBATT(引腳C10)的用途。它是否必須由外部來源高(參見附件2

2020-05-13 09:42:06

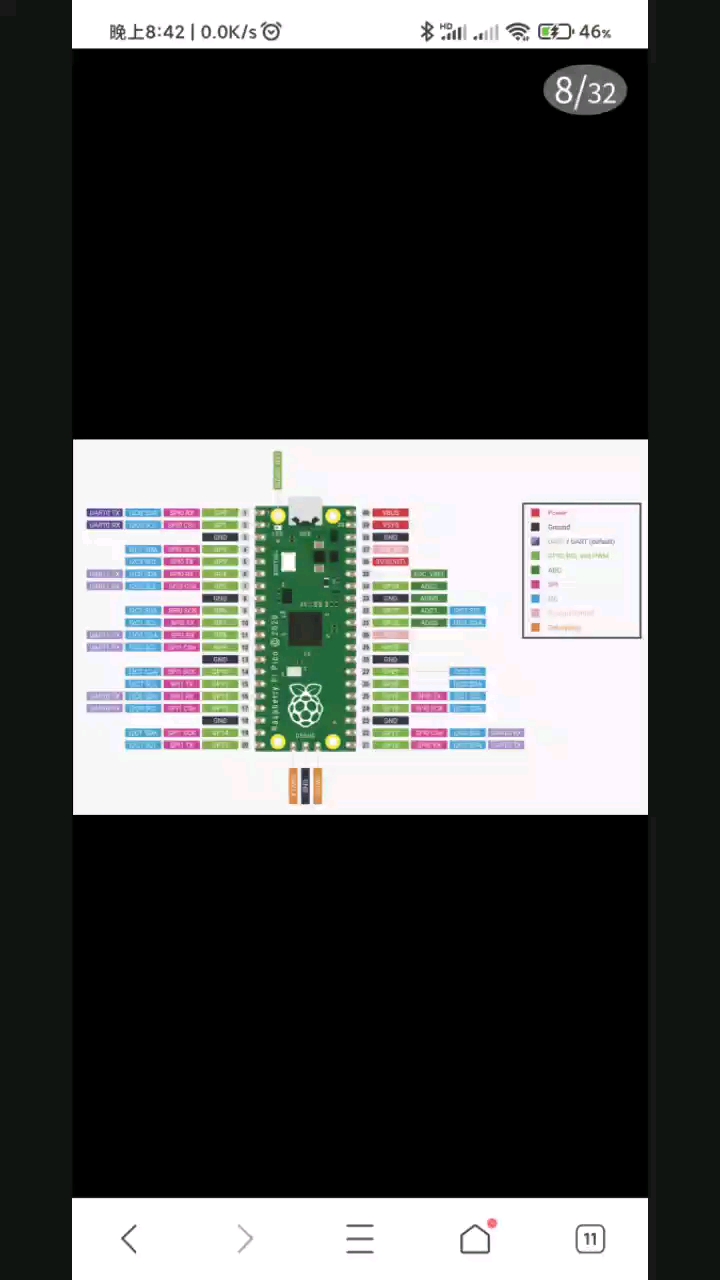

Pico板具有哪些特性?引腳是如何分布的?

2022-01-20 07:11:38

等設備與 MCU 間,要求通訊速率較高的場合。芯片的管腳上只占用四根線。MISO: 主器件數據輸出,從器件數據輸入。MOSI:主器件數據輸入,從器件數據輸出。SCK: 時鐘信號,由主設備控制發出。NSS(CS): 從設備選擇信號,由主設備控制。當NSS為低電平則選中從器件。二、引腳分布ST

2021-08-11 07:54:01

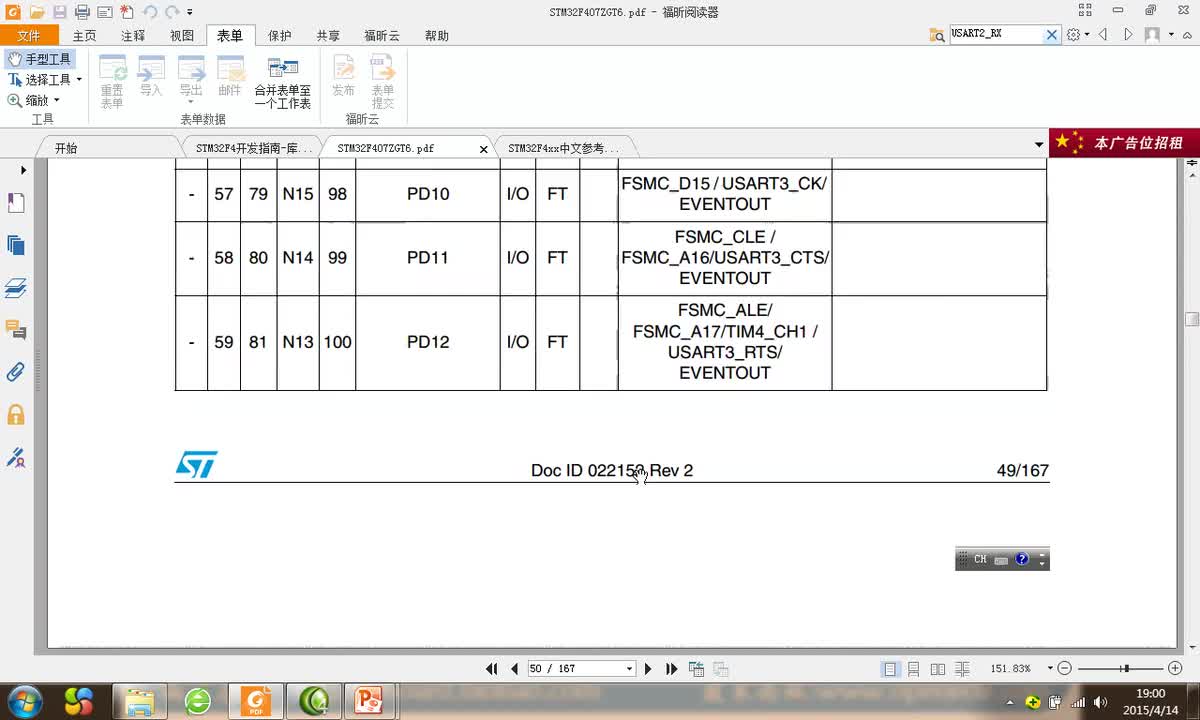

在《STM32F103xCDE_DS_CH_V5(帶有引腳定義)》手冊中第18頁有這個100腳芯片的引腳分布,做STM32F103設計的常常用到。

2022-02-11 06:22:01

大家好!想請教一下,Xilinx FPGA可以設置引腳帶內部上拉電阻嗎? 怎么設置?

2013-10-11 20:59:26

你好,我目前正在為我的Zynq 7020 FPGA做一個RTL引腳規劃。我有一個非常基本的問題。我在PL EMI上的PS和AXI EMC v3.0 ip核心上只有很少的接口。在合成之前,我可以為此IP核進行引腳規劃嗎?另請告訴我針腳規劃的整個步驟。

2020-04-10 10:21:22

在做原理圖庫的時候 有一個芯片 有很多重復 GNDNCVDD 引腳 當我把所有的引腳 都命名為同一個名稱的是候軟件會報出一個錯誤*我想請教各位高手有辦法把這個錯誤消除掉嗎?軟件應該該如何設置下呢?

2013-03-26 16:49:32

各位大神,我自己焊了一塊FPGA的最小系統板,FPGA能下載程序,下載程序前就把unused pins設置為input tri-stated,但除了所有的引腳都輸出高電平是什么狀況?確認沒有虛焊,電源、jtag都沒問題。。

2016-04-13 21:27:28

2上的GCLK引腳(T9)。該時鐘是方波,周期為10nsec,上升/下降時間約為1nsec,僅在總線突發傳輸期間有效。當MCU執行突發讀取時,FPGA驅動所有16個數據總線引腳。這些引腳配置為

2019-08-08 06:49:12

`例說FPGA連載33:PLL例化配置與LED之使用Tcl Console進行引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

剛開始學習fpga,對引腳分配的問題不是很理解,求高手給予幫助 例如fpga的線路板上23引腳接clk ,28引腳是空余的 ,那么在編程的時候我可以用 28引腳接clk 嗎?

2013-01-06 15:24:21

讀FPGA手冊發現里面有很多IO, DIFFIO_L26p, (DQ0L)/(DQ1L)/(DQ1L),不懂這樣的引腳是什么意思啊?還有DQS for X8/X9 in F324又作何解釋?哪位前輩有關于FPGA引腳解釋的文檔或說明,感激涕零

2014-04-17 15:25:17

`勇敢的芯伴你玩轉Altera FPGA連載49:PWM蜂鳴器驅動之引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD

2018-02-27 21:50:07

嗨,來自Cadence方面,我迷失了如何定制引腳名稱。在節奏中,您只需放置引腳并根據需要命名它們,然后使用“創建單元視圖 - 從單元格視圖”,然后生成具有相同引腳命名的符號。在ADS中,似乎你只能

2018-11-27 15:49:37

嗨,可以在Chipscope中看到FPGA外部引腳......?問候Naveen G K.謝謝娜文G K.

2020-03-31 09:55:44

有人可以幫我解釋XC7K325T-2FFG900C FPGA的引腳名稱。實際上我想了解XC7K325T-2FFG900C FPGA中的GCIO引腳。下面我附上了文件

2018-11-05 11:31:27

大家好,我剛開始學習FPGA并試圖弄清楚哪些FPGA引腳可以分配我的數據信號。我正在使用FPGA Spartan 6封裝TQG114器件LX9。查看產品規格,有102個可用的用戶I / O.這是

2019-04-23 06:55:23

,首先最主要的一點,我們先來了解FPGA的IO。 FPGA的IO命名。FPGA芯片IO命名方式太多,管腳也多,讓人感覺很亂。這是我當年的感覺,諸如會經常聽到:A13,B14···BANK34

2020-12-23 17:44:23

我正在使用cusotmised Virtex 6 Fpga(V6_XC6VLX550T封裝FF1760)我正在嘗試使用VREF和VRP和VRN引腳作為用戶I / O引腳。任何人都可以幫助我,我能否根據我的要求使用這些引腳..

2020-06-11 12:06:58

如何克服FPGA I/O引腳分配挑戰?

2021-05-06 08:57:22

我有一塊fpga板子,其情況如下:

板子在設計時預留有備用引腳,這些備用引腳所在的IOBANK的電壓值為3.3V。

我現在想要一個在fpga里有一個邏輯一直為1的輸入信號,這個信號通過備用引腳中的一

2023-04-23 14:55:18

請問如何在函數中命名引腳,如[C] 純文本查看 復制代碼//兩個函數在同一個程序中。以下為示例需求***it P1_1= P1^1; void test(){P1_1= P1^2;}void

2019-07-10 04:12:56

的IIC引腳設置為漏極開路。我讀了ug471:7系列fpga selectedIO資源, ug768:7系列硬盤 ug865:zynq-7000-pkg-pinout但我沒有找到將iic引腳設置為漏極開路的方法。你可以幫幫我嗎?謝謝。

2020-05-14 06:37:27

嗨,大家好, 我是FPGA的新手,有一個簡單的問題可能需要你的幫助。我有一個Virtex 5 ML506 XC5VLX50T板,我想找到一些golbal時鐘IO引腳。我檢查了用戶指南文件(ug347

2020-06-08 14:18:44

大家好, 我在spartan-6 FPGA(XC6SLX9TQ144)板上遇到了問題。我發現我的FPGA的所有io引腳在配置之前都處于高位狀態。但是我需要它們低。我不知道究竟是什么原因。我

2019-07-26 12:00:25

信號)哪個引腳用于此目標以及哪些引腳用于從osiloscobe看到此信號。 (我知道ADC / DAC使用但我沒有看到任何ucf文件)2-)FPGA存儲數據的容量是多少?例如,我想實時存儲這個模擬信號

2019-05-22 13:15:46

大家下午好,我計劃使用主fpga板的IO引腳配置目標cpld板,即菊花鏈。我使用主fpga板的IO引腳連接cpld的JTAG頭。如何編程master fpga的IO引腳來配置目標cpld?請發送與此相關的任何文件....謝謝問候Vimala

2020-03-24 06:43:09

引腳都將轉到fpga。我想將板作為第一步,以節省原型零件的費用,所以我試圖找出在不使用ISE YET的情況下為地址線,數據總線等分配引腳的最佳方法。不會使用RAM。謝謝!以上來自于谷歌翻譯以下為原文I

2019-01-21 06:02:55

(PLIB_PORTS_PinClear、PinSet、PinToggle等),當有可能在“引腳設置”中命名引腳時,我真的很想使用它,如“我想將引腳7(RB3)命名為“通知LED”。在生成代碼時,Harmony

2019-10-10 06:56:20

嗨, 我使用的是XC6SLX45設備,其中我接口DDR SDRAM。在上面的FPGA器件中包含4個Bank。其中每個bank包含3或4個VREF引腳。通常在DDR SDRAM連接中,我們必須

2019-05-31 09:57:19

你好,我正在使用ISE 14.1在CPLD(XCR3256XL)上實現設計。我完成了原理圖,包含了所有I / O引腳并命名。原理圖包含6個解碼器和大量基本邏輯門(AND,NOR等)。當我選擇我的頂級

2020-04-21 09:43:50

怎樣將FPGA時鐘引腳作為普通輸入引腳設置,在軟件中怎樣設置?求解答{:2:}

2013-05-21 20:11:34

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應用程序中,我可以使用哪些方法來檢查這些?請提供一些想法。謝謝

2019-04-01 12:33:26

親愛的每一個人, 我對fpga編程有疑問..如果我想使用另一個fpga來做它(例如編程fpga2我將使用fpga1),除了jtag之外,我可能需要從fpga1獲取額外的引腳( TDI,TDO,TMS

2019-03-22 06:03:59

fpga剩下7個引腳,全是clk,只能做輸入,想接收16個移相器的16個狀態,一般需要8個腳,有沒有別的寫法,用7腳就可以搞定的?一般的話,16個移相器要4位,16種狀態要4位,8位就很舒服了,可是剛好少一位,請教論壇高人指點下!說下思路或者寫法,我現在用verilog hdl!

2011-06-22 16:13:54

想問問各位大神,在做FPGA的外圍電路時,除了專用引腳,每一個功能模塊對應的引腳是固定的嗎?還是說用戶I/O可以隨意分配引腳給外圍電路?

2019-04-08 08:43:16

請問哈FPGA的輸入輸出信號跟端口引腳一定是一一對應的吧?

2019-04-16 04:46:22

百度一下 看到有很多種 而且又不給出型號 所以請教下友友們 10引腳D4021ASR 數碼管 的分布圖 現在在做單片機數字時鐘 學校給的材料就是那樣所以不能拿別的替換

2013-09-13 12:32:40

pads LOGICError on pin number 16in number length must be from 1 to 40 characters ,PADS LOGIC原理圖每個引腳命名最多只能40個字符嗎?有些單片機引腳復用那么多功能就寫不全了?

2019-09-28 23:41:24

你好我對DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

目錄選擇TIM5CH21、GPIO配置輸出2、定時器配置3、調用函數使用初次易錯點:使用pwm輸出是首先要看,那個引腳使用可以使用pwm輸出。高級控制和通用定時器通道引腳分布:高級定時器通用定時器 TIM1TIM8TIM2TIM5TIM3TIM4 CH1PA8/PE9PC6PA...

2021-09-16 06:40:25

ide接口引腳定義圖

IDE 是 Integrated Drive Electronics 的縮寫,由 Compaq 和 Western Digital 公司開發,新版的 IDE 命名為 ATA 即 AT bus Attachment,IDE 接口在設備和主板

2007-11-23 18:44:41 11195

11195

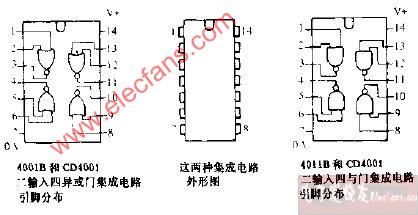

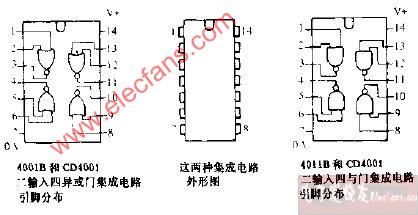

集成電路外形與引腳分布圖

2009-06-10 10:20:18 4695

4695

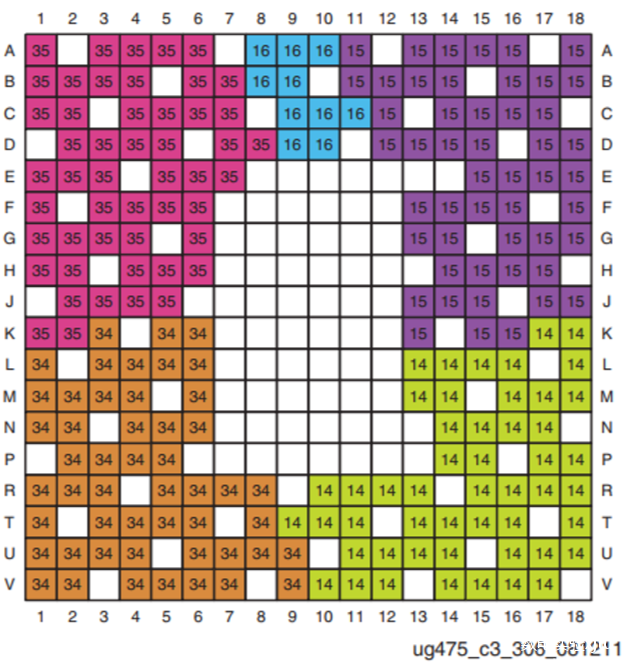

現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳信號指配的指導方針有

2010-11-08 18:23:52 868

868 樹莓派引腳(含有每個引腳)。

2016-04-18 14:29:02 2

2 FPGA學習資料教程之Xilinx-FPGA-引腳功能詳細介紹

2016-09-01 15:27:27 0

0 引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 10273

10273 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2017-05-18 10:51:54 29124

29124

本文檔內容介紹了MagicSOPC主板FPGA-IO引腳分配表,供參閱

2018-03-15 15:50:59 6

6 對于需要在PCB板上使用大規模FPGA器件的設計人員來說,I/O引腳分配是必須面對的眾多挑戰之一。 由于眾多原因,許多設計人員發表為大型FPGA器件和高級BGA封裝確定I/O引腳配置或布局方案越來越困難。 但是組合運用多種智能I/O規劃工具,能夠使引腳分配過程變得更輕松。

2019-06-03 08:06:00 2312

2312 FPGA的引腳交換

2020-01-20 17:53:00 2843

2843 FPGA System Planner解決了設計一個或多個工程師時遇到的挑戰PCB板上的更多大引腳數FPGA。

2021-03-16 16:56:15 24

24 在《STM32F103xCDE_DS_CH_V5(帶有引腳定義)》手冊中第18頁有這個100腳芯片的引腳分布,做STM32F103設計的常常用到。

2021-12-07 21:06:09 19

19 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2023-05-04 17:38:53 597

597 隨著 FPGA 的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的 硬件 引腳分配。 設計目標:ZU11EG FFVC1760封裝,掛載4組NVME

2023-12-14 15:45:01 194

194

電子發燒友App

電子發燒友App

評論