21世紀太空將成為國際軍事競爭的制高點。隨著技術的發展和科技的進步,航天電子設備對諸如現場可編程門陣列(Field Programmable Gate Array, FPGA)、數字信號處理器(Digital Signal Processor, DSP)等超大規模集成電路的依賴性越來越強。另一方面,宇宙中存在各種輻射射線,使得高性能芯片受太空射線影響而產生單粒子效應的概率大大提高,并且器件的集成度越高,單粒子效應的影響就越顯著,這嚴重影響和制約著航天電子儀器設備的正常工作。因此開發具有高速度、強抗輻射能力的集成電路技術對于發展我國航天技術及在輻射環境下工作的武器系統具有重要的意義。

一、 輻射環境

空間輻射主要來自宇宙射線,太陽耀斑和太陽風輻射。宇宙射線是指來自宇宙空間的高能量的粒子輻射,它們主要由高能質子和電子、X射線和γ射線、中子組成。這些高能量粒子能在局部沉積足夠量的電荷,不僅會造成邏輯翻轉還會對加工的芯片產生輻射損傷。國內外對航天故障的統計顯示,40%左右的故障源自太空輻射:1993年8月21日,美國有五顆衛星同時失效,原因是使用的同一批定時器芯片,均因宇宙射線輻照而失效;我國1994年發射的“風云二號”氣象衛星失去控制,也是由于一塊超大規模集成電路(Very Large Scale Integration, VLSI)芯片受到空間輻射影響而失效。2003年10月太陽風暴引起強烈的北極光,導致日本高級地球觀測衛星Midori-2等多顆衛星失靈。因此抗輻射技術是保障航天電子設備高可靠長壽運行的關鍵技術,是航天電子領域的研究重點和熱點。

二、 輻射效應概述

空間電子設備由于其所處的軌道不同,受到的輻射影響也不相同。總的來講,空間中的輻射效應主要有:總劑量效應(Total Ionizing Dose, TID)、位移損傷(Displacement Damage)、單粒子翻轉(Single Event Upset, SEU)、單粒子功能中斷(Single Event Functional Interrupt, SEFI)、單粒子燒毀(Single Event Burnout, SEB)、單粒子瞬態脈沖(Single Event Transient, SET)等。其中對FPGA影響較大的輻射效應主要是總劑量效應和單粒子效應。

隨著工藝水平的提高,FPGA內核電壓逐步降低,器件的輻射總劑量承受能力會越來越高,因此對采用先進工藝的高性能FPGA來講,總劑量效應影響會相對減小。但是隨著器件核電壓的降低、門數的劇增,單粒子翻轉、單粒子功能中斷和單粒子瞬態脈沖等一系列單粒子效應會越來越明顯。單粒子效應可以造成某個器件或者器件的某個區域較長時間甚至永久性的失效。因此FPGA的抗單粒子效應設計將極大程度上影響以FPGA為重要組成部分的航天電子設備的可靠性。

三、 單粒子效應的產生機理

單個粒子可能擊中硅片中的組合邏輯,也可能擊中時序邏輯。當一個帶電粒子擊中存儲單元的某一敏感節點時,如截止態晶體管的漏極時,其產生的瞬時電流脈沖能夠開啟對面晶體管的柵極。這種作用將產生存儲值的倒置,也就是存儲單元中的位翻轉。存儲單元有兩個穩定狀態,一個表示存儲“0”,而另一個表示存儲“1”。每種狀態都有兩個晶體管開啟和兩個晶體管關閉(SEU以漏極為目標)。存儲單元中的位翻轉發生在高能粒子引起電路中晶體管狀態翻轉的時刻,這種效應就是SEU效應,也是數字電路中需要重點關注的問題之一。

當一個帶電粒子沖擊組合邏輯塊時,同樣會產生瞬時電流脈沖,這種現象稱為單粒子瞬態脈沖效應(SET)。如果邏輯運行速度足夠快,以至于傳播了引入的瞬時電流脈沖,那么該SET將最終出現在第二個鎖存器的輸入端,并被認為是有效的信號。該SET是否會被當作真正數據而得到保存,取決于當時它到達的時間和時鐘下降沿或上升沿之間的關系。SET有轉變為SEU的可能。

基于靜態隨機訪問存儲器(Static Random Access Memorizer, SRAM)工藝的FPGA受空間高能粒子影響較大,其內部配置存儲器的邏輯狀態常常發生SEU。如果翻轉發生在RAM單元,可能導致數據錯誤或丟失;如果翻轉發生在邏輯功能區,可能導致航天器的功能中斷。因此,研究提高其抗單粒子效應能力的新方法是相當具有吸引力的工作。

四、 宇航應用中的芯片選擇

在實際宇航工程應用中,可選擇的芯片包括專用集成電路(Application Specific Integrated Circuit, ASIC)、以SRAM為基礎的FPGA和以反熔絲為基礎的FPGA。由于沒有一項技術是萬能的,設計人員需要針對特定的應用權衡取舍各種特性,從而得到最佳方案。

對于多數航天系統而言,ASIC是具有最高密度、最小重量和最低功耗的解決方案,但它卻缺乏FPGA的靈活性。除此之外,當把設計工具成本、校驗時間和非經常性工程費用(Non Recurring Engineering Cost, NRE)一并考慮之后,ASIC也是成本最高的解決方案。

以SRAM為基礎的FPGA可以現場編程,設計人員可在運行的航天器中重新配置邏輯電路。因此,SRAM型的FPGA成為多數設計人員在應用中的首選。不過這種靈活性所要付出的代價是:所有SRAM都易受高強度宇宙輻射的影響,易發生SEU。

對于大多數航天應用而言,以反熔絲為基礎的FPGA比ASIC和SRAM產品具有更多優勢。它擁有最低的FPGA能耗且具有高可靠性,采用耐輻射的反熔絲FPGA,設計人員可以免除ASIC設計中那些NRE成本和工程延誤風險,并且能享受只有FPGA才能提供的設計靈活性。此外,耐輻射反熔絲FPGA所需元件較少,因此能簡化板級設計、減輕重量和節省板卡的空間。

五、 抗單粒子效應的加固設計

1、 看門電路

FPGA設計中防止單粒子翻轉的硬件措施是采取看門電路,一旦發生單粒子翻轉導致的程序走飛,可通過狗咬信號對FPGA進行復位,從而達到自動恢復。此外,在FPGA內部狀態機設置狀態陷阱,使由于單粒子翻轉而產生的錯誤狀態可以自動恢復初始狀態,從而避免死鎖。目前此項技術已在中俄火星探測中嶄露頭角。

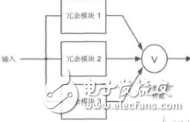

2、 三模冗余

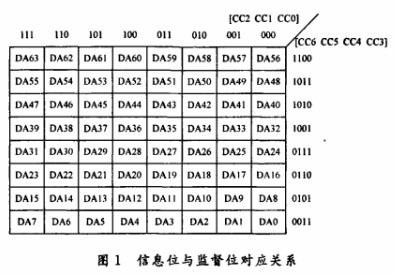

圖1為典型的基于硬件的三模冗余(Triple Module Redundancy ,TMR)邏輯原理示意圖,三個相同的模塊M0、M1和M2分別接收三個相同的輸入Input,產生的三個結果送至三選二表決邏輯。若有一個模塊發生SEU故障,另外兩個正常模塊的輸出可將故障模塊的輸出掩蔽,從而不會在表決器輸出產生差錯。此設計思想基于的假設前提為:任意兩個存儲單元的同一位不會在統一時間發生SEU 。

TMR的優點在于速度快,缺點是所需附加硬件資源多,一個受保護模塊的冗余至少需要備份兩次,從而造成功耗、體積及質量增大。

3、 刷寫

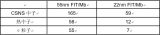

SRAM型FPGA上電時通過配置電路將配置存儲單元的內容寫入其中。當FPGA發生SEU效應時,存儲單元的“位翻轉”是一個常見的現象。由于翻轉的位置可能恰好不在FPGA編程布線區,故配置數據中的一個位(bit)的翻轉不一定直接導致FPGA發生功能故障。然而,如果不及時采取恢復措施,翻轉位數量會不斷積累,達到一定程度終究會導致功能錯誤。刷寫(Scrub)的直接功能就是阻止翻轉位的累積。由于FPGA是可重復編程的邏輯器件,可以通過周期性刷寫存儲單元中的內容,來減小存儲單元受到SEU而發生位翻轉的概率。從許多空間飛行器中搜集到的數據顯示:頻繁地刷寫可以直接提高存儲器的抗SEU能力;而且存儲單元刷寫的時間間隔越大,可靠性越低。

刷寫無需冗余的附加硬件邏輯資源,僅需適當增加自適應周期性刷新操作。因此,存儲區域的重新刷寫是目前國外FPGA和DSP空間應用時解決單粒子翻轉問題的最有效的方法,尤其是對未作防護的標準商用貨架器件(Commercial Off The Shelf, COTS)器件。但是,該方法只能解決時序邏輯的瞬時故障,不能解決由SEU導致的錯誤傳播效應。因此,刷寫技術僅適合片外FPGA配置存儲單元的抗SEU設計。

4、 結構設計

金字塔形體系結構設計基本概念

從結構設計上研究提高系統抗單粒子效應能力的方法是目前國內外正在研究的重點。設計中常采用金字塔形體系結構,金字塔形體系結構的含義是指:高等級、高可靠性的器件實施對中等級、中可靠性的器件的狀態監控,中等級、中等可靠性的器件實施對低等級、低可靠性器件的監控,依此類推,構成一個金字塔形的層層監控的可靠性體系結構。

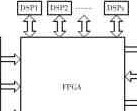

Actel宇航級FPGA是國內外星載設備上普遍使用的高可靠單元(High Reliable Unit, HRU),它位于信號處理平臺的金字塔塔尖,負責系統故障的診斷、控制、調配和重構,是系統的大腦。由于Actel的宇航級FPGA的規模較小,不適合進行復雜的信號處理,因此它必須結合具有自主重構能力、高性能的FPGA或DSP才能完成復雜的信號處理,如測控、通信、數據壓縮等。處于第二層結構的是SRAM型FPGA,它可以是軍品級、工業級,甚至商業級器件,它完成多通道高速并行信號處理、DSP陣列的數據管理和待處理數據流向的控制。第三層是多個地位平等的高性能DSP,它們構成了一個具有高速數據處理能力的信號處理網絡。

配置存儲器的回讀和重配置

Actel高可靠性的反熔絲FPGA負責從非易失大容量存儲器中讀取Xilinx FPGA的配置數據并對其進行配置,然后在系統運行期間,對最容易受輻射效應影響的配置存儲器按列進行讀操作,回讀出數百萬配置鎖存器中的FPGA配置信息后,將其與原始配置文件進行逐位比對。如果有不同,則說明可能有單粒子翻轉,且能同時準確定位到時哪一幀數據的哪一位發生了翻轉,從而對出現錯誤的列進行局部重配置。

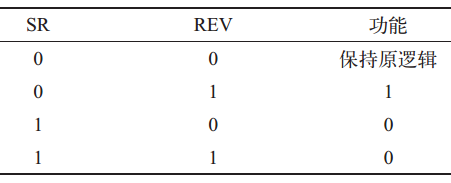

FPGA狀態的分析與重配置

在金字塔形體系結構設計基本概念的基礎上,Actel高可靠性的反熔絲FPGA擔任系統的監控模塊,通過Xilinx FPGA內部的功能模塊提供的狀態信息,對當前FPGA功能的正常性做出分析與判斷。這些狀態信號是配合內部程序產生的一種具有一定寬度的脈沖串,如果FPGA檢測到存儲區發生SEU或者運算單元發生故障,將停止產生狀態信號;如果某些故障引起FPGA程序“跑飛”或“死機”,此狀態信號也將自行終止。根據評估結果,如果發生輻射失效的概率足夠大時,Actel FPGA將對Xilinx FPGA進行復位、重配置或者局部重配置,以恢復其正常功能。

5、分區設計

由單粒子翻轉引發的單粒子效應故障具有伴隨性,其傳遞范圍一般局限在幾何相鄰或者有邏輯關聯的功能模塊之間,因此,如果把邏輯關系聯系緊密的功能模塊按照區域放在一起,那么當單個粒子入射引起配置存儲器單粒子翻轉時,故障空間和邏輯擴散范圍就將局限于該區域。最重要的是,在某個區域的功能模塊出現故障的時候,采用這種分區設計措施可以在不影響其他區域正常工作的情況下,對該區域的配置存儲器進行快速動態重配置。

21世紀的國防已經開始向遙遠的太空延伸,空間必將成為繼陸、海、空之外的第四維戰場,空間應用、空間攻防能力必將成為未來國防空間威懾力的重要籌碼。易受輻射干擾的航空電子儀器能否高速可靠地運行,影響著未來空間國防的決策效率。而以FPGA為代表的超大規模集成電路依靠其強大的信號處理能力和優越的接口性能,成為航空電子儀器的重要組成部分,它們在航空航天工程中的廣泛應用勢在必行,其抗輻射加固也迫在眉睫。FPGA在航空電子應用中的加固設計可以直接應用于航空電子儀器設備,從而增強我國宇航級高性能數字器件的應用能力,提高我國宇航領域的整體研究水平。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論