· 新思科技Custom Design Platform為三星7LPP工藝技術提供經認證的工具、PDK、仿真模型、運行集(runsets)以及定制參考流程。

· 新思科技Custom

2018-07-18 11:46:35 7228

7228 達成合作,通過采用新思科技業界領先的仿真工具Saber為DC/DC IC和μModule?(微型模塊)穩壓器提供模型庫。Saber作為新思科技虛擬原型解決方案的一部分,其系統級仿真軟件中的新模型庫能夠助力動力總成開發者在電動汽車、儀器設備和超級計算機等產品上快速準確地進行多域仿真,加速設計進

2022-05-24 10:47:43 1483

1483

臺積電0.18工藝電源電壓分別是多少?是1.8v跟3.3v嗎?

2021-06-25 06:32:37

有機會“獨吞”A7代工訂單。 臺積電作為全球規模最大的專業集成電路制造公司,其技術優勢的領先,在業界可謂屈指可數。臺積電積極開發20納米制程,花旗環球證券指出,在技術領先MAX3232EUE+T優勢下,未來1

2012-09-27 16:48:11

采用0.13um的混合工藝 模擬設計中用到的MOS的柵長選擇就是0.13um嗎? / C5 @, o6 U8 I% q! X而如果采用0.18um的混合工藝 模擬設計中用到的MOS的柵長選擇就是0.18um嗎?

2012-01-12 16:33:54

本文闡述關于模擬設計中噪聲分析的11個由來已久的誤區。

2021-03-09 08:27:51

模擬設計的100條圣經

2021-02-25 07:24:42

HarmonyOS分布式——跨設備遷移

2021-06-26 14:34:39

說明:此Demo用于跨設備遷移視頻內容。您可以方便地跨設備遷移視頻內容,然后在源設備遠程控制、操作遠端設備視頻內容。效果圖:完整代碼地址:https://gitee.com/jltfcloudcn/jump_to/tree/feature/DistributedVideoCodelab

2022-07-05 10:24:59

圖:如圖3所示。應注意的是,所有準備工作都應依照產品程序中的定 義來開展。 ③貼片機生產基本工藝流程:圖4提供了貼片生產的基本工藝流程,在實際生產環境中的工藝流程(或 說貼片設備的動作流程)比這要復雜

2018-08-31 14:55:23

據外媒報道,預計臺積電將獲得高通新一代電源管理芯片(PWM IC)70%至80%的訂單。高通前一代電源管理芯片是由中芯國際(SMIC)生產的,后者在其8英寸晶圓廠使用0.18至0.153微米工藝來生

2017-09-27 09:13:24

模擬/數字混合系統設計的數字工程師、學生、教師及應用工程人員。本書是一本有用的參考資料,既可以幫助讀者完成數字系統中的模擬設計,也可以作為掌握許多模擬電子方面重要內容的指導手冊。內容簡介 本書為那些

2017-12-14 17:49:51

【招聘】射頻/模擬、ASIC設計/驗證、系統、模擬設計等 射頻集成電路工程師(TRX 方向)-BJ 射頻/模擬集成電路工程師(RF/Analog IC Engineer)-BJ 射頻IC工程師

2017-03-03 14:54:37

流程。公司在項目初期就與客戶充分接觸,為客戶提供系統整體解決方案,從產品功能定義、市場競爭力分析、工藝選擇到代工廠選取以及知識產權模塊的授權都深入參與,為客戶提供精準可靠的分析數據和全面的方案報告,幫助

2016-01-07 11:03:36

| 產品解讀7月26日(下周二)15:00,電子發燒友聯合先積集成將舉辦一場線上技術交流會,先積集成資深大咖將針對公司產品路線布局及產品特點做詳細解讀,致力于提供更專業的模擬芯片解決方案。特邀嘉賓資深

2022-07-25 18:22:32

消費類產品中日益增長的模擬器件數量、當今的設計規模以及先進工藝節點所面臨的愈加復雜的制造約束,使得模擬設計領域對自動化設計工具的企盼更加迫切。 自動化設計工具的目標是使模擬版圖設計人員能夠簡單自動

2019-07-08 06:00:51

關于黑孔化工藝流程和工藝說明,看完你就懂了

2021-04-23 06:42:18

各類常用工藝庫臺積電,中芯國際,華潤上華

2015-12-17 19:52:34

,負責管理所有下屬公司、市場和行業的各個開發階段的項目,這是一項艱巨任務。為了應對這一挑戰,三星SDS將項目管理系統、流程、工具和解決方案有效組合在一起,為創建高質量、可信軟件提供支持。部署開源軟件

2023-03-02 14:20:49

Kochpatcharin表示:“臺積公司與新思科技等開放創新平臺(OIP)合作伙伴緊密合作,助力我們的客戶在執行定制及模擬模塊的工藝制程設計遷移時,提高生產效率并加快設計收斂。現在,通過全新的新思科技AI驅動型模擬設

2023-04-03 16:03:26

主導地位,因此可以相對確定地控制價格。目前臺積電訂單已排到2022年年底,訂單數量過多也在無形中影響了代工價格。臺積電漲價20%,意味著什么?意味著小公司無力支付芯片代工費用。受晶圓代工漲價影響,如今

2021-09-02 09:44:44

晶體管管芯的工藝流程?光刻的工藝流程?pcb制版工藝流程?薄膜制備工藝流程?求大佬解答

2019-05-26 21:16:27

樣板貼片的工藝流程是什么

2021-04-26 06:43:58

一個跨阻放大器LTC6268的增益帶寬積為500毫赫茲。

詳細參數表內寫明GBW=500毫赫茲實在條件f=10MHz下得到。

這一參數明顯與通用運算放大器的增益帶寬積不同。

例如一個

2023-11-17 06:38:58

的IDM們,也正在采取“輕晶圓廠”的模式。快速轉向SoC的壓力使得這些公司更樂于接受采用外部模擬IP的做法,以此滿足緊迫的時間期限。不過,這些公司仍在繼續尋求純粹內部開發的模擬設計,針對自己的工藝

2019-05-13 07:00:04

芯片生產工藝流程是怎樣的?

2021-06-08 06:49:47

設備聯網步驟和接入流程。二、虛擬設備的特點?主要有以下特點:1、可模擬要開發或正在開發的智能硬件2、通過虛擬設備模擬真實設備上報數據的行為,可以快速驗證接口功能的開發。3、用您開發的app或 下載

2017-02-16 16:55:04

實現產品與云端通訊呢?如果你不想折騰硬件產品,就想知道設備和機智云互聯的原理,同樣OK。機智云新推出的虛擬設備,可以模擬真實設備上報數據的行為,可以快速驗證接口功能的開發。使用指南如下:step1:在

2017-02-23 16:43:25

的必經前提步驟,而先進的制成工藝可以更好的提高中央處理器的性能,并降低處理器的功耗,另外還可以節省處理器的生產成本。 “芯片門”讓臺積電備受矚目 2015年12月份由臺積電舉辦的第十五屆供應鏈管理論

2016-01-25 09:38:11

DevEco Studio支持打開兩個遠程模擬器,演示跨設備遷移嗎?

2022-06-07 10:02:55

辦公。本篇 Codelab 文檔,我們通過模擬不同設備間協同的郵件編輯來做一個簡單的演示,如下圖,我們可以通過遷移按鈕完成任務的跨設備遷移,并通過附件按鈕調用跨設備的圖片。

2022-03-25 16:59:38

陶瓷(LTCC)多層基材的工藝技術已達到該要求。 現在,新設計的芯片內部電極的制造工藝對位置控制更為精確,進而生產出高Q值的0402和0603系列中的積層電感MLG0402Q和MLG0603P系列。積

2019-05-30 06:00:38

中芯國際和新思科技攜手推出參考設計流程4.0

全球領先的半導體設計、驗證和制造軟件及知識產權(IP)供應商新思科技公司與中國內地最大的芯片代工企業中芯國際集成電

2009-06-29 07:43:54 369

369 Exar選擇微捷碼Titan ADX來加速模擬設計

芯片設計解決方案供應商微捷碼(Magma(r))設計自動化有限公司(納斯達克代碼:LAVA)日前宣布,Exar公司已

2009-12-10 09:48:02 718

718 微捷碼(Magma)設計自動化有限公司日前宣布,提供免費試用版Titan混合信號平臺和模擬設計加速器的下載。這是“Titan Up!”計劃下一階段的內容,旨在為模擬設計師提供模擬和混合信

2010-06-22 09:36:50 936

936 新思科技完整實施流程助力英飛凌在中國成功實現首款40納米3G基帶處理器芯片設計和一次流片成功

中國北京和西安,2010年8月9日—全

2010-08-11 14:39:39 510

510 微捷碼(Magma)設計自動化有限公司日前宣布,Titan模擬設計加速器(Titan ADX)已為富士通半導體有限公司(Fujitsu Semiconductor)所采用

2011-11-23 09:11:43 680

680 嵌入式系統中的模擬設計 英文版,好東西,喜歡的朋友可以下載來學習。

2016-01-18 14:55:52 0

0 國內搞模擬設計可能缺乏的是傳承,感興趣的小伙伴們可以瞧一瞧。

2016-09-18 17:15:05 0

0 精密模擬設計中的噪聲分析

2017-01-14 15:09:16 17

17 放大器和轉換器模擬設計技巧

2017-09-15 17:01:44 29

29 TI各種模擬設計工具介紹

2017-10-16 12:56:45 7

7 本手冊描述如何使用VieloSo模擬設計環境來模擬模擬設計。VieloSo模擬設計環境被記錄在一系列在線手冊中。下面的文件給你更多的信息。 FieloSo高級分析工具用戶指南提供有關蒙特卡洛、優化和統計分析的信息。

2018-09-20 08:00:00 0

0 采用新思科技Sentaurus、Process Explorer、StarRC、SiliconSmart、PrimeTime和IC Compiler II,DTCO方法學降低了先進半導體工藝開發的成本,并加快了上市速度。

2018-09-21 11:53:52 7913

7913 近日,全球知名的EDA工具廠商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得了重大突破,這將為三星后續5nm、4nm、3nm工藝的量產和良品率的提升奠定堅實基礎。

2019-07-09 17:13:48 4225

4225 全球知名的EDA工具廠商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得了重大突破

2019-07-11 14:49:47 3325

3325 微捷碼(Magma)設計自動化有限公司日前宣布,Titan模擬設計加速器(TitanADX)已為富士通半導體有限公司(FujitsuSemiconductor)所采用。

2019-12-20 15:18:49 1261

1261 本視頻介紹了采用PSoC Creator進行模擬設計的各種技巧和注意事項。

2020-07-01 12:16:00 1888

1888 本視頻介紹了采用PSoC Creator進行模擬設計的各種技巧和注意事項。

2020-07-01 12:41:00 2668

2668 本視頻介紹了采用PSoC Creator進行模擬設計的各種技巧和注意事項。

2020-07-01 12:04:00 3262

3262 ,可實現可靠的簽核和設計實時分析 新思科技(Synopsys)近日宣布與TSMC合作,為先進封裝解決方案提供經認證的設計流程。這些解決方案使用新思科技3DIC Compiler產品,進行CoWoS-S

2020-10-14 11:11:21 2099

2099 新思科技與三星基于Fusion Design Platform開展合作,充分釋放三星在最先進節點工藝的優勢 經過認證的流程為開發者提供了一整套針對時序和提取的業界領先數字實現和簽核解決方案 新思科

2021-01-13 16:01:18 1903

1903 的“芯云智聯 擎領未來 云上芯片設計技術沙龍”在西安成功舉辦。 紫光國芯設計服務部總監王成偉在會上分享了《先進工藝下的全流程芯片設計服務》。王成偉介紹,先進工藝SoC芯片研發面臨著研發難度高、驗證和測試覆蓋率要求高、物理驗證規則

2021-04-29 09:44:11 3264

3264 雙方共同推出的工藝設計套件和經認證參考流程可加速高性能汽車、邊緣人工智能和5G SoC的開發 全球半導體制造領先企業GlobalFoundries(GF)聯合新思科技(Synopsys)近日宣布

2021-11-17 14:38:41 1609

1609 解決方案能夠實現全面的數據可視化和AI自動優化設計,助力提高先進節點的芯片設計生產力。該解決方案將為所有開發者提供實時、統一、360度視圖,以加快決策過程,通過更深入地了解運行、設計、項目之間的趨勢來加強芯片的開發協作。

2022-06-02 16:09:44 2433

2433 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 4800

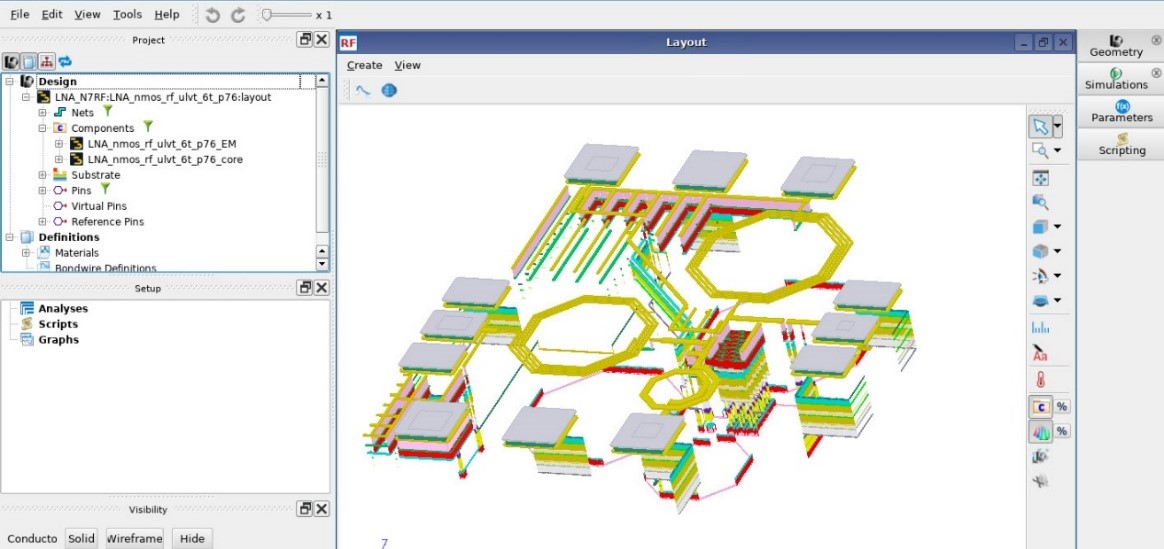

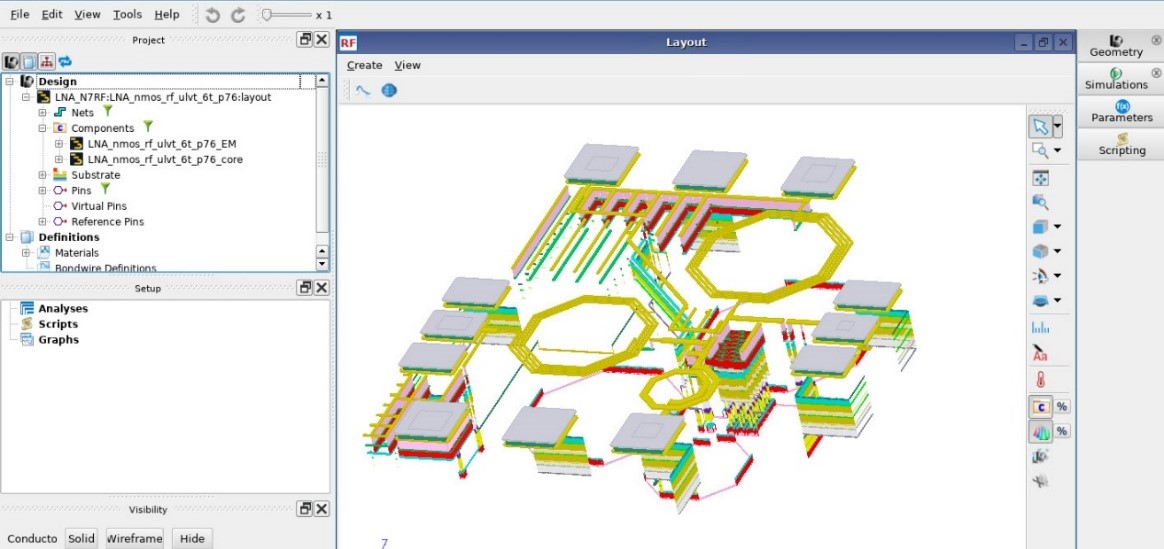

4800 新思科技(Synopsys)近日推出面向臺積公司N6RF工藝的全新射頻設計流程,以滿足日益復雜的射頻集成電路設計需求。

2022-06-24 14:30:13 868

868 來源:是德科技 PathWave RFPro 與新思科技定制化編譯器相輔相成,可提供無線晶片設計工作流程所需的整合式電磁模擬工具 是德科技(Keysight Technologies Inc.

2022-06-27 14:41:38 667

667

新思科技數字和定制設計流程獲得臺積公司的N3E和N4P工藝認證,并已推出面向該工藝的廣泛IP核組合。

2022-07-12 11:10:51 877

877 中國上海,2022 年 10 月 27 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence 數字和定制/模擬設計流程已獲得臺積電最新 N4P 和 N3E

2022-10-27 11:01:37 940

940 ,納斯達克股票代碼:SNPS )近日宣布,得益于與臺積公司的長期合作,新思科技針對臺積公司N3E工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的

2022-11-08 13:37:19 1358

1358 工藝技術取得了多項關鍵成就,共同推動先進工藝節點的持續創新。新思科技經產品驗證的數字和定制設計流程已在臺積公司N3E工藝上獲得認證。此外,該流程和新思科技廣泛的基礎IP、接口IP組合已經在臺積公司N3E工藝上實現了多項成功流片,助力合

2022-11-10 11:15:22 502

502 為滿足5G/6G SoC對性能和功耗的嚴苛需求,新思科技(Synopsys,Inc.,納斯達克股票代碼:SNPS)、Ansys和是德科技近日宣布,推出針對臺積公司16納米精簡型工藝技術(16FFC

2022-11-16 16:24:19 570

570 工藝技術的2D/2.5D/3D多裸晶芯片系統。基于與臺積公司在3DFabric?技術和3Dblox?標準中的合作,新思科技提供了一系列全面的、系統級的、經過產品驗證的解決方案,助力共同客戶能夠滿足復雜的多裸晶芯片系統對于功耗和性能的嚴苛要求。

2022-11-16 16:25:43 877

877 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的節點到節點設計遷移流程,能兼容所有的臺積電先進節點

2023-05-06 15:02:15 801

801 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發

2023-05-09 10:09:23 708

708 為了不斷滿足新一代系統單晶片(SoC) 的嚴格設計目標,新思科技在臺積電最先進的 N2 製程中提供數位與客製化設計 EDA 流程。相較於N3E 製程,臺積公司N2 製程採用奈米片(nanosheet

2023-05-11 19:02:35 1996

1996 針對臺積公司16FFC的79GHz毫米波射頻設計流程加速自動駕駛系統中射頻集成電路的開發。 新思科技、Ansys和是德科技近日宣布,推出針對臺積公司16納米精簡型工藝技術(16FFC)的全新

2023-05-17 05:45:01 232

232

股票代碼:SNPS)近日宣布,攜手臺積公司和Ansys持續加強多裸晶芯片系統設計與制造方面的合作,助力加速異構芯片集成以實現下一階段的系統可擴展性和功能。得益于與臺積公司在3DFabric?技術和3Dblox?標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技

2023-05-17 15:43:06 229

229 在3DFabric?技術和3Dblox?標準中的合作,新思科技能夠為臺積公司先進的7納米、5納米和3納米工藝技術上的多裸晶芯片系統設計,提供業界領先的全方位EDA和IP解決方案。臺積公司先進工藝技術集成

2023-05-18 16:04:08 790

790 Packet Tracer 是由Cisco公司發布的一個輔助學習工具,為學習思科網絡課程的初學者去設計、配置、排除網絡故障提供了網絡模擬環境。

2023-06-07 10:03:11 2226

2226

面向三星8LPU、SF5 (A)、SF4 (A)和SF3工藝的新思科技接口和基礎IP,加速先進SoC設計的成功之路 摘要: 新思科技接口IP適用于USB、PCI Express、112G以太網

2023-06-30 13:40:14 341

341 內容提要 1 輕松實現節點到節點的設計和 layout 遷移 2 將定制/模擬設計遷移速度提升 2 倍 3 Cadence Virtuoso Studio 針對所有 Samsung Foundry

2023-07-04 10:10:01 471

471 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 的 Cadence 流程,以十足把握交付各類 HPC 及消費電子應用 中國上海,2023 年 7 月 14 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布其數字和定制/模擬

2023-07-14 12:50:02 381

381

存儲器、TCAM和GPIO,可以在各先進節點上提供行業領先的功耗、性能和面積(PPA) 新思科技車規級IP集成到三星的工藝中,有助于確保ADAS、動力總成和雷達SoC的長期運行并提高可靠性 三星工藝中集成了廣泛的IP組合,并在新思科技經過認證的數字和定制設計流程的加持下,共同加速流片成功

2023-07-26 17:40:03 255

255 技的解決方案可在英特爾代工服務提供的制程工藝上實現安全且先進的微電子技術開發 新思科技(Synopsys)近日宣布,其搭載了Synopsys.ai全棧式AI驅動型EDA解決方案的數字和定制設計流程已經通過英特爾代工服務(IFS)的Intel 16制程工藝認證,以助力簡化功耗和空間受限型應用

2023-08-07 18:45:03 334

334 基于臺積公司N3E工藝技術的新思科技IP能夠為希望降低集成風險并加快首次流片成功的芯片制造商建立競爭優勢

2023-08-24 17:37:47 657

657 新思科技經認證的多裸晶芯片系統設計參考流程和安全的Die-to-Die IP解決方案,加速了三星SF 5/4/3工藝和I-Cube及X-Cube技術的設計和流片成功。 新思科技3DIC

2023-09-14 09:38:28 839

839 流程,能兼容所有的 TSMC(臺積電)先進節點,包括最新的 N3E 和 N2 工藝技術。 這款生成式設計遷移流程由 Cadence 和 TSMC 共同開發,旨在實現定制和模擬 IC 設計在 TSMC

2023-09-27 10:10:04 301

301 N2納米片工藝的數字設計流程正在實現多次流片,而模擬設計流程已在多個設計啟動中采用。預計將于2024年提供樣品。 這是在領先工藝上同時提供模擬設計流程和庫與數字設計流程和庫的重大舉措,特別是從FINFET晶體管轉向納米片、全柵(GAA)器件之際。由此需要新的設計和

2023-10-08 16:49:24 285

285 的生產力 基于 AI 驅動的 Virtuoso Studio 的定制/模擬流程支持電路優化,功能經過增強,可將設計遷移吞吐量提升 3 倍 雙方的共同客戶正在積極使用 N2 PDK 來開發 AI、大規模計算

2023-10-10 16:05:04 270

270 。 Synopsys.ai? EDA解決方案中的模擬設計遷移流程可實現臺積公司跨工藝節點的快速設計遷移。 新思科技接口IP和基礎IP的廣泛產品組合正在開發中,將助力縮短設計周期并降低集成風險。 ? 加利福尼亞州桑尼維爾, 2023 年 10 月 18 日 – 新思科技(Synopsys, I

2023-10-19 11:44:22 104

104 新思科技近日宣布,其數字和定制/模擬設計流程已通過臺積公司N2工藝技術認證,能夠幫助采用先進工藝節點的SoC實現更快、更高質量的交付。新思科技這兩類芯片設計流程的發展勢頭強勁,其中數字設計流程已實現

2023-10-24 16:42:06 475

475 摘要: 全新參考流程針對臺積公司 N4PRF 工藝打造,提供開放、高效的射頻設計解決方案。 業界領先的電磁仿真工具將提升WiFi-7系統的性能和功耗效率。 集成的設計流程提升了開發者的生產率,提高了

2023-10-30 16:13:05 106

106 計 新思科技攜手Ansys 和 Keysight 共同推出全新射頻設計參考流程,能夠為現代射頻集成電路設計提供完整解決方案 新思科技(Synopsys)近日宣布,其模擬設計遷移流程已應用于臺積公司N4P、N3E 和 N2 在內的多項先進工藝。作為新思科技定制設計系列產品

2023-11-09 10:59:40 436

436 (RF)設計和接口IP五項大獎。新思科技與臺積公司長期穩固合作,持續提供經過驗證的解決方案,包括由Synopsys.ai全棧式AI驅動型EDA解決方案支持的認證設計流程,幫助共同客戶加快創新型人工智能

2023-11-14 10:31:46 376

376 多個獎項高度認可新思科技在推動先進工藝硅片成功和技術創新領導方面所做出的卓越貢獻 摘要 : 新思科技全新數字與模擬設計流程認證針對臺積公司N2和N3P工藝可提供經驗證的功耗、性能和面積(PPA)結果

2023-11-14 14:18:45 120

120 電子發燒友網站提供《模擬設計中噪聲分析的11個誤區.pdf》資料免費下載

2023-11-28 10:25:19 0

0 ?芯片制造商與EDA解決方案和廣泛的IP組合緊密合作, 能夠提升產品性能并加快上市時間 摘要: 新思科技數字和模擬EDA流程經過認證和優化,針對Intel 18A工藝實現功耗、性能和面積目標

2024-03-05 10:16:59 84

84 新思科技數字和模擬 EDA 流程經過認證和優化,針對Intel 18A工藝實現功耗、性能和面積目標

2024-03-05 17:23:44 238

238 近日,新思科技與英特爾宣布深化合作,共同加速先進芯片設計的步伐。據悉,新思科技的人工智能驅動的數字和模擬設計流程已經成功通過英特爾代工的Intel 18A工藝認證,這一突破性的進展標志著雙方在芯片設計領域的合作邁上了新臺階。

2024-03-06 10:33:59 180

180

電子發燒友App

電子發燒友App

評論