[導讀]?賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現有的FPGA中沒有一款同時包含這四種資源(見表1)。

這四大類中的每一種都針對特定的應用。例如,數字時鐘管理器(DCM)適用于實現延遲鎖相環(DLL)、數字頻率綜合器、數字移相器或數字頻譜擴展器。DCM還是鏡像、發送或再緩沖時鐘信號的理想選擇。另一種時鐘資源相位匹配時鐘分頻器(PMCD)可用于實現相位匹配分配時鐘或相位匹配延遲時鐘。

鎖相環(PLL)和混合模式時鐘管理器(MMCM)處理的工作有許多是相同的,比如頻率綜合、內外部時鐘抖動濾波、時鐘去歪斜等。這兩種資源也可用于鏡像、發送或再緩沖時鐘信號。

在深思設計實現細節時,把這些通常用法記在心里,有助于理清時鐘選擇的思路。對于長期產品發展規劃而言,在制定合適的時鐘策略時,應考慮各個器件系列之間的兼容性。下面讓我們深入了解一下這些時鐘資源。

您可以使用DCM將時鐘源的輸入時鐘信號相乘,生成高頻率時鐘信號。與此類似,可以將來自高頻率時鐘源的輸入時鐘信號相除,生成低頻率時鐘信號。

數字時鐘管理器

顧名思義,數字時鐘管理器(DCM)是一種用于管理時鐘架構并有助于時鐘信號成形和操控的模塊。DCM內含一個延遲鎖相環(DLL),可根據輸入時鐘信號,去除DCM輸出時鐘信號的歪斜,從而避免時鐘分配延遲。

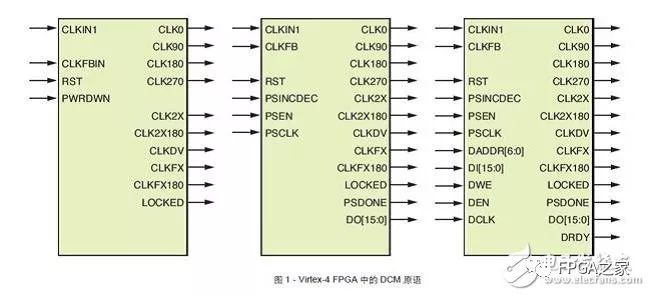

DLL 內含一個延遲元件和控制邏輯鏈路。延遲元件的輸出是輸入時鐘延遲所得。延遲時間取決于延遲元件在延遲鏈路中的位置。這種延遲體現為針對原始時鐘的相位改變或相移,這就是所謂的“數字相移”。圖1所示的即為Virtex-4器件中的典型DCM模塊。根據Virtex-4FPGA用戶指南(UG070,2.6 版本)的介紹,Virtex-4中有三種不同的DCM原語。

一般來說,DLL與PLL類似。但與PLL不同的是DLL不含壓控振蕩器(VCO)。PLL會一直存儲相位和頻率信息,而DLL只存儲相位信息。因此,DLL略比PLL穩定。DLL和PLL這兩種類型都可以使用模擬和數字技術設計,或者混合兩種技術設計。但賽靈思器件中的DCM采用全數字化設計。

由于DCM可以在時鐘路徑上引入延遲,比如您就可使用DCM可以精確地為DRAM生成行和列訪問選通信號的時序。與此類似,數據總線上的各個數據位可以在不同的時間到達。為了正確對數據位采樣,接收端的時鐘信號必須適當地與所有數據位的到達保持同步。如果接收器使用發射時鐘,可能會要求延遲從發送端到接收端的時鐘信號。

有時設計可能需要一個更高的時鐘頻率來運行FPGA上的邏輯。但是,只有低頻率輸出的時鐘源可以用。此時可以使用DCM將時鐘源的輸入時鐘信號相乘,生成高頻率時鐘信號。與此類似,可以將來自高頻率時鐘源的輸入時鐘信號相除,生成低頻率時鐘信號。這種技術稱為“數字頻率綜合”。

設計人員使用擴頻時鐘并通過調制時鐘信號來降低時鐘信號的峰值電磁輻射。未經調制的時鐘信號的峰值會產生高電磁輻射。但經調制后,電磁輻射被擴展到一系列時鐘頻率上,從而降低了所有頻點的輻射。一般來說,如果需要滿足一定的最大電磁輻射要求和在FPGA上執行高速處理的時候(比如說通信系統中接收器使用的解串器),就需要使用擴頻時鐘。因此,FPGA中的DCM將乘以輸入擴頻時鐘信號,在內部生成高頻時鐘信號。DCM的輸出必須準確地跟隨擴頻時鐘,以保持相位和頻率對齊并更新去歪斜和相移。DCM相位和頻率對齊的惡化會降低接收器的歪斜裕量。

建立時鐘的鏡像需要將時鐘信號送出FPGA器件,然后又將它接收回來。可以使用這種方法為多種器件的板級時鐘信號去歪斜。DCM能夠把時鐘信號從FPGA發送到另一個器件。這是因為FPGA的輸入時鐘信號不能直接路由到輸出引腳,沒有這樣的路由路徑可用。如果僅需要發送時鐘信號,那么使用DCM將時鐘信號發送到輸出引腳,可以確保信號的保真度。另外也可選擇在時鐘信號發送之前,將DCM輸出連接到ODDR觸發器。當然也可以選擇不使用DCM,僅使用ODDR 來發送時鐘信號。往往時鐘驅動器需要將時鐘信號驅動到設計的多個組件。這會增大時鐘驅動器的負荷,導致出現時鐘歪斜及其它問題。在這種情況下,需要采用時鐘緩沖來平衡負載。

時鐘可以連接到FPGA上的一系列邏輯塊上。為確保時鐘信號在遠離時鐘源的寄存器上有合適的上升和下降時間(從而將輸入輸出時延控制在允許的范圍內),需要在時鐘驅動器和負載之間插入時鐘緩沖器。DCM可用作時鐘輸入引腳和邏輯塊之間的時鐘緩沖器。

最后,還可以使用DCM將輸入時鐘信號轉換為差分I/O標準信號。例如,DCM可以將輸入的LVTTL時鐘信號轉換為LVDS時鐘信號發送出去。

相位匹配時鐘分頻器

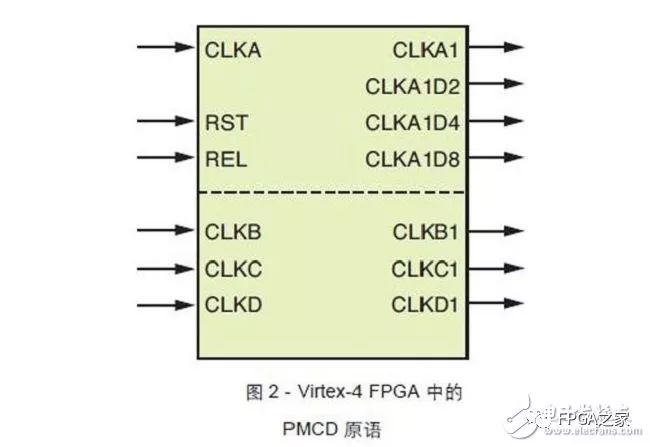

設計人員可使用相位匹配時鐘分頻器(PMCD)來生成相位匹配的分頻輸入時鐘信號。這與分頻時鐘的DCM頻率綜合相似。PMCD還能生成設計中相位匹配但有延遲的時鐘信號。在后一種情況下,PCMD能夠在輸入時鐘信號和其它PMCD輸入時鐘信號之間保持邊緣對齊、相位關系和歪斜。與DCM不同的是,在分頻器的值可配置的情況下,賽靈思器件中現有的PMCD生成的時鐘信號僅按2、4和8分頻。這意味著PMCD生成的時鐘信號的頻率是輸入時鐘信號的1/2、1/4和1/8。在如Virtex-4FPGA這樣的賽靈思器件中,PMCD緊鄰 DCM并與其位于同一列上。每一列有兩個PMCD-DCM對。因此DCM的輸出可以驅動PMCD的輸入。

由于DCM還負責處理去歪斜,因此只要不需要去歪斜時鐘,設計人員就可以使用不帶DCM的PMCD。通過專用引腳,還可以把一列中的兩個PMCD連接起來。圖2是 Virtex-4器件中的PMCD原語。詳細內容請參閱Virtex-4FPGA用戶指南(UG070,2.6版本)。

混合模式時鐘管理器

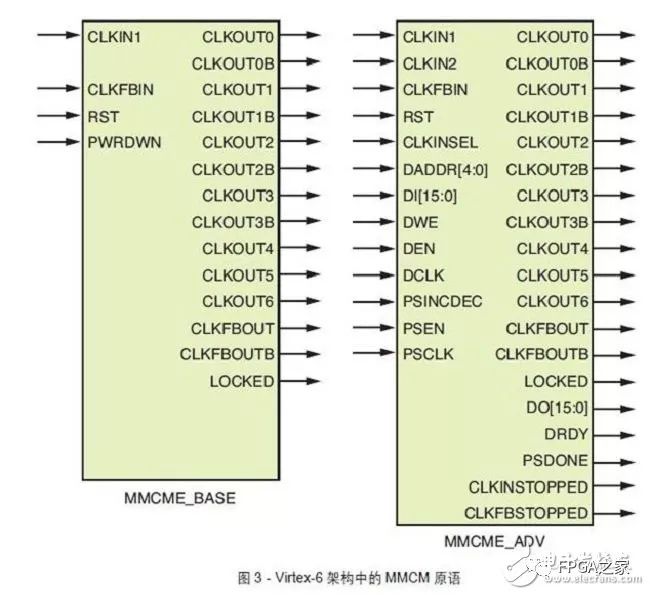

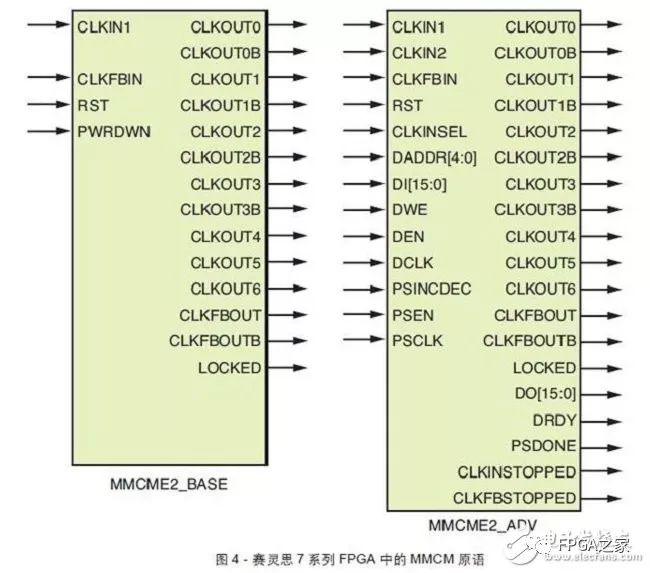

另一種類型的時鐘資源——混合模式時鐘管理器(MMCM),用于在與給定輸入時鐘有設定的相位和頻率關系的情況下,生成不同的時鐘信號。不過與DCM不同是,MMCM使用PLL來完成這一工作。Virtex-6FPGA中的時鐘管理模塊(CMT)有兩個MMCM,而Virtex-7中的CMT有一個 MMCM和一個PLL。Virtex-6器件中的MMCM沒有擴頻功能,因此輸入時鐘信號上的擴頻不會被濾波,將直接被傳送給MMCM輸出時鐘。但 Virtex-7FPGA的MMCM卻有擴頻功能。

Virtex-6FPGA中的MMCM要求插入一個校準電路,以便在用戶復位或用戶斷電后確保MMCM正確運行。賽靈思ISE設計套件11.5版本及更高版本能夠在設計的MAP階段自動插入必要的校準電路。若使用賽靈思ISE 的更早版本,則需要使用賽靈思技術支持部提供的設計文件手動插入校準電路。最后需要注意的是,在本移植該設計,以便用ISE11.5版本或更高版本實現時,必須手動移除校準電路,或通過適當設置每個MMCM上的綜合屬性,禁用自動插入功能。詳細介紹請參閱賽靈思答復記錄AR#33849。

對7系列器件中的MMCM就不存在這樣的問題,因為這些FPGA只得到ISE13.1版本和更高版本以及新型Vivado設計套件的支持。Virtex-6系列中提供的MMCM間專用走線可便于用戶將全局時鐘資源用于設計的其余部分。

圖 3顯示了Virtex-6FPGA中的MMCM原語。各個端口的詳細介紹請參閱Virtex-6FPGA時鐘資源用戶指南(UG362,2.1版本)。圖 4顯示了賽靈思7系列FPGA中的MMCM原語,有關詳細介紹請參閱7系列FPGA時鐘資源用戶指南(UG472,1.5版本)。

鎖相環

設計人員使用鎖相環(PLL)主要用于頻率綜合。使用一個PLL可以從一個輸入時鐘信號生成多個時鐘信號。結合DCM使用,還可以用作抖動濾波器。Spartan-6、Virtex-5和7系列FPGA中都提供有PLL。Spartan-6和 Virtex-5中均有專門的“DCM到PLL”和“PLL到DCM”走線。Spartan-6和Virtex-5中的PLL輸出是非擴頻的。對這兩種器件而言,如果設計使用多個不同時鐘,都可以用PLL替代DCM。PLL時鐘輸出具有寬范的配置范圍,而DCM的輸出是預定的,不可配置。PLL和DCM的選擇還是取決于設計的要求。不過如果相移是必需的,就應該明確地選擇DCM。

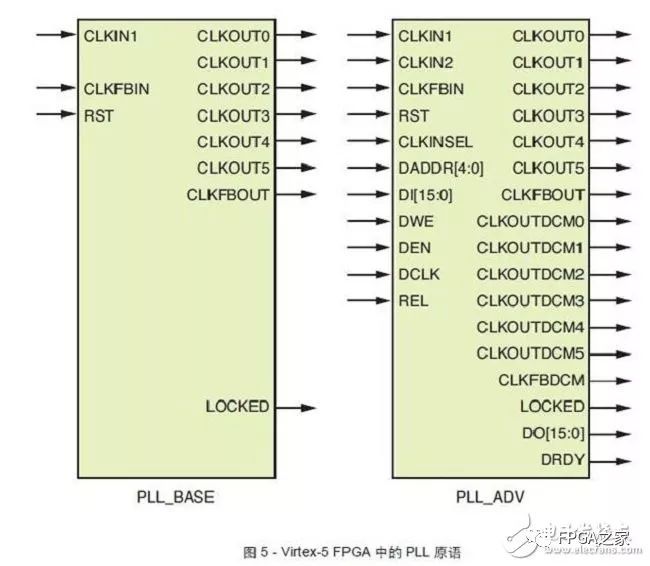

同時,7系列器件中的PLL所實現的功能沒有 MMCM所實現的多。因此雖然MMCM是建立在PLL架構之上,但7系列器件中也有獨立的PLL。圖5顯示了Virtex-5FPGA中的PLL原語。各個端口的詳細介紹請參閱Virtex-5用戶指南(UG190,5.4版本)。

設計移植

掌握四種主要的時鐘資源之間的差異及其在不同器件系列中的可用性非常重要。同時,在不同的系列中,相似的資源(比如DCM)可能在功能上并不完全相同。例如,Spartan-6FPGA中的DCM支持擴頻時鐘,但Virtex-5和Virtex-5器件中的DCM就不支持。

在規劃未來設計向更高端系列移植時,除了確保功能,為給定設計選擇正確的時鐘資源也很重要。如表1所示,Virtex-6和7系列中的MMCM能夠與之前系列中的DCM向后兼容。但需要判斷在多大程度上支持向后兼容性,因為所有這些時鐘資源都具有多功能性,提供與時鐘相關的多種不同功能。在制定產品長期發展規劃時,必須對兼容性了如指掌。

編輯:黃飛

電子發燒友App

電子發燒友App

評論