基于FPGA和DDS的信號源設計

1 引言

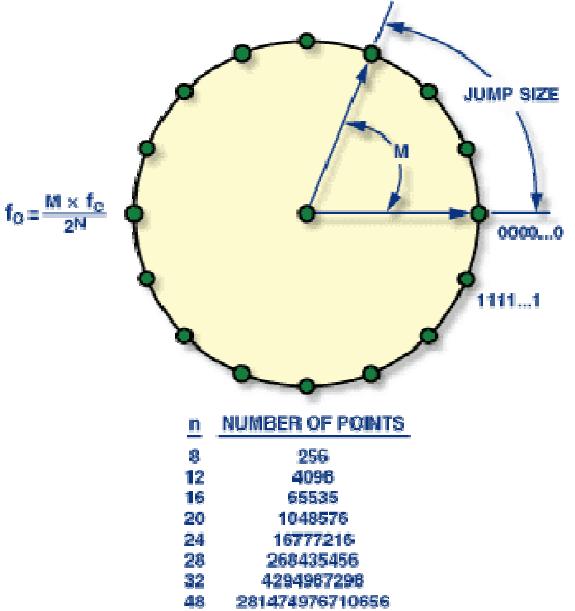

直接數字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現代器件生產技術發展的一種新的頻率合成技

2010-02-21 09:15:21 1833

1833

上篇主要是分享了Vivado編譯軟件遠程調試的方法。杰克使用Vivado軟件進行遠程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內容是對使用Vitis軟件遠程調試的方法進行總結和分享。

2023-05-25 14:36:58 1685

1685

調用ISE中DDS的IP核產生1MHZ的正弦波給AD9361,硬件平臺是K7的板子。但是通過chipsope抓取DDS產生的信號不對,I路波形和抓取的信號頻譜在matlab中如下所示

2019-04-26 15:52:20

或單片機板,利用通過模式控制和頻率字控制實時產生點頻、掃頻、ASK、FSK等各種形式的模擬信號。說明:+5V、+12V、-12V供電,輸出雙極性信號;同時提供FPGA和單片機控制程序源代碼。實驗DDS

2013-01-27 19:07:26

DDS的工作原理是什么?基于DSP Builder和DDS設計基于FPGA的DDS設計

2021-05-06 06:27:03

DDS專用芯片與基于FPGA的DDS的區別什么地方,優勢在哪?關于DDS選型,DAC的位數影響DDS的什么性能,怎么選擇合適DAC位數?AD995X系列與AD991x系列那個相噪性能雜散好?輸出約20MHz的時鐘,希望能推薦一款相噪和雜散性能好的芯片。

2018-08-06 09:13:36

jtag調試時,fpga能識別到器件,但是下載程序失敗,針對這種情況,想問下各位:1、能識別到器件,說明fpga配置電路的哪些部分是正常的2、我描述的這種情況可能是由于什么原因導致的?

2014-05-04 10:50:29

用FPGA做DDS,請教這種由于輸出信號的各位跳變時間有差異導致的毛刺怎么解決?

2017-05-17 09:57:54

本帖最后由 Nancyfans 于 2019-8-9 16:55 編輯

線上線下培訓課程推薦課程名稱:FPGA周六班,快速入門FPGA課程鏈接:http://url.elecfans.com

2019-08-02 16:09:06

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

下載配置與調試接口電路設計FPGA是SRAM型結構,本身并不能固化程序。因此FPGA需要一片Flash結構的配置芯片來存儲邏輯配置信息,用于進行上電配置。以Altera公司的FPGA為例,配置芯片

2019-06-11 05:00:07

ISE軟件,使用IP core調用DDS,產生正弦載波,使用調頻200M時鐘做為DDS輸入,功能仿真沒問題,但后仿真卻不顯示波形,只是一根紅線,是不是頻率過高啊,還是什么設置問題,請各位高人賜教,小弟初學FPGA

2013-03-20 20:37:32

你好!我們使用DDS芯片AD9954時遇到如下問題:FPGA基帶板產生FSK調制方式的2Mbit/S的碼流給AD9954,AD9954內部時鐘400MHz(20MHz的20倍),若基帶板和DDS同源

2018-12-11 10:02:36

調試硬件配置實用程序使您能夠連接到在您的開發平臺和PC之間提供接口的調試硬件單元。

提供了以下實用程序:

RVI配置IP實用程序使用此實用程序在調試硬件單元上配置IP地址。

這使您能夠通過以太網訪問

2023-08-12 06:54:13

Gowin? DDS IP 用戶指南主要內容包括功能特點、端口描述、時序說明、配置調用、參考設計等。主要用于幫助用戶快速了解 DDS IP 的產品特性、特點及使用方法。

2022-10-10 08:36:14

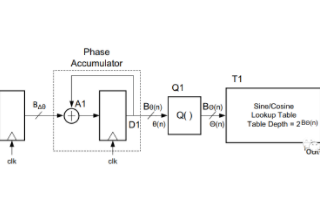

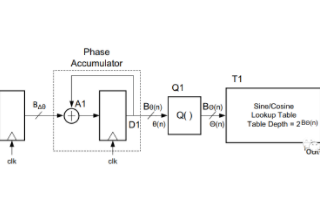

DDS(直接數字合成器) 是一款邏輯 IP 核,它可以提供適用于多種場景的正弦/余弦波形。DDS 主要由相位發生器和正弦/余弦查找表組成。 直接數字合成器也叫做 NCO(Numerically

2023-08-09 06:11:11

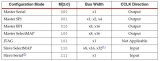

IP CORE NCO/DDS SC/SCM CONFIG

2023-03-30 12:01:19

IP CORE NCO/DDS LATTICEXP2 CONF

2023-03-30 12:01:19

IP CORE NCO/DDS LATTICEXM CONF

2023-03-30 12:01:19

; (4) DDS配置-3配置輸出信號的頻率為 0.5 MHz,結合前面的配置輸出 0.5 MHz 的固定的正弦波,其他保持默認; 總結如下,可以看到位寬符合前文的計算。 2. 使用IP核搭建濾波系統

2020-01-18 22:05:50

發生器。函數信號發生器的實現方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩定性較差,且不易調試,開發和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發展,直接頻率合成(DDS)技術

2012-05-12 23:01:54

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

這是數字信號處理系列的第一篇,以簡單的數字混頻為例,介紹在FPGA程序設計中很重要的二進制原碼、補碼;有符號數、無符號數的問題。本文不是像課本那樣介紹這些基礎概念,而是介紹很實際的設計方法。借助于

2021-07-23 06:38:10

信息顯示在LCD液晶顯示屏上。各硬件模塊之間的協調工作通過嵌入式軟核處理器NiosⅡ用編程實現控制。本設計所搭建的LCD12864控制器是通過編程實現的IP核。關鍵詞:DDS;FPGA技術;順序存儲;NiosⅡ;IP核

2019-06-21 07:10:53

基于FPGA 的DDS 調頻信號的研究與實現

2012-08-17 11:41:11

FPGA數字信號處理——基于FPGA和高速DAC的DDS設計與頻率調制(一)——X現如今,隨著高速模數-數模轉換技術和FPGA的發展。FPGA的高速性、并行性、高數據吞吐量與高速數模-模數轉換技術

2021-07-23 08:06:59

求一個基于FPGA的DDS信號發生器設計,最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

本帖最后由 kandy286 于 2013-11-8 00:33 編輯

剛學FPGA,用FPGA+DAC設計的DDS,已實現調頻,調相功能。可是調幅該怎么控制呢?有種方案是改變DAC的參考電壓

2013-11-08 00:32:04

本帖最后由 eehome 于 2013-1-5 09:51 編輯

基于FPGA的DDS設計利 用現 場 可 編程 門 陣 列 設 計 并 實 現 直 接 數 字 頻 率 合 成 器 結 合

2012-08-11 11:56:30

FPGA dds的全套設計資料分享給51hei的朋友們,有需要可以下載學習。 下面是DDS頻率合成器視頻教程內容截圖(代碼講解): 部分源程序如下: `timescale 1ns / 1ps

2018-07-03 06:06:17

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

我很難用MLSA為TMSC LAN820運行TCP/IP演示應用程序。我使用PIC32 MX795F512L。我在論壇上閱讀了很多問題并做出了修改。1。刪除DP838 48 .c和h文件2。添加

2019-09-24 11:29:09

一個DDS應用,我想使用Xilinx DDS IP內核生成任意波形,但我看到的是DDS只能生成正弦或余弦波形數據。你知道如何用其他數據替換正弦波形LUT嗎?如果可以修改該LUT,它可以生成任意波形

2019-02-12 08:07:21

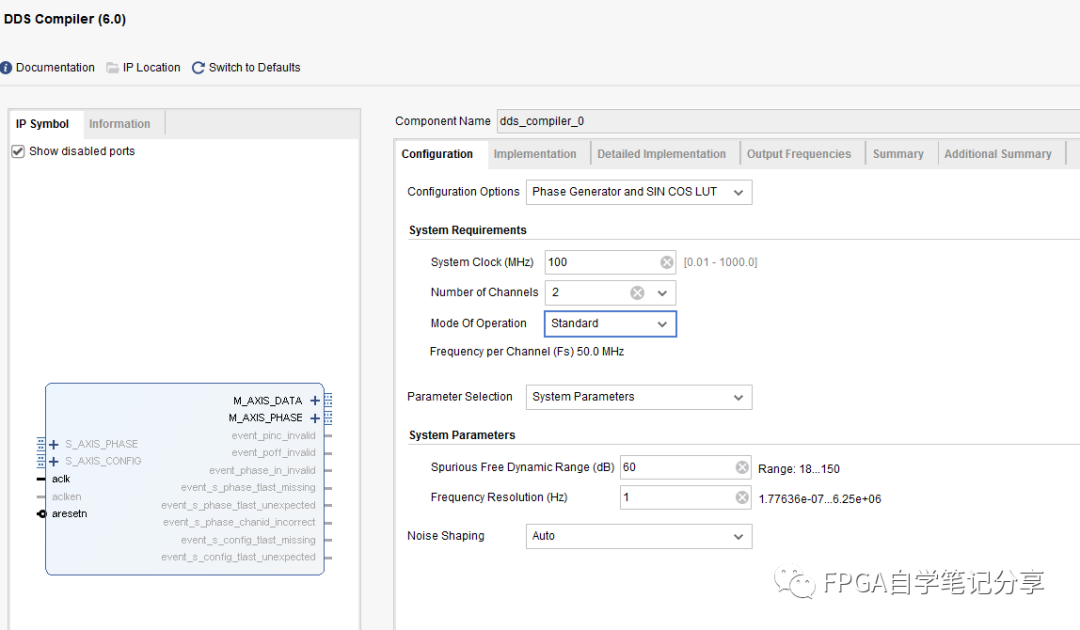

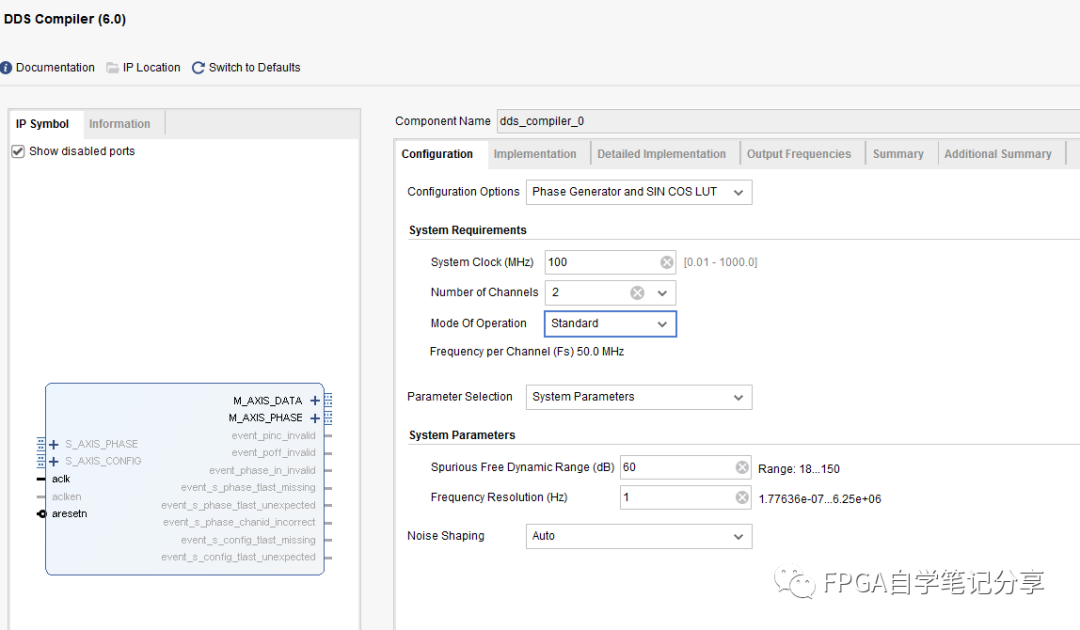

出現在 IP 存儲庫的列表中時雙擊它,將彈出一個對話框。單擊“Customize IP”按鈕,將出現 DDS 編譯器的配置窗口。在如上所示的第一個選項卡中,為了我們的目的,保留所有默認設置。在第二個選項卡

2023-02-08 15:39:30

DDS的工作原理和基本結構基于FPGA的DDS信號發生器的設計如何建立頂層模塊?

2021-04-09 06:46:42

ACEX 1K具有什么特點DDS電路工作原理是什么如何利用FPGA設計DDS電路?

2021-04-30 06:49:37

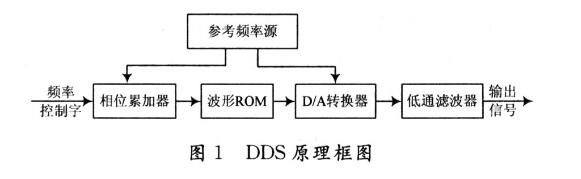

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

針對數據處理速度越來越高的要求,本文提出了基于FPGA+DDS的控制設計,能夠快速實現復雜數字系統的功能。

2021-04-30 06:17:49

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發生器。

2021-05-06 09:54:10

介紹了DDS的發展歷史及其兩種實現方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發生器的設計方法,使DDS信號發生器具有調頻、調相的功能,最后對其性能進行了分析。實驗表明該系統具有設計合理、可靠性高、結構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

用高性能的FPGA器件設計符合自己需要的DDS電路有什么好的解決辦法嗎?

2021-04-08 06:23:09

我想調用dds IP核,調用出來后,在填寫信息的第一頁有一個系統時鐘的填寫欄,在倒數第三頁有一個輸出頻率的填寫欄(最大2M),我想問這兩個填寫內容有什么關系嗎?求高手解答(最好把12.4這個版本的dds IP 核具體怎么用也幫我解答一下,謝謝!)

2015-02-18 09:20:26

怎樣去設計一種基于MCU+FPGA的DDS呢?

2022-01-26 06:30:43

大家好,我有一個問題。當我設計DDS IP CORE時,我不知道如何創建不同振幅的sin波。通常我可以創建相同的振幅但不同頻率的sin波要疊加。但是,我不知道知道如何實現幅度控制.SFDR的功能是什么?謝謝!

2020-05-13 08:58:43

的MSB來使用Xilinx DDS IP內核? DDS ip是否允許控制生成波形的相移?謝謝您的回答最好的祝福以上來自于谷歌翻譯以下為原文Hello,i need to implement an IP

2019-04-04 14:20:38

DDS AD9959應用電路和配置源程序

AD9959是一款有四個DDS通道,最高達500M SPS的數字頻率合成芯片。

常用電路接法:

2008-03-12 17:33:23 282

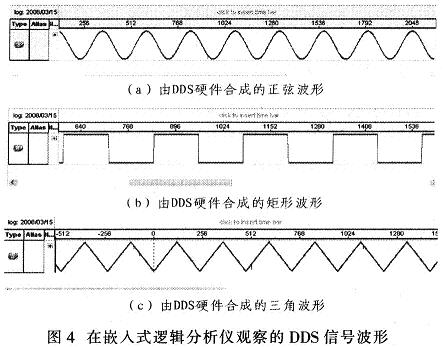

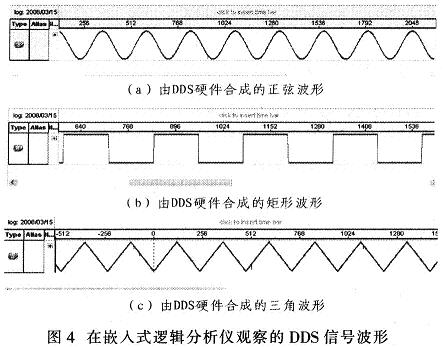

282 本文從DDS 基本原理出發,利用FPGA 來實現DDS 調頻信號的產生,重點介紹了其原理和電路設計,并給出了FPGA 設計的仿真和實驗,實驗結果表明該設計是行之有效的。直接數字頻率

2009-06-26 17:29:09 70

70 基于FPGA的DDS信號源設計與實現

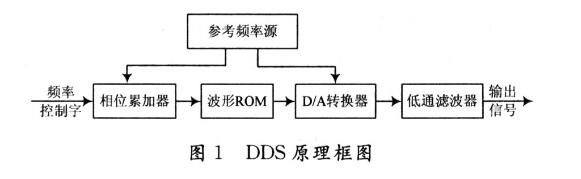

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 223

223 DDS,什么是DDS,DDS的結構

DDS概述

直接數字式頻率綜合器DDS(Direct Digital Synthesizer),

2009-09-03 08:42:40 4227

4227

DDS是什么意思,DDS結構,DDS原理是什么

什么叫DDS

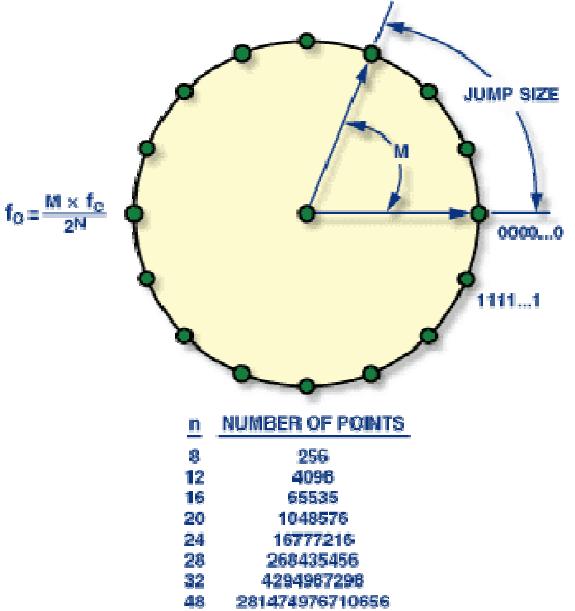

直接數字式頻率合成器DDS(Direct Digital Synthesizer),實際

2010-03-08 16:56:38 45260

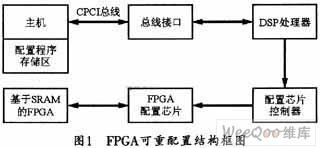

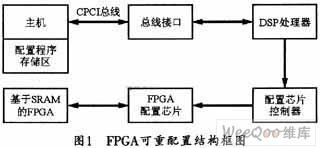

45260 采用VC++程序的FPGA重配置設計方案利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲于存儲器的不同系統數據

2010-04-14 15:14:57 580

580

本站提供DDS 調試心得的資料,希望能夠幫你學習。

2011-05-25 15:53:06 43

43 文中提出一種基于FPGA的DDS信號發生器。信號發生電路采用直接數字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數字技術,從相位概念出發,直接合成所需波形的一種新的

2011-07-16 10:24:22 1678

1678

基于FPGA、PCI9054、SDRAM和DDS設計了用于某遙測信號模擬源的專用板卡。PCI9054實現與上位機的數據交互,FPGA實現PCI本地接口轉換、數據接收發送控制及DDS芯片的配置。通過WDM驅動程序設計及

2012-03-01 15:37:30 83

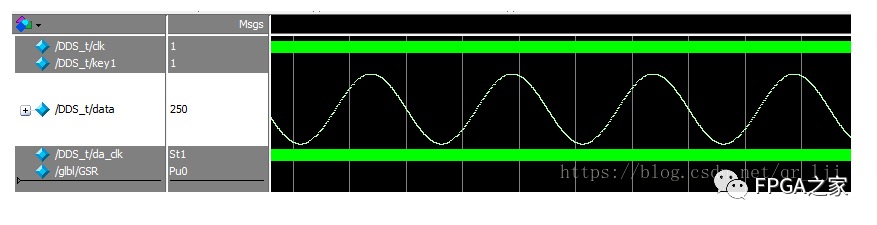

83 以Altera公司的Quartus Ⅱ 7.2作為開發工具,研究了基于FPGA的DDS IP核設計,并給出基于Signal Tap II嵌入式邏輯分析儀的仿真測試結果。將設計的DDS IP核封裝成為SOPC Builder自定義的組件,結合

2012-04-05 16:04:34 85

85 本設計基于DDS原理和FPGA技術按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數據依次全部存儲在ROM波形表里,通過外接設備撥扭開關和鍵盤控制所需波形信號的

2012-07-12 14:23:15 0

0 首先介紹了采用直接數字頻率合成(DDS)技術的正弦信號發生器的基本原理和采用FPGA實現DDS信號發生器的基本方法,然后結合DDS的原理分析了采用DDS方法實現的正弦信號發生器的優缺點

2012-11-26 16:23:32 49

49 利用現場可編程門陣列(FPGA)設計并實現直接數字頻率合成器(DDS)。結合DDS 的結構和原理,給出系統設計方法,并推導得到參考頻率與輸出頻率間的關系。DDS 具有高穩定度,高分辨率和高轉換速度,同時利用Altera 公司FPGA 內的Nios 軟核設置和顯示輸出頻率,方便且集成度高。

2016-04-01 16:14:19 24

24 基于FPGA的DDS信號源研究與設計_南楠.pdf 關于干擾的,不知道。

2016-05-16 17:15:25 4

4 Xilinx FPGA工程例子源碼:基于Spartan3E的串口調試和檢測程序

2016-06-07 15:07:45 6

6 在FPGA中嵌入cpu軟核,讓C語言程序在里面運行。這就涉及到FPGA配置文件的引導,如果C語言程序太大,需要在DDR里面運行的話也涉及到應用程序的引導的問題。我剛接觸到xinlinx的spartan3e

2018-02-27 15:33:29 5

5 本文首先介紹了DDS的基本原理和特點,其次介紹了DDS芯片AD9854的概念,最后詳細介紹了STM32的AD9854 DDS模塊調試經驗總結。

2018-05-16 16:43:13 17245

17245

結合對FPGA重配置方案的軟硬件設計,本文通過PC機并通過總線(如PCI總線)將配置數據流下載到硬件功能模塊的有關配置芯片,從而完成配置FPGA的全過程。該方法的軟件部分基于Visual C++的開發環境,并用C++語言開發動態連接庫,以用于軟件設計應用程序部分的調用。

2018-12-30 09:26:00 2425

2425

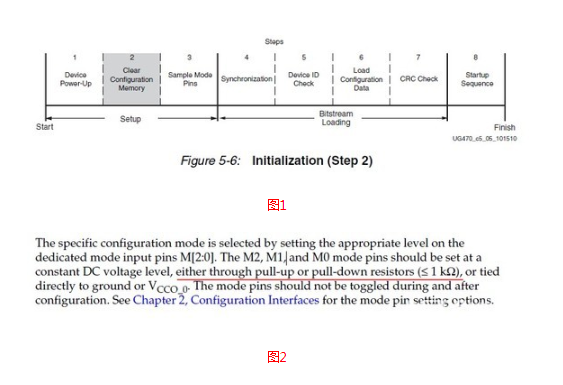

主設備可以為控制器,CPLD等等。當然FPGA也支持通過JTAG的方式進行程序下載,同時也可以通過JTAG進行FPGA時序抓取。 FPGA的配置過程包括以下幾方面:復位,程序加載,初始化,最后進入用戶

2018-11-18 18:05:01 481

481 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 在FPGA上設計一個DDS模塊,在DE0 開發板上運行,在FPGA芯片內部合成出數字波形即可。

2018-12-08 09:18:25 1923

1923

主要有AD8950.AD8951等的原理圖,介紹,PCB,調試圖片和軟件介紹

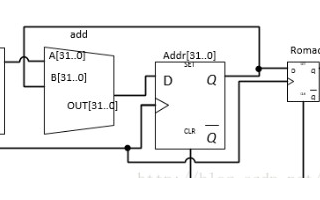

DDS的基本大批量是利用采樣定量,通過查表法產生波形。DDS的結構有很多種,其基本的電路原理可用圖1來表示。

2019-03-04 08:00:00 9

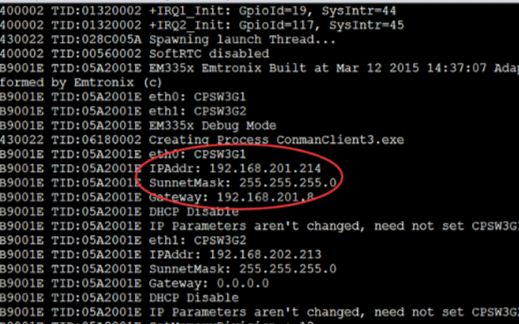

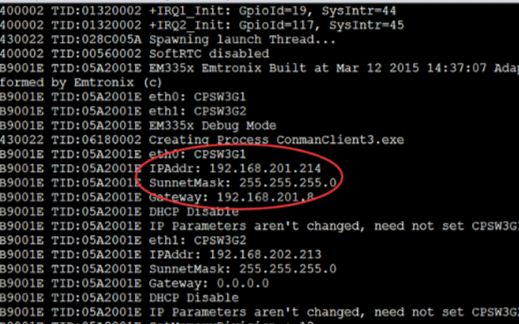

9 為了提高系統效率,WEC2013不再支持基于USB連接的Active sync功能,只能通過網絡調試應用程序,獲取主板的IP地址是調試程序的第一步。 以預裝了正版WEC2013操作系統的英創工控主板

2020-02-03 10:21:14 1353

1353

問題是FPGA使用JTAG口能把程序到FPGA,FPGA也能跑得動,當配置模式選擇MASTER SPI時,通過JTAG口下載也可以下載成功,但是問題是重新上電發現FPGA無法讀出FLASH的配置文件。

2020-03-15 16:08:00 2685

2685

對于FPGA調試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環境下進行仿真和調試,開發板類型EP4CE15F17。

2020-03-29 11:37:00 1142

1142 FPGA概述FPGA調試介紹調試挑戰設計流程概述■FPGA調試方法概述嵌入式邏輯分析儀外部測試設備■使用 FPGAVIEW改善外部測試設備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 9

9 本文檔的主要內容詳細介紹的是DDS的FPGA實現電路原理圖免費下載。

2020-10-22 12:07:17 26

26 在線調試也稱作板級調試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 3948

3948

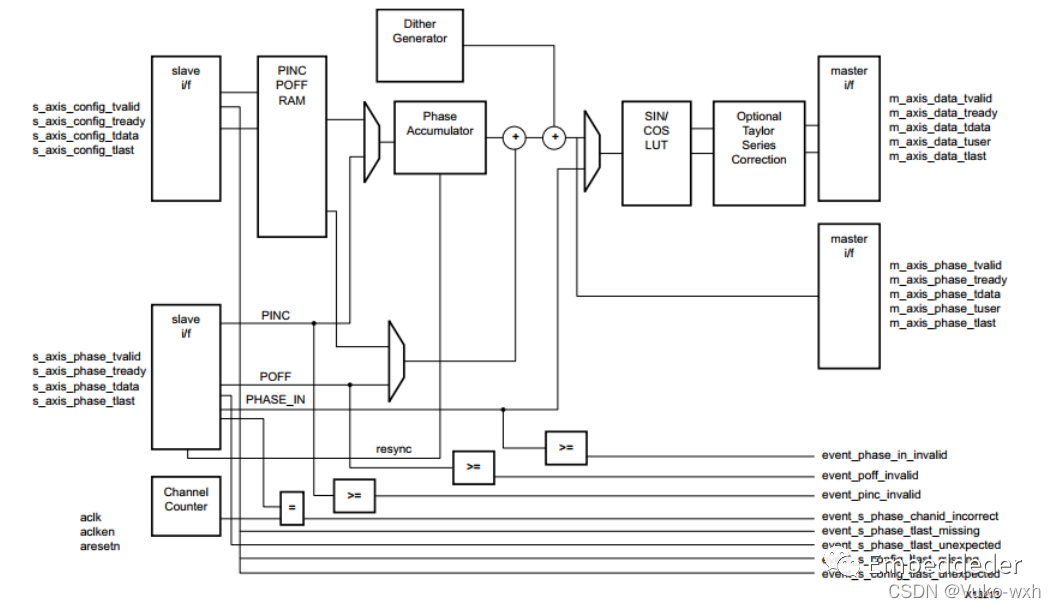

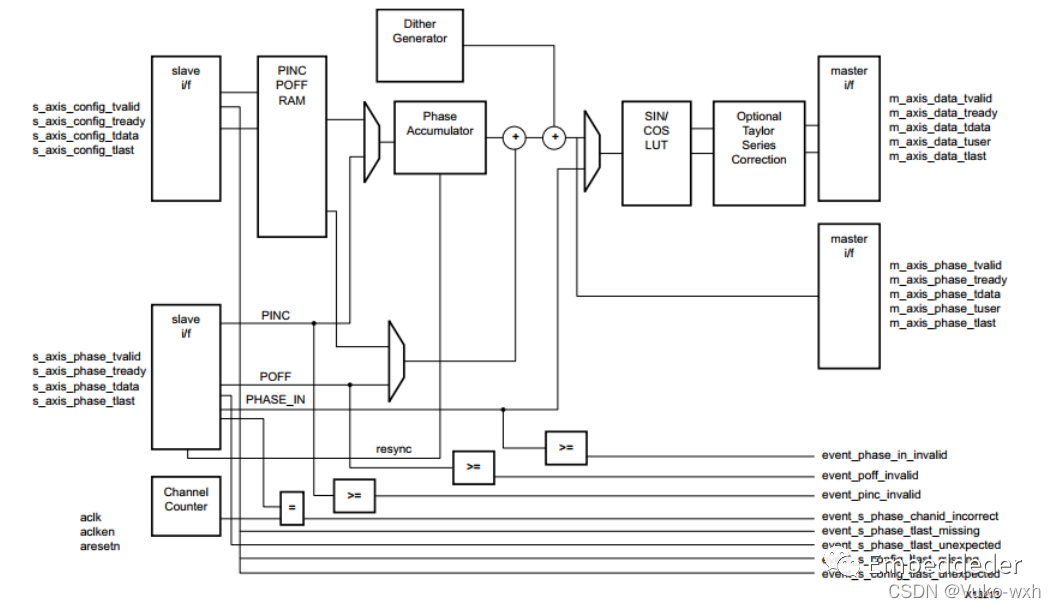

本次使用Vivado調用DDS的IP進行仿真,并嘗試多種配置方式的區別,設計單通道信號發生器(固定頻率)、Verilog查表法實現DDS、AM調制解調、DSB調制解調、可編程控制的信號發生器(調頻調相)。

2021-04-27 16:33:06 5595

5595

vivado提供了DDS IP核可以輸出正余弦波形,配置方法如下

2021-04-27 15:52:10 9060

9060

本次項目我們主要是為了講解DDS,所以我們使用了混頻這個小項目來講解。DDS自己手寫是比較簡單且靈活,但是Xilinx給我們提供了相應的IP核,那么這次我們將直接講解使用IP來產生不同頻率的正弦波。

2021-04-27 16:00:05 6329

6329

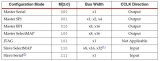

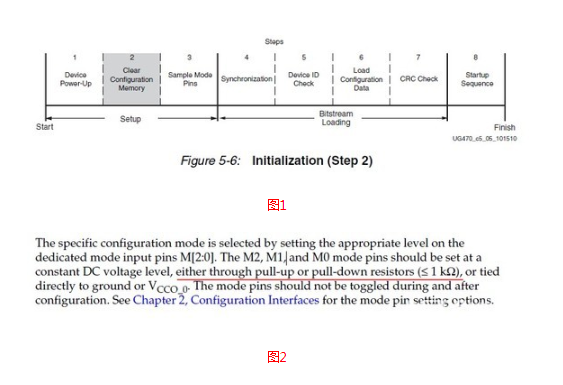

1.? Master Modes 自動下載FPGA程序在本地的非易失性存儲器,而且主模式的時鐘來自內部晶振。 2.? Slave Modes 外部控制下載FPGA配置模式,通常稱為從模式,有串行

2021-05-11 15:22:40 3967

3967

利用DDS IP實現線性調頻信號 1 DDS技術簡介隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。 直接數字

2021-07-02 10:27:58 3099

3099

利用DDS IP實現線性調頻信號1 DDS技術簡介隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。

2021-07-02 10:27:28 5773

5773

基于FPGA和DAC設計的dds發生器(普德新星電源技術有限公司的LoGo)-該文檔為基于FPGA和DAC設計的dds發生器總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 12:09:10 40

40 DDS基于FPGA的DDSSPI系統結構功能實現:在SPI接口下掛接上DDS模塊,通過單片機向FPGA發送頻率字實現任意頻率正弦波的波形,并通過DAC模塊輸出單片機部分通過按鍵輸入待產生的信號頻率

2021-12-01 17:36:17 9

9 STM8S103單片機使用IAR進行程序開發和調試1.在程序調試沒有錯誤后 選擇 “Options” 進行配置2.選擇“Debugger”選項“ST-LINK”3.選擇其中一個進行在線調試注:兩種調試模式的區別

2021-12-03 10:21:02 15

15 使用Jtag Master調試FPGA程序時用到tcl語言,通過編寫tcl腳本,可以實現對FPGA的讀寫,為調試FPGA程序帶來極大的便利,下面對FPGA調試過程中常用的tcl語法進行介紹,并通過tcl讀FIFO的例子,說明tcl在實際工程中的應用。

2022-02-19 19:44:34 2272

2272 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 1900

1900

電子發燒友網站提供《Gowin DDS IP用戶指南.pdf》資料免費下載

2022-09-16 14:32:10 0

0 電子發燒友網站提供《關于Ultra96的Xilinx DDS編譯器IP教程.zip》資料免費下載

2022-12-13 10:17:40 1

1 本文是本系列的第六篇,本文主要介紹FPGA常用運算模塊-DDS信號發生器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-24 10:37:18 3733

3733

本文對DDS以及基于DDS的SOA系統的測試策略進行探討,并介紹DDS測試方案。

2022-08-04 14:52:04 1326

1326

DDS(Direct Digital Frequency Synthesizer) 直接數字頻率合成器,本文主要介紹如何調用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號。

2023-07-24 11:23:29 1728

1728

之前的文章對dds ip 的結構、精度、參數、接口進行了詳細的說明,本文通過例化仿真對該IP的實際使用進行演示。本文例化固定模式和可配置模式兩種模式分別例化ip并仿真,說明該IP的應用。

2023-09-07 18:31:06 769

769

電子發燒友App

電子發燒友App

評論