什么是FPGA原型??

FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。?

由于硬件復(fù)雜性不斷增加,需要驗證的相關(guān)軟件數(shù)量不斷增加,因此它今天的使用范圍更加廣泛。?

為什么公司使用FPGA原型??

FPGA已經(jīng)被用于驗證相對成熟的RTL,因為它們可以代表一個近乎精確的以高速運行的設(shè)計的復(fù)制品。這些復(fù)制品通常也足夠便攜,可用于現(xiàn)場測試。在純硬件方面,由于FPGA供應(yīng)商盡快轉(zhuǎn)向最先進的制造工藝節(jié)點,F(xiàn)PGA原型設(shè)計變得更加簡單和強大。??

由于該軟件通常占設(shè)計工作量的一半以上,所以SoC RTL的FPGA實現(xiàn)也可以用作軟件開發(fā),硬件/軟件協(xié)同驗證和軟件驗證的基礎(chǔ) - 所有這些都在最終硅芯片可用之前完成。??

所有這些因素都有助于降低設(shè)計成本并縮短上市時間,降低重新調(diào)整的風(fēng)險。例如,已經(jīng)在FPGA原型上得到廣泛驗證的軟件應(yīng)該更容易與來自晶圓廠的第一塊硅相結(jié)合。FPGA原型也可用于設(shè)置任何可能的硅后調(diào)試路徑。??

一個可用的FPGA原型也可以用于產(chǎn)品演示和現(xiàn)場試驗。? ?

還有哪些其他原型方法可用嗎??

FPGA原型不是SoC或ASIC開發(fā)人員唯一的原型設(shè)計選項。??

虛擬原型可在電子系統(tǒng)級(ESL)上使用。它可用于定義和驗證設(shè)計的某些部分,如處理器架構(gòu),電源管理方案和一些軟件代碼。? ?

RTL仿真可以提供設(shè)計代碼工作方式的大量可視性,盡管速度遠遠低于真實設(shè)備的運行速度。? ?

硬件模擬器是預(yù)封裝的原型FPGA陣列,可提供比仿真器更高的調(diào)試可視性和運行速度。? ?

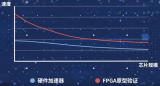

硬件加速器介于仿真和模擬之間,提供了每種仿真的一些優(yōu)點。?

這些方法不直接與FPGA原型競爭,因為今天的設(shè)計通常非常復(fù)雜,工程團隊會在設(shè)計流程的不同階段使用部分或全部。? ?

鑒于在等待第一顆硅片期間越來越多地使用FPGA作為開發(fā)平臺,隨著設(shè)計的RTL映射到FPGA原型時,它通常會達到高級階段。?

FPGA原型設(shè)計的好處是什么??

性能?

FPGA通常建立在最新的制造流程上,以實現(xiàn)最高的密度和運行速度。即使是采用主流工藝構(gòu)建的FPGA,也可以提供高門限等效計數(shù)(FPGA通常以可容納多少個標準查找表來衡量)。根據(jù)現(xiàn)成的主板廠商Polaris的說法,兩款Xilinx的Virtex-7器件可以提供相當(dāng)于48M的門電路 - 足以承載目前近85%的SoC設(shè)計。?

??

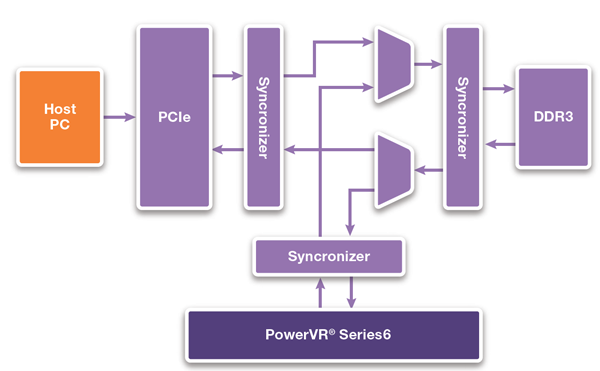

超過最大FPGA功能的設(shè)計有時在多個FPGA上進行原型設(shè)計。這使得將源RTL映射到FPGA原型環(huán)境變得更加困難,并且可能會降低原型的性能。?

成本?

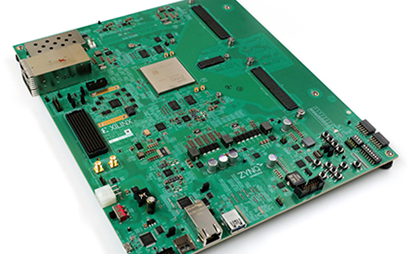

FPGA是批量生產(chǎn)的芯片,具有競爭力的價格。許多公司 - 特別是The Dini Group, S2C, Polaris Design Systems和Synopsys(HAPS) - 將它們集成到現(xiàn)成(OTS)原型板上,盡管一些公司更喜歡建立自己的原型印刷電路板(PCB) 。這個所謂的“構(gòu)建vs購買”辯論將在下面進一步討論。?

基礎(chǔ)設(shè)施?

兩家主要FPGA供應(yīng)商(原型設(shè)計市場領(lǐng)導(dǎo)者Xilinx及其競爭對手Altera)都提供了廣泛的工具來支持他們的產(chǎn)品。他們還與主要的EDA供應(yīng)商建立了聯(lián)盟,這些供應(yīng)商為軟件套件提供了增強的FPGA原型設(shè)計。?

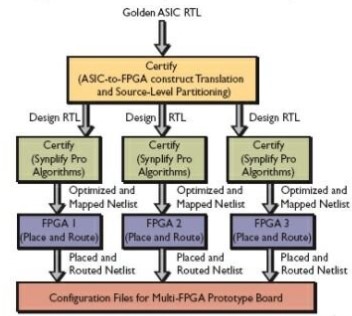

Cadence Design Systems提供Allegro FPGA系統(tǒng)規(guī)劃器。Mentor Graphics將其Precision Precision工具與Veridae Systems提供的Certus和Corus驗證和調(diào)試工具聯(lián)系起來。Synopsys提供OTS板卡以及Synplify Pro和Premier綜合工具(在2012年4月發(fā)布的版本中增加了重要功能)。??

其他OTS主板供應(yīng)商也與這些和其他工具供應(yīng)商以及他們自己的軟件有合作關(guān)系。?

??

?2011年,Synopsys和Xilinx發(fā)布了基于FPGA的原型方法手冊。這本由Synopsys出版社出版的書籍不可避免地通過兩家公司自己的產(chǎn)品解決了具體的案例研究項目,但是更一般地說,它旨在描述一種用可編程邏輯來構(gòu)建原型項目的供應(yīng)商中立方法。您可以閱讀本指南中討論的許多高層次問題的示例章節(jié),或者閱讀本手冊的更多詳細信息,并在此處下載電子書版本。?

??

可移植性?

FPGA板可以在與最終SoC相同的嘈雜環(huán)境中進行測試。這對于打算用于便攜式消費設(shè)備以及工業(yè),通信基礎(chǔ)設(shè)施,醫(yī)療和軍事/航空航天市場的產(chǎn)品有益。?

??

可用性?

FPGA原型的成本相對較低意味著公司通常可以構(gòu)建其中的幾個,這加速了硬件驗證,軟件開發(fā),硬件/軟件協(xié)同驗證和軟件驗證。每個團隊都可以有自己的原型,可能有幾個。?

??

FPGA原型設(shè)計面臨的挑戰(zhàn)是什么??

FPGA原型設(shè)計面臨技術(shù)和商業(yè)挑戰(zhàn)。?

技術(shù)挑戰(zhàn)?

分區(qū)?

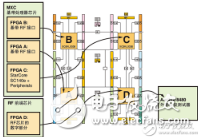

大型設(shè)計可能需要在多個FPGA之間進行分離(分區(qū))以實現(xiàn)所需的門控容量。這項任務(wù)通常被認為是FPGA原型設(shè)計的最大挑戰(zhàn)。?

分區(qū)包括估計持有該設(shè)計所需的FPGA數(shù)量,以及購買OTS板卡(可提供各種配置)或者構(gòu)建一個用于容納大量FPGA的OTS板卡。通過將設(shè)計中的每個主要功能塊分配給一個器件,或者根據(jù)結(jié)果預(yù)先綜合設(shè)計和工作,您可以估算要使用多少個FPGA。您還可以利用由硅和OTS主板供應(yīng)商提供的標準第三方IP模塊,為您的設(shè)計中使用的每個模塊分配一個FPGA。同樣,您需要決定哪些配件,如子板,您將需要:這些配件的“經(jīng)過驗證”版本。?

分區(qū)過程本身很可能是一個棘手的迭代過程,涉及將設(shè)計映射到設(shè)備的眾多判斷調(diào)用,以及從RTL或軟件中的實際錯誤中過濾出并糾正映射錯誤。每個FPGA的利用率是最優(yōu)的?內(nèi)存要求如何?那么I / O和互連呢??

手動干預(yù)?

FPGA原型設(shè)計可能需要幾種類型的手動干預(yù)。?

由于原始設(shè)計RTL被轉(zhuǎn)換為FPGA綜合和布局工具所需的硬件描述語言(HDL),因此即使工具已經(jīng)實現(xiàn)了大部分翻譯的自動化,也可能需要一些手動編碼才能使原型工作。很可能起源于設(shè)計的工程師不熟悉FPGA的HDL編碼風(fēng)格。因此這可能是一個漫長而容易出錯的過程。? ?

映射的各個方面都面臨著挑戰(zhàn)。FPGA上的時鐘樹路由(特別是原始設(shè)計具有門控時鐘的地方)非常困難。如果允許關(guān)鍵路徑通過緩慢的芯片到芯片到芯片路徑運行,原型性能將會受到影響。原創(chuàng)中的內(nèi)存和加密塊也會帶來重大困難。? ?

對于設(shè)計的許多方面,一對一映射是不可能的。確保您有足夠的資源和專業(yè)知識來處理過渡中較為困難的部分 - 也可能是您設(shè)計中最敏感的部分,因為它們具有差異性。? ?

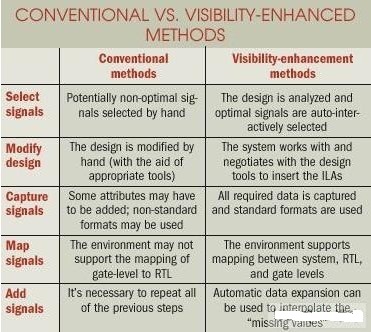

調(diào)試可見性?

上述兩個挑戰(zhàn)所代表的工作量說明了為什么FPGA原型設(shè)計最好采用成熟的RTL代碼來提供,而這種代碼幾乎沒有什么意外。確保調(diào)試ram的可見性成為難題。? ?

從第一個單FPGA原型開始就有足夠的設(shè)計可視性來進行有效的調(diào)試存在一個問題。可用的可見性往往局限于單個FPGA,這使得跨多個FPGA映射的設(shè)計使調(diào)試可見性變得更加困難。? ?

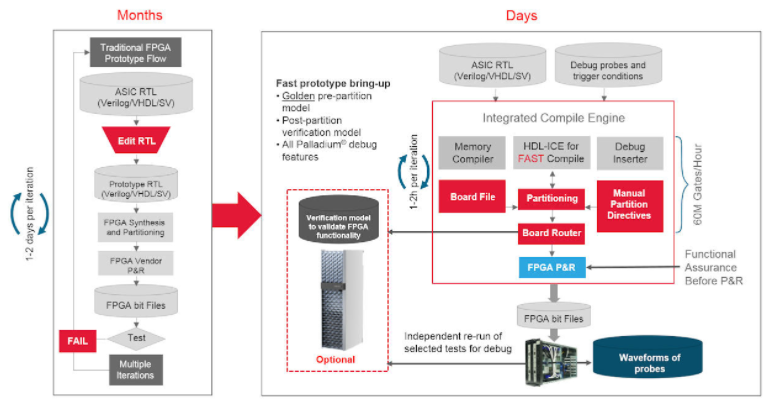

編譯時間?

從歷史上看,工程師們編譯了一個FPGA原型,直到錯誤停止了這個過程。他們會修復(fù)這個錯誤,然后從頭開始重新編譯。這里的潛在延誤很明顯。在Synplify Premier的最新版本中,Synopsys已經(jīng)加入了“繼續(xù)出錯”功能,旨在緩解這個問題。編譯將不會停止,并會在最后生成一個整理錯誤列表。(這不像RTL仿真,在這種仿真中,您可能會遇到錯誤,請修復(fù)并從此處繼續(xù)。)???

商業(yè)挑戰(zhàn)?

時間對原型?

一些FPGA原型在他們原本應(yīng)該進行原型設(shè)計的第一塊硅片抵達時未完成。這是生活中的事實。?

設(shè)計經(jīng)理擔(dān)心將重要的工程資源投入到一個有失敗風(fēng)險的原型項目中。現(xiàn)實情況是,大多數(shù)失敗是在原型開始工作之前沒有進行徹底的風(fēng)險評估的結(jié)果。什么是適當(dāng)?shù)馁Y源,它們是可用的(內(nèi)部還是外部)?正在采用哪種方法(有幾種可用并在下面討論)?? ?

FPGA原型設(shè)計過程變得更加自動化,但假設(shè)設(shè)計團隊不需要進行任何手動干預(yù),除了涉及修復(fù)令人滿意的原型所發(fā)現(xiàn)的錯誤之外的其他手動干預(yù)。相反,在可用時間內(nèi)對所需內(nèi)容進行研究和保守估計。?

建設(shè)vs購買?

關(guān)于FPGA原型設(shè)計最激烈的辯論之一是您是否應(yīng)該自己購買FPGA并構(gòu)建PCB,或購買OTS板并根據(jù)您的要求量身定制。答案是,“這取決于項目。”? ?

爭論的“構(gòu)建”方面表示OTS板卡太不靈活,無法應(yīng)對日益復(fù)雜的項目日新月異的需求。它繼續(xù)說,盡管開發(fā)自己的PCB確實花費了大量的時間和精力,但與支付可能無法滿足您的要求的OTS等效品相比,有一些工具可以以更具成本效益的方式來協(xié)助此過程。論證的“構(gòu)建”一面也指出了OTS板卡的總線寬度和工作頻率有限。? ?

爭論的“購買”方面表明,關(guān)于不靈活的說法被夸大了,構(gòu)建先進FPGA原型所需的PCBs會進一步增加設(shè)計過程的復(fù)雜性。它還表示,構(gòu)建自己的板卡可能會影響到時間原型,甚至可能會縮短上市時間。此外,OTS板在其上的芯片和互連,其他本地特征和附件的可用性(如子板)連接到與最終硅芯片可能連接的外部系統(tǒng)方面“已證實”。'購買'支持者也指出,電路板也被設(shè)計為與當(dāng)今FPGA的性能相匹配。?

那么,它值得嗎??

FPGA原型設(shè)計是一個有價值的策略,特別是對于嵌入式軟件內(nèi)容高的項目,可以滿足對時間敏感或要求很高的市場的需求。??

最近的一項調(diào)查發(fā)現(xiàn),一半的嵌入式軟件項目錯過了最后期限,其中44%未達到最初設(shè)想的功能。如果沒有其他,F(xiàn)PGA原型使軟件團隊能夠在最終的系統(tǒng)集成中盡早開始工作。? ?

FPGA原型提供了執(zhí)行全面的硬件 - 軟件協(xié)同驗證的最有效方法,特別是在降低堆棧的關(guān)鍵階段,以及在與最終芯片結(jié)合的軟件代碼之前的最終驗證。?

是否采用FPGA原型的問題很大程度上取決于您的團隊是否可以平衡執(zhí)行復(fù)雜且通常非常困難的任務(wù)所需的風(fēng)險和資源。?

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論