1.面積與速度的平衡與互換

這里的面積指一個(gè)設(shè)計(jì)消耗 FPGA/CPLD 的邏輯資源的數(shù)量,對(duì)于 FPGA 可以用消耗的 FF(觸發(fā)器)和 LUT(查找表)來衡量,更一般的衡量方式可以用設(shè)計(jì)所占的等價(jià)邏輯門數(shù)。

速度指設(shè)計(jì)在芯片上穩(wěn)定運(yùn)行,所能達(dá)到的最高頻率,這個(gè)頻率由設(shè)計(jì)的時(shí)序狀況來決定,和設(shè)計(jì)滿足的時(shí)鐘要求,PAD to PAD time ,Clock Setup TIme,Clock Hold TIme,Clock-to-Output Delay 等眾多時(shí)序特征量密切相關(guān)。

面積和速度這兩個(gè)指標(biāo)貫穿 FPGA/CPLD 設(shè)計(jì)的時(shí)鐘,是設(shè)計(jì)質(zhì)量的評(píng)價(jià)的終極標(biāo)準(zhǔn)。

面積和速度是一對(duì)對(duì)立統(tǒng)一的矛盾體。要求一個(gè)同事具備設(shè)計(jì)面積最小,運(yùn)行頻率最高是不現(xiàn)實(shí)的。更科學(xué)的設(shè)計(jì)目標(biāo)應(yīng)該是在滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大,頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。

作為矛盾的兩個(gè)組成部分,面積和速度的地位是不一樣的。相比之下,滿足時(shí)序、工作頻率的要求更重要一些,當(dāng)兩者沖突時(shí),采用速度優(yōu)先的準(zhǔn)則。

從理論上講,如果一個(gè)設(shè)計(jì)時(shí)序余量較大,所能跑的速度遠(yuǎn)遠(yuǎn)高于設(shè)計(jì)要求,那么就通過功能模塊的復(fù)用來減少整個(gè)設(shè)計(jì)消耗的芯片面積,這就是用速度的優(yōu)勢(shì)換取面積的節(jié)約。反之,如果一個(gè)設(shè)計(jì)的時(shí)序要求很高,普通方法達(dá)不到設(shè)計(jì)頻率,那么一般可以通過將數(shù)據(jù)流串并轉(zhuǎn)換,并行復(fù)制多個(gè)操作模塊,對(duì)整個(gè)設(shè)計(jì)采取乒乓操作和串并轉(zhuǎn)換的思想運(yùn)行。

2. 硬件原則

硬件原則主要針對(duì) HDL 代碼編寫而言

Verilog 是采用了 C 語言形式的硬件的抽象,它的本質(zhì)作用在于描述硬件!它的最終實(shí)現(xiàn)結(jié)果是芯片內(nèi)部的實(shí)際電路。所以評(píng)判一段 HDL 代碼的優(yōu)劣的最終標(biāo)準(zhǔn)是:其描述并實(shí)現(xiàn)的硬件電路的性能。包括面積和速度兩個(gè)方面。評(píng)價(jià)一個(gè)設(shè)計(jì)的代碼水平較高,僅僅是說這個(gè)設(shè)計(jì)是由硬件想 HDL 代碼這種表現(xiàn)形式的轉(zhuǎn)換更加流暢、合理。而一個(gè)設(shè)計(jì)最終性能,在更大程度上取決于設(shè)計(jì)工程師所構(gòu)想的硬件實(shí)現(xiàn)方案的效率以及合理性。(HDL 代碼僅僅是硬件設(shè)計(jì)的表達(dá)形式之一)

初學(xué)者,片面追求代碼的整潔、簡(jiǎn)短,是錯(cuò)誤的。是與 HDL 的標(biāo)準(zhǔn)背道而馳的。正確的編碼方法,首先要做到對(duì)所需實(shí)現(xiàn)的硬件電路胸有成竹,對(duì)該部分的硬件的結(jié)構(gòu)和連接十分清晰,然后再用適當(dāng)?shù)?HDL 語句表達(dá)出來即可。

另外,Verilog 作為一種 HDL 語言,是分層次的。系統(tǒng)級(jí) -- 算法級(jí) -- 寄存器傳輸級(jí) -- 邏輯級(jí) -- 門級(jí) -- 開關(guān)級(jí)。

構(gòu)建優(yōu)先級(jí)樹會(huì)消耗大量的組合邏輯,所以如果能夠使用 case 的地方,盡量使用 case 代替 if.....else......

3. 系統(tǒng)原則

系統(tǒng)原則包含兩個(gè)層次的含義:更高層面上看,是一個(gè)硬件系統(tǒng),一塊單板如何進(jìn)行模塊花費(fèi)和任務(wù)分配,什么樣的算法和功能適合放在 FPGA 里面實(shí)現(xiàn),什么樣的算法和功能適合放在 DSP,CPU 里面實(shí)現(xiàn),以及 FPGA 的規(guī)模估算數(shù)據(jù)接口設(shè)計(jì)等。具體到 FPGA 設(shè)計(jì)就要對(duì)設(shè)計(jì)的全局有個(gè)宏觀上的合理安排,比如時(shí)鐘域,模塊復(fù)用,約束,面積,速度等問題。在系統(tǒng)上模塊的優(yōu)化最為重要。

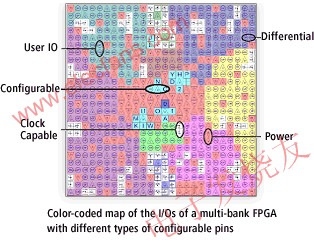

一般來說實(shí)時(shí)性要求高,頻率快的功能模塊適合 FPGA 實(shí)現(xiàn)。而 FPGA 和 CPLD 相比,更適合實(shí)現(xiàn)規(guī)模較大,頻率較高、寄存器較多的設(shè)計(jì)。使用 FPGA/CPLD 設(shè)計(jì)時(shí),應(yīng)該對(duì)芯片內(nèi)部的各種底層硬件資源,和可用的設(shè)計(jì)資源有一個(gè)較深刻的認(rèn)識(shí)。比如 FPGA 一般觸發(fā)器資源豐富,CPLD 的組合邏輯資源更加豐富。FPGA/CPLD 一般是由底層可編程硬件單元,BRAM,布線資源,可配置 IO 單元,時(shí)鐘資源等構(gòu)成。底層可編程硬件單元一般由觸發(fā)器和查找表組成。Xilinx 的底層可編程硬件資源較 SLICE,由兩個(gè) FF 和 2 個(gè) LUT 構(gòu)成。Altera 的底層硬件資源叫 LE,由 1 個(gè) FF 和 1 個(gè) LUT 構(gòu)成。

使用片內(nèi) RAN 可以實(shí)現(xiàn)單口 RAM,雙口 RAM,同步、異步 FIFO,ROM,CAM 等常用單元模塊。

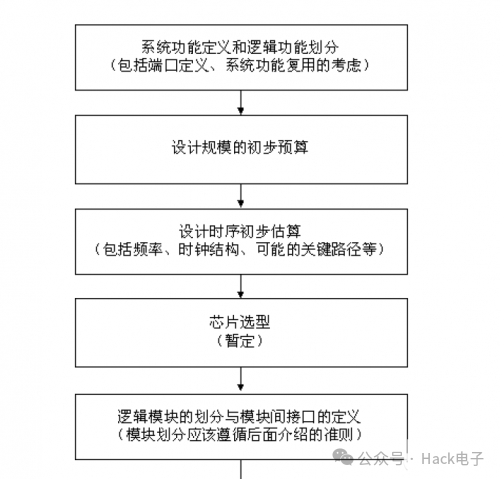

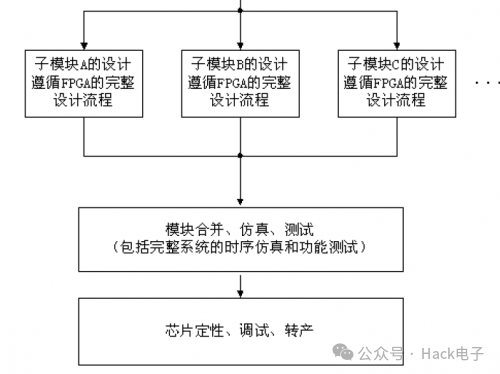

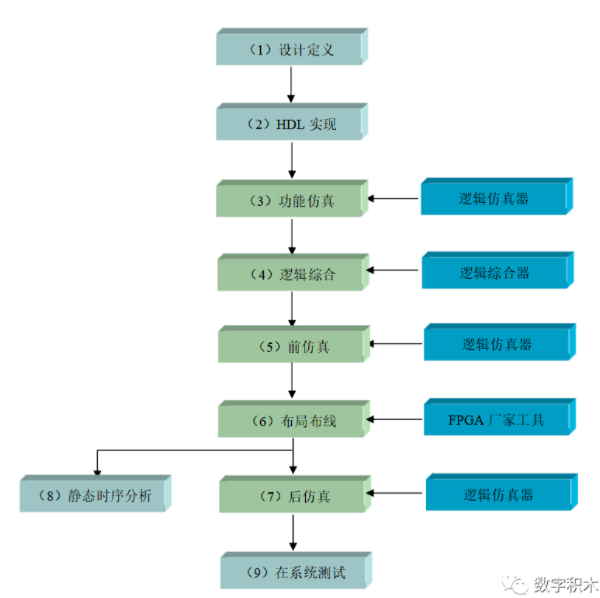

一般的 FPGA 系統(tǒng)規(guī)劃的簡(jiǎn)化流程

?

4. 同步設(shè)計(jì)原則

異步電路

電路的邏輯核心是用組合邏輯電路實(shí)現(xiàn)。比如異步的 FIFO/RAM 讀寫信號(hào),地址譯碼等電路。電路的主要信號(hào)、輸出信號(hào)等并不依賴于任何一個(gè)時(shí)鐘性信號(hào),不是由時(shí)鐘信號(hào)驅(qū)動(dòng) FF 產(chǎn)生的。

異步時(shí)序電路的最大缺點(diǎn)是容易產(chǎn)生毛刺。在布局布線后仿真和用邏輯分析儀觀測(cè)實(shí)際信號(hào)時(shí),這種毛刺尤其明顯。

同步時(shí)序

電路的核心邏輯用各種各樣的觸發(fā)器實(shí)現(xiàn)

電路的主要信號(hào)、輸出信號(hào)都是由某個(gè)時(shí)鐘沿驅(qū)動(dòng)觸發(fā)器產(chǎn)生出來的。

同步時(shí)序電路可以很好的避免毛刺。布局布線后仿真,和用邏輯分析儀采樣實(shí)際工作信號(hào)都沒有毛刺。

是否時(shí)序電路一定比異步電路使用更多的資源呢?

從單純的 ASCI 設(shè)計(jì)來看,大約需要 7 個(gè)門來實(shí)現(xiàn)一個(gè) D 觸發(fā)器,而一個(gè)門即可實(shí)現(xiàn)一個(gè) 2 輸入與非門,所以一般來說,同步時(shí)序電路比異步電路占用更大的面積。(FPGA/CPLD 中不同,主要是因?yàn)閱卧獕K的計(jì)算方式)

如何實(shí)現(xiàn)同步時(shí)序電路的延時(shí)?

異步電路產(chǎn)生延時(shí)的一般方法是插入一個(gè) Buffer,兩級(jí)與非門等。這種延時(shí)調(diào)整手段是不適用同步時(shí)序設(shè)計(jì)思想的。首先要明確一點(diǎn) HDL 語法中的延時(shí)控制語法,是行為級(jí)的代碼描述,常用于仿真測(cè)試激勵(lì),但是在電路綜合是會(huì)被忽略,并不能啟動(dòng)延時(shí)作用。

同步時(shí)序電路的延時(shí)一般是通過時(shí)序控制完成的。換句話說,同步時(shí)序電路的延時(shí)被當(dāng)做一個(gè)電路邏輯來設(shè)計(jì)。對(duì)于比較大的和特殊定時(shí)要求的延時(shí),一般用高速時(shí)鐘產(chǎn)生一個(gè)計(jì)數(shù)器,通過計(jì)數(shù)器的計(jì)數(shù)控制延遲;對(duì)于比較小的延時(shí),可以用 D 觸發(fā)器打一下,這種做法不僅僅使信號(hào)延時(shí)了一個(gè)時(shí)鐘周期,而且完成了信號(hào)與時(shí)鐘的初次同步,在輸入信號(hào)采樣和增加時(shí)序約束余量中使用。

同步時(shí)序電路的時(shí)鐘如何產(chǎn)生?

時(shí)鐘的質(zhì)量和穩(wěn)定性直接決定著同步時(shí)序電路的性能。

輸入信號(hào)的同步

同步時(shí)序電路要求對(duì)輸入信號(hào)進(jìn)行同步化,如果輸入數(shù)據(jù)的節(jié)拍和本級(jí)芯片的處理時(shí)鐘同頻,并且建立保持時(shí)間匹配,可以直接用本級(jí)芯片的主時(shí)鐘對(duì)輸入數(shù)據(jù)寄存器采樣,完成輸入數(shù)據(jù)的同步化。如果輸入數(shù)據(jù)和本級(jí)芯片的處理時(shí)鐘是異步的,特別是頻率不匹配的時(shí)候,則要用處理時(shí)鐘對(duì)輸入數(shù)據(jù)做兩次寄存器采樣,才能完成輸入數(shù)據(jù)的同步化。

是不是定義為 Reg 型,就一定綜合成寄存器,并且是同步時(shí)序電路呢?

答案的否定的。Verilog 中最常用的兩種數(shù)據(jù)類型 Wire 和 Reg,一般來說,Wire 型指定書數(shù)據(jù)和網(wǎng)線通過組合邏輯實(shí)現(xiàn),而 reg 型指定的數(shù)據(jù)不一定就是用寄存器實(shí)現(xiàn)。

5. 乒乓操作

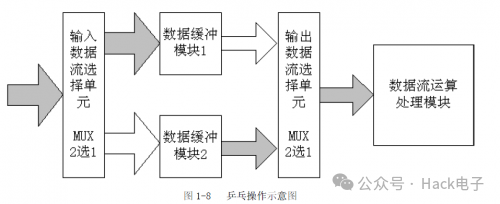

乒乓操作是一個(gè)常常應(yīng)用于數(shù)據(jù)流控制的處理技巧。

數(shù)據(jù)緩沖模塊可以為任何的存儲(chǔ)模塊,比較常用的存儲(chǔ)模塊為雙口 RAM(DPRAM),單口 RAM(SPRAM),F(xiàn)IFO 等。在等一個(gè)緩沖周期,將輸入的數(shù)據(jù)流緩存到數(shù)據(jù)緩存模塊 1,在第二個(gè)緩沖周期,通過輸入數(shù)據(jù)流選擇單元,將輸入的數(shù)據(jù)流緩存到數(shù)據(jù)緩沖模塊 2. 乒乓操作的最大特點(diǎn)是,通過輸入數(shù)據(jù)選擇單元和輸出數(shù)據(jù)選擇單元,進(jìn)行運(yùn)算和處理。把乒乓操作模塊當(dāng)成一個(gè)整體,站在兩端看數(shù)據(jù),輸入數(shù)據(jù)和輸出數(shù)據(jù)流都是連續(xù)不斷的,沒有任何停頓,因此非常適合對(duì)數(shù)據(jù)流進(jìn)行流水線式處理。所以乒乓操作常常應(yīng)用于流水線式算法,完成數(shù)據(jù)的無縫緩沖和處理。

乒乓操作的第二個(gè)優(yōu)點(diǎn)是可以節(jié)約緩沖區(qū)空間。比如在 WCDMA 基帶應(yīng)用中,1 幀是由 15 個(gè)時(shí)隙組成的,有時(shí)需要將 1 整幀的數(shù)據(jù)延時(shí)一個(gè)時(shí)隙后處理,比較直接的方法就是將這幀數(shù)據(jù)緩存起來,然后延時(shí)一個(gè)時(shí)隙,進(jìn)行處理。這時(shí)緩沖區(qū)的長(zhǎng)度為 1 幀的數(shù)據(jù)長(zhǎng),假設(shè)數(shù)據(jù)速率是 3.84Mb/s,1 幀 10ms,此時(shí)需要緩沖區(qū)的長(zhǎng)度是 38400bit,如果采用乒乓操作,只需定義兩個(gè)緩沖 1 時(shí)隙的數(shù)據(jù) RAM,當(dāng)向一個(gè) RAM 寫數(shù)據(jù)時(shí),從另一塊 RAM 讀數(shù)據(jù),然后送到處理單元處理,此時(shí)每塊 RAM 的容量?jī)H需 2560bit,2 塊加起來 5120bit 的容量。

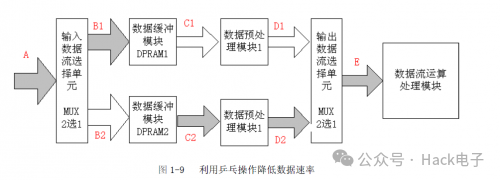

巧妙的運(yùn)用乒乓操作,還可以達(dá)到低速模塊處理高速數(shù)據(jù)流的效果。

6. 串并轉(zhuǎn)換

7. 流水線操作

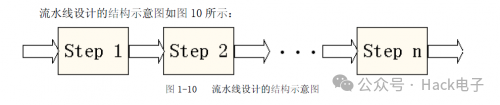

流水線處理是高速設(shè)計(jì)中一個(gè)常用的設(shè)計(jì)手段。如果某個(gè)設(shè)計(jì)的處理流程分為若干步驟,而且整個(gè)數(shù)據(jù)處理是單流向的。則可以考慮采用流水線設(shè)計(jì)方法提高系統(tǒng)的工作頻率。

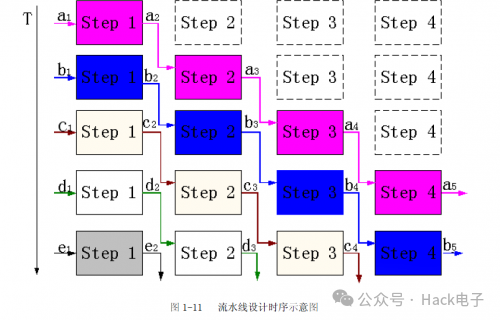

其基本結(jié)構(gòu)為:將適當(dāng)劃分的 n 個(gè)操作步驟單流向串聯(lián)起來。流水線操作的最大特點(diǎn)和要求是,數(shù)據(jù)在各個(gè)步驟的處理,從時(shí)間上是連續(xù)的,如果將每個(gè)操作步驟簡(jiǎn)化假設(shè)為一個(gè)通過 D 觸發(fā)器(就是用寄存器打一個(gè)節(jié)拍),那么流水線操作就類似一個(gè)移位寄存器組,數(shù)據(jù)流依次流經(jīng) D 觸發(fā)器,完成每個(gè)步驟的操作。流水線設(shè)計(jì)時(shí)序圖如下:

流水線設(shè)計(jì)的關(guān)鍵在于,整個(gè)設(shè)計(jì)時(shí)序的合理安排。要求每個(gè)操作步驟的劃分合理。如果前級(jí)操作時(shí)間恰好等于后級(jí)操作時(shí)間,設(shè)計(jì)最為簡(jiǎn)單,前級(jí)的輸出直接匯入后級(jí)的輸入即可。如果前級(jí)操作時(shí)間大于后級(jí)操作時(shí)間,則需要進(jìn)行適當(dāng)緩存。如果前級(jí)操作時(shí)間小于后級(jí)操作時(shí)間,則必須通過復(fù)制邏輯,將數(shù)據(jù)流分流,或在前級(jí)對(duì)數(shù)據(jù)采用存儲(chǔ)、后處理的方式。否則會(huì)造成后級(jí)數(shù)據(jù)的溢出。

8. 數(shù)據(jù)接口的同步方法

數(shù)據(jù)接口的同步在 FPGA/CPLD 設(shè)計(jì)中一個(gè)常見問題。很多設(shè)計(jì)工作不穩(wěn)定都是源于數(shù)據(jù)接口的同步問題。

輸入輸出的延時(shí)不可測(cè),或者可能有變動(dòng),如何完成數(shù)據(jù)的同步?

對(duì)于數(shù)據(jù)延遲不可測(cè)或者變動(dòng),就需要建立同步機(jī)制。或者用一個(gè)同步使能,或者同步指示信號(hào)。另外使數(shù)據(jù)通過 RAM 或者 FIFO 的存取,也可以達(dá)到數(shù)據(jù)同步的目的。

把數(shù)據(jù)存放在 RAM 或 FIFO 的方法如下,將上級(jí)芯片提供的數(shù)據(jù)隨路時(shí)鐘作為寫信號(hào),將數(shù)據(jù)寫入 RAM 或者 FIFO,然后使用本級(jí)時(shí)鐘的采樣時(shí)鐘(一般是數(shù)據(jù)處理的主時(shí)鐘),將數(shù)據(jù)讀出來即可。這種做法的關(guān)鍵是數(shù)據(jù)寫入 RAM 或者 FIFO 要可靠,如果使用同步 RAM 或者 FIFO,就要求有一個(gè)與數(shù)據(jù)延遲相對(duì)關(guān)系固定的隨路指示信號(hào)。

?

?

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論