今天給大俠帶來FPGA設計中,對SPI進行參數(shù)化結構設計,話不多說,上貨。 ?

為了避免每次SPI驅動重寫,直接參數(shù)化,盡量一勞永逸。SPI master有啥用呢,你發(fā)現(xiàn)各種外圍芯片的配置一般都是通過SPI配置的,只不過有三線和四線。SPI slave有什么用呢,當外部主機(cpu)要讀取FPGA內部寄存器值,那就很有用了,F(xiàn)PGA寄存器就相當于RAM,cpu通過SPI尋址讀寫數(shù)據(jù)。代碼僅供參考,勿做商業(yè)用途。

SPI salve

SPI salve支持功能:

支持三線SPI或者四線SPI。通過define切換。??? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

支持指令長度、幀長自定義。? ??? ? ? ? ? ? ? ? ? ? ? ? ? ?

工作時鐘可自定義,大于SPI clk的2倍。

用戶只需修改:(1)幾線SPI。(2)單幀長度。(3)指令長度。(4)寄存器開辟。

注意:指令最高bit表示讀寫,低寫高讀,其余bit表示地址。指令接著為數(shù)據(jù)端,兩者位寬之和即為SPI單幀長。

//`define SPI_LINE //是否是三線SPI `define SPI_FRAME_WIDTH 16 //SPI一幀長度為16 `define SPI_INS_WIDTH 8 //SPI指令長 `timescale 1ns/1ps //// module spi_slave ( input i_clk , //work clk input i_rst_n , input i_spi_clk , //SPI clk input i_spi_cs , //SPI cs `ifdef SPI_LINE //條件編譯 inout io_spi_sdio `else input i_spi_mosi , //SPI mosi output o_spi_miso //SPI miso `endif ); //位寬計算函數(shù) function integer clogb2 (input integer depth); begin for (clogb2=0; depth>0; clogb2=clogb2+1) depth = depth >>1; end endfunction reg r_cs = 1'b1; //打一拍 always @(posedge i_clk) begin r_cs <= i_spi_cs; end reg [1:0] r_spi_clk_edge = 2'b00; //SPI clk邊沿檢測 always @(posedge i_clk) begin r_spi_clk_edge <= {r_spi_clk_edge[0],i_spi_clk}; end //always reg [clogb2(`SPI_FRAME_WIDTH-1)-1:0] r_spi_cnt = 'd0; always @(posedge i_clk) begin if (r_cs) //cs為高則歸零 r_spi_cnt <= 'd0; else if (r_spi_clk_edge == 2'b10) //下降沿才計數(shù) r_spi_cnt <= r_spi_cnt + 'd1; end ////指令鎖存 reg [`SPI_INS_WIDTH-1:0] r_ins = 'd0; always @(posedge i_clk) begin if ((~r_cs) && (r_spi_clk_edge == 2'b01)) //上升沿鎖存數(shù)據(jù) begin if ((r_spi_cnt >= 0) && (r_spi_cnt <= `SPI_INS_WIDTH-1)) `ifdef SPI_LINE //條件編譯 r_ins <= {r_ins[`SPI_INS_WIDTH-2:0],io_spi_sdio}; `else r_ins <= {r_ins[`SPI_INS_WIDTH-2:0],i_spi_mosi}; `endif end end ////數(shù)值寫入 reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_data_rx = 'd0; always @(posedge i_clk) begin if ((~r_cs) && (r_spi_clk_edge == 2'b01)) //上升沿鎖存數(shù)據(jù) begin if (r_spi_cnt >= `SPI_INS_WIDTH) `ifdef SPI_LINE r_data_rx <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],io_spi_sdio}; `else r_data_rx <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],i_spi_mosi}; `endif end end ////用戶寄存器定義 reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_reg0 = 'd0; reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_reg1 = 'd0; reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_reg2 = 'd0; reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_reg3 = 'd0; //// always @(posedge i_clk,negedge i_rst_n) begin if (~i_rst_n) begin r_reg0 <= 'd0; r_reg1 <= 'd0; r_reg2 <= 'd0; r_reg3 <= 'd0; end else if ((~r_ins[`SPI_INS_WIDTH-1]) && (r_spi_cnt == (`SPI_FRAME_WIDTH-1)) && (~r_cs) && (r_spi_clk_edge == 2'b01)) begin `ifdef SPI_LINE case (r_ins[`SPI_INS_WIDTH-2:0]) 'd0:begin r_reg0 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],io_spi_sdio}; end 'd1:begin r_reg1 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],io_spi_sdio}; end 'd2:begin r_reg2 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],io_spi_sdio}; end 'd3:begin r_reg3 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],io_spi_sdio}; end endcase `else case (r_ins[`SPI_INS_WIDTH-2:0]) 'd0:begin r_reg0 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],i_spi_mosi}; end 'd1:begin r_reg1 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],i_spi_mosi}; end 'd2:begin r_reg2 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],i_spi_mosi}; end 'd3:begin r_reg3 <= {r_data_rx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],i_spi_mosi}; end endcase `endif end end ////寄存器值讀出 reg [`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1:0] r_data_tx = 'd0; always @(posedge i_clk) begin if (r_ins[`SPI_INS_WIDTH-1] && (~r_cs) && (r_spi_clk_edge == 2'b10)) begin if (r_spi_cnt == (`SPI_INS_WIDTH-1)) begin case (r_ins[`SPI_INS_WIDTH-2:0]) 'd0:begin r_data_tx <= r_reg0; end 'd1:begin r_data_tx <= r_reg1; end 'd2:begin r_data_tx <= r_reg2; end 'd3:begin r_data_tx <= r_reg3; end endcase end else r_data_tx <= {r_data_tx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-2:0],1'b0}; end end ////讀取輸出 `ifdef SPI_LINE assign io_spi_sdio = (r_ins[`SPI_INS_WIDTH-1]) ? (((r_spi_cnt>=`SPI_INS_WIDTH) && (r_spi_cnt<`SPI_FRAME_WIDTH)) ? r_data_tx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1] : 1'bz) : 1'bz; `else assign o_spi_miso = ((r_spi_cnt>=`SPI_INS_WIDTH) && (r_spi_cnt<`SPI_FRAME_WIDTH)) ? r_data_tx[`SPI_FRAME_WIDTH-`SPI_INS_WIDTH-1] : 1'b0; `endif endmodule // end the spi_slave model

SPI master

spi master內部僅僅封裝SPI驅動,寫入值讀出控制由上層控制,這部分邏輯很simple,不贅述。用戶只需給入SPI幀及控制使能即可。

用戶只需修改parameter參數(shù):(1)單幀長;(2)指令長;(3)數(shù)據(jù)長;(4)工作時鐘;(5)SPI clk。

實現(xiàn)不使用狀態(tài)機,采用線性序列計數(shù)法。

//`define SPI_LINE //是否是三線SPI

`timescale 1ns/1ps

module spi_master

#(parameter p_spi_frame_width = 16, //SPI單幀長度

parameter p_spi_ins_width = 8 , //指令長度

parameter p_spi_data_width = 8 //讀出數(shù)據(jù)長度

)

(

input i_clk , //系統(tǒng)時鐘

input i_rst_n ,

input i_flag , //檢測到flag的上升沿則啟動一次傳輸,一個時鐘周期即可

input [p_spi_frame_width-1:0] i_spi_data ,

output o_spi_cs ,

output o_spi_clk ,

`ifdef SPI_LINE //條件編譯

inout io_spi_sdio ,

`else

input i_spi_miso , //SPI miso

output o_spi_mosi , //SPI mosi

`endif

output o_transfer_done , //單次傳輸完成

output [p_spi_data_width-1:0] o_spi_data //讀取數(shù)據(jù)

);

parameter p_clk_fre = 200; //XXM時鐘頻率

parameter p_spi_clk_fre = 0.5*1000; //SPI 時鐘速率,表示1M

parameter p_clk_div = p_clk_fre * 1000/p_spi_clk_fre/2-1;

parameter p_spi_cnt_max = p_spi_frame_width*2-1;

parameter p_spi_ins_max = p_spi_ins_width*2-1;

//位寬計算函數(shù)

function integer clogb2 (input integer depth);

begin

for (clogb2=0; depth>0; clogb2=clogb2+1)

depth = depth >>1;

end

endfunction

//把最大值賦值給線型,直接用p_clk_div仿真有問題,但實際上板是可以的

wire [clogb2(p_clk_div)-1:0] w_clk_div;

assign w_clk_div = p_clk_div;

////時鐘分頻

reg [clogb2(p_clk_div)-1:0] r_cnt_div = 'd0;

always @(posedge i_clk)

begin

if (r_cnt_div == w_clk_div)

r_cnt_div <= 'd0;

else

r_cnt_div <= r_cnt_div + 'd1;

end //always

wire w_clk_en; //分頻時鐘使能

assign w_clk_en = (r_cnt_div == w_clk_div) ? 1'b1 : 1'b0;

reg [1:0] r_flag_edge = 2'b00;

reg [clogb2(p_spi_cnt_max)-1:0] r_spi_cnt = 'd0;

always @(posedge i_clk) //flag邊沿檢測

begin

r_flag_edge <= {r_flag_edge[0],i_flag};

end

//flag信號展寬到低速時鐘域

reg r_flag_enlarge = 1'b0;

always @(posedge i_clk)

begin

if (r_flag_edge == 2'b01) //上升沿拉高

r_flag_enlarge <= 1'b1;

else if (r_spi_cnt == p_spi_ins_max) //足夠長的高電平才拉低

r_flag_enlarge <= 1'b0;

end

reg [1:0] r_flag_enlarge_edge = 2'b00;

always @(posedge i_clk)

begin

if (w_clk_en)

r_flag_enlarge_edge <= {r_flag_enlarge_edge[0],r_flag_enlarge};

end

reg r_cs = 1'b1;

always @(posedge i_clk)

begin

if (w_clk_en)

begin

if (r_flag_enlarge_edge == 2'b01) //檢測到需要進行SPI操作

r_cs <= 1'b0;

else if (r_spi_cnt == p_spi_cnt_max) //計數(shù)到最大值表示一次SPI完成

r_cs <= 1'b1;

end

end

always @(posedge i_clk)

begin

if (w_clk_en)

begin

if(~r_cs) //在操作區(qū)間計數(shù)

r_spi_cnt <= r_spi_cnt + 'd1;

else

r_spi_cnt <= 'd0;

end

end

////數(shù)據(jù)傳輸段

reg [p_spi_frame_width-1:0] r_data = 'd0;

always @(posedge i_clk)

begin

if (w_clk_en)

begin

if (r_flag_enlarge_edge == 2'b01) //上升沿刷入

r_data <= i_spi_data;

else if (r_spi_cnt[0] == 1'b1) //數(shù)據(jù)移動

r_data <= {r_data[p_spi_frame_width-2:0],1'b1};

end

end

////數(shù)據(jù)讀取段

reg [p_spi_data_width-1:0] r_data_read = 'd0;

always @(posedge i_clk)

begin

if (w_clk_en)

begin

if (i_spi_data[p_spi_frame_width-1] && (r_spi_cnt > p_spi_ins_max) && (r_spi_cnt[0] == 1'b0)) //是讀

`ifdef SPI_LINE

r_data_read <= {r_data_read[p_spi_data_width-2:0],io_spi_sdio};

`else

r_data_read <= {r_data_read[p_spi_data_width-2:0],i_spi_miso};

`endif

end

end

////SPI輸出段

assign o_spi_cs = r_cs;

assign o_spi_clk = r_cs ? 1'b0 : r_spi_cnt[0];

////SPI SDIO的輸入輸出切換

`ifdef SPI_LINE

assign io_spi_sdio = (i_spi_data[p_spi_frame_width-1]) ? (((r_spi_cnt >= 'd0) && (r_spi_cnt <= p_spi_ins_max)) ? r_data[p_spi_frame_width-1] : 1'bz ) : r_data[p_spi_frame_width-1];

`else

assign o_spi_mosi = r_data[p_spi_frame_width-1];

`endif

assign o_transfer_done = ((~r_cs) && (r_spi_cnt == p_spi_cnt_max)) ? 1'b1:1'b0;

assign o_spi_data = r_data_read;

endmodule // end the spi_master model

?

?

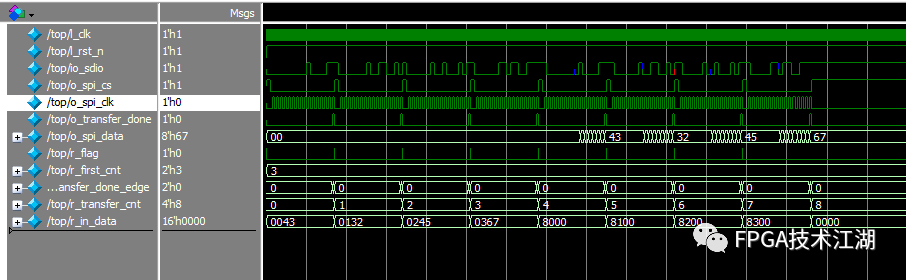

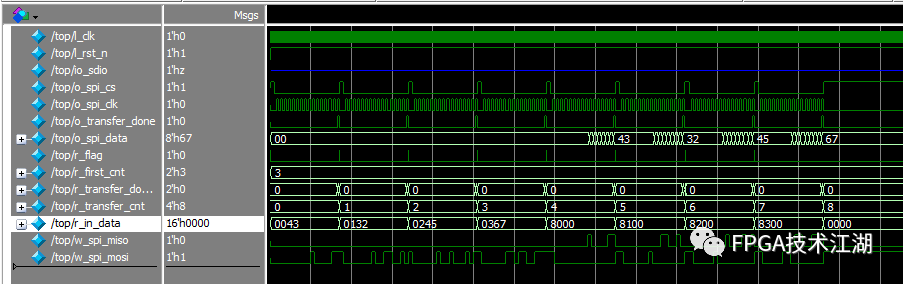

仿真如下所示:寫入四個寄存器值,再讀出。

仿真代碼如下:

?

?

`define TRANSFER_NUMBER 8 //操作數(shù)為4 `define DATA 8'ha5 //`define SPI_LINE timeunit 1ns; timeprecision 1ps; module top; parameter p_sim_end_time = 1000000; //ns logic l_clk = 1'b0; always #2.5 l_clk = ~l_clk; ////復位 logic l_rst_n = 1'b0; initial begin #100 l_rst_n = 1'b1; end wire io_sdio; wire o_spi_cs; wire o_spi_clk; wire o_transfer_done; wire [7:0] o_spi_data; ////多個數(shù)據(jù)操作模式 reg r_flag = 1'b0; reg [1:0] r_first_cnt = 2'b00; always @(posedge l_clk,negedge l_rst_n) begin if (~l_rst_n) r_first_cnt <= 2'b00; else if (r_first_cnt == 2'd3) r_first_cnt <= r_first_cnt; else r_first_cnt <= r_first_cnt + 2'd1; end reg [1:0] r_transfer_done_edge = 2'b00; always @(posedge l_clk) begin r_transfer_done_edge <= {r_transfer_done_edge[0],o_transfer_done}; end reg [3:0] r_transfer_cnt = 4'd0; always @(posedge l_clk) begin if ((r_first_cnt == 2'd2) && (r_transfer_cnt < `TRANSFER_NUMBER)) r_flag <= 1'b1; else if ((r_transfer_done_edge == 2'b10) && (r_transfer_cnt < `TRANSFER_NUMBER-1)) r_flag <= 1'b1; else r_flag <= 1'b0; end always @(posedge l_clk) begin if (r_transfer_done_edge == 2'b10) r_transfer_cnt <= r_transfer_cnt + 'd1; end reg [15:0] r_in_data = 16'd0; always @(*) begin if (~l_rst_n) //仿真不執(zhí)行此段仿真會有問題 r_in_data = 16'h0000; else begin case(r_transfer_cnt) 4'd0:begin r_in_data = {8'h00,8'h43}; end 4'd1:begin r_in_data = 16'h0132; end 4'd2:begin r_in_data = 16'h0245; end 4'd3:begin r_in_data = 16'h0367; end 4'd4:begin r_in_data = 16'h8000; end 4'd5:begin r_in_data = 16'h8100; end 4'd6:begin r_in_data = 16'h8200; end 4'd7:begin r_in_data = 16'h8300; end default:begin r_in_data = 16'h0000; end endcase end end wire w_spi_miso; wire w_spi_mosi; spi_master inst_spi_master ( .i_clk (l_clk), .i_rst_n (), .i_flag (r_flag), .i_spi_data (r_in_data), .o_spi_cs (o_spi_cs), .o_spi_clk (o_spi_clk), `ifdef SPI_LINE .io_spi_sdio (io_sdio), `else .i_spi_miso (w_spi_miso), .o_spi_mosi (w_spi_mosi), `endif .o_transfer_done (o_transfer_done), .o_spi_data (o_spi_data) ); spi_slave inst_spi_slave ( .i_clk (l_clk), .i_rst_n (l_rst_n), .i_spi_clk (o_spi_clk), .i_spi_cs (o_spi_cs), `ifdef SPI_LINE .io_spi_sdio (io_sdio) `else .i_spi_mosi (w_spi_mosi), .o_spi_miso (w_spi_miso) `endif ); initial begin #p_sim_end_time $stop; end endmodule

三線SPI:

四線SPI:

?

可以看到讀寫是一致的,驗證通過。

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論