將區(qū)塊劃分為可管理的片段變得越來越難,但新的工具和方法正顯示出前景。

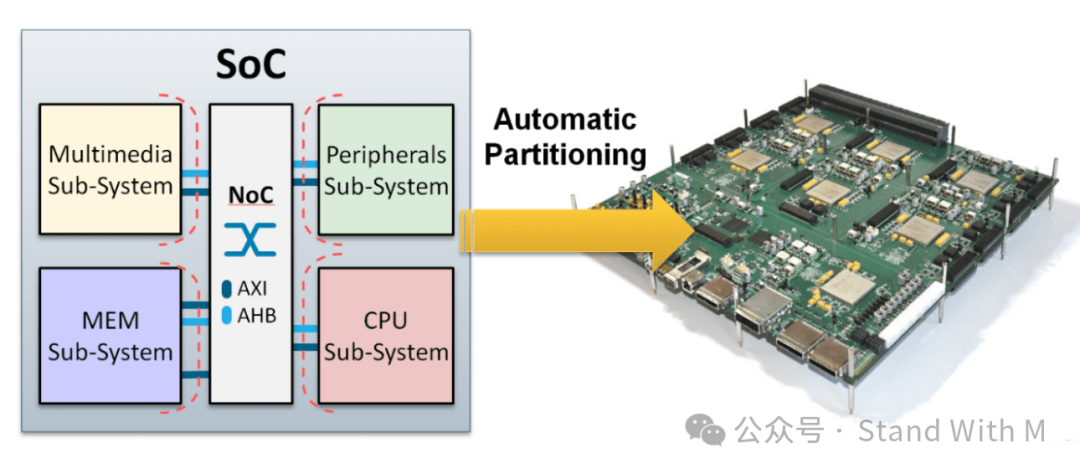

ASIC 和 SoC 設(shè)計的多 FPGA 原型驗證使驗證團隊能夠?qū)崿F(xiàn)仿真技術(shù)中最高的時鐘速率,但為原型驗證設(shè)置設(shè)計非常復(fù)雜且具有挑戰(zhàn)性。這正是機器學習和其他新方法開始提供幫助的地方。 根本問題在于設(shè)計變得如此龐大和復(fù)雜,以至于必須將其分割成更易于管理的部分。但碎片的數(shù)量在成倍增加,分割的難度也在成比例上升。

Cadence 公司產(chǎn)品管理部總監(jiān) Juergen Jaeger 說:“你需要將一大團邏輯進行分割,而分割的方式最重要的是要保留功能,也就是說不能破壞設(shè)計中的任何部分。”無論是仿真器還是 FPGA 原型,你都希望有效地利用所劃分的資源,并盡可能實現(xiàn)最佳性能。這就像在空中玩弄多個球一樣。

由于新一代 FPGA 剛剛出現(xiàn),該行業(yè)正處于一個有趣的關(guān)頭。“對于設(shè)計規(guī)模相對較小的用戶來說,這確實是一個很好的機會。Synopsys公司產(chǎn)品營銷高級總監(jiān)Johannes Stahl表示:”對于以前不得不將設(shè)計分割到兩個FPGA中的用戶來說,這是一個絕佳的機會,因為他們省去了分割,并獲得了更好的結(jié)果。“例如,以前一個設(shè)計的運行速度是 20MHz,而現(xiàn)在可以達到 50MHz,所以這是一個巨大的影響。在這些新型 FPGA 上線的許多情況下,這種情況還會繼續(xù)發(fā)生。”

Aldec 硬件驗證產(chǎn)品經(jīng)理 Krzysztof Szczur 說:“換句話說,邏輯密度的大幅提高使得在單個 FPGA 芯片中實現(xiàn)更小的 SoC 設(shè)計成為可能,并以接近實際運行條件的時鐘頻率運行原型。 Aldec 硬件驗證產(chǎn)品經(jīng)理 Krzyztof Szczur 說:”與此同時,由于當今最先進的 FPGA 實際上并不是一個芯片,因此出血邊緣器件增加了另一個層次的復(fù)雜性。

Jaeger說:“賽靈思和英特爾/Altera的高端FPGA現(xiàn)在包含多個裸片,其中的多個芯片用線連接,因此FPGA內(nèi)部也有分區(qū)。Jaeger 說:”作為額外的復(fù)雜性,如果你現(xiàn)在正在研究功能(必須具備的功能)、性能和資源的有效利用,那么分區(qū)算法就會試圖采用‘最小切割算法’。它們試圖盡量減少必須在多個分區(qū)之間傳輸?shù)?a target="_blank">信號數(shù)量。除此之外,進行分區(qū)的工程師還試圖平衡每個 FPGA 的利用率,這樣就不會出現(xiàn)一個 FPGA 滿載 90%,而另一個只滿載 10%的情況,因為這會對性能產(chǎn)生負面影響。“

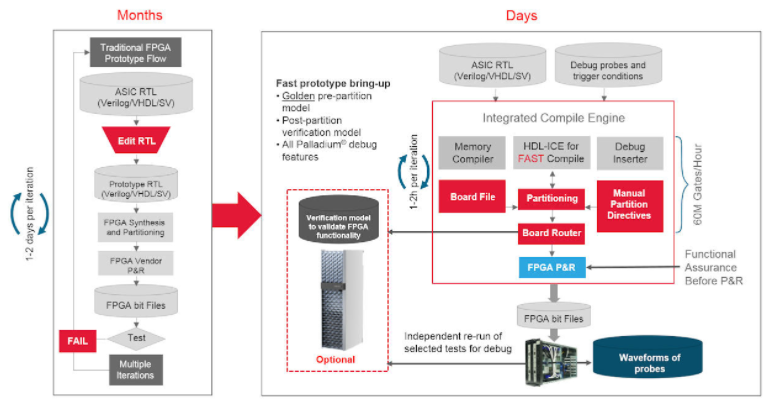

當然,在有些情況下,也無法實現(xiàn) Stahl 所提到的同樣顯著的效果。例如,一些公司在使用自己的電路板進行原型開發(fā)時,會遇到多 FPGA 分區(qū)以外的挑戰(zhàn),具體來說,就是因為需要添加調(diào)試信號,所以要反復(fù)進行多 FPGA 分區(qū)。

Stahl 說:”如果你必須在一個主要是手動的流程中引入調(diào)試信號,你就必須將它們引入引腳,這就會影響分區(qū)。Stahl 說:“因此,你必須重新運行分區(qū),這相當痛苦。一位用戶就非常討厭這樣做,因為他永遠無法預(yù)測下一次分區(qū)運行的時間會在什么時候結(jié)束,而他卻可以再次把原型提供給用戶。由此可見,它與調(diào)試確實息息相關(guān)。調(diào)試和自動分區(qū)對于使用原型設(shè)計的用戶來說是同一個主題。這一切都必須協(xié)同工作”。

多 FPGA 原型驗證的另一個挑戰(zhàn)是分區(qū)的連接。Aldec 的 Szczur 說:“隨著邏輯密度的不斷提高,F(xiàn)PGA 被封裝在更大的封裝中,從而提供了更多的 I/O。”然而,I/O 的增加并不像邏輯資源那樣引人注目。例如,最大的 Virtex UltraScale 提供 1,456 個常規(guī) I/O,比 Virtex-7 系列多出約 21%。為了縮小這一差距,F(xiàn)PGA 供應(yīng)商為現(xiàn)代 FPGA 配備了高速串行 I/O(如 XCVU440 中的 48 條 GTH 線),從而提高了連接帶寬。這些 I/O 通常與用于 PCI Express、USB 3.0 或 QSFP 等標準接口的 PHY 相耦合。在某些情況下,它們也可用于多 FPGA 原型中的芯片間連接,但在這種情況下,它們的使用僅限于實現(xiàn)專用協(xié)議握手的事務(wù)接口,而且最好使用突發(fā)傳輸,以最大限度地減少此類鏈路延遲增加的影響。此外,在高端 FPGA 中,由于支持低壓差分信令 (LVDS),加上專用的串行器/解串器 (SerDes) 邏輯,標準 I/O 被設(shè)計為以更高的數(shù)據(jù)傳輸速率進行傳輸,從而促進了此類鏈接的實現(xiàn)。不過,在 LVDS 模式下同時設(shè)置 GTH/GTX 或標準 I/O 可能比較麻煩,如果由分區(qū)軟件自動進行設(shè)置,則可以節(jié)省大量時間,減少麻煩。

如果設(shè)計規(guī)模大于單個 FPGA,則必須進行分區(qū),每個分區(qū)都要與單個 FPGA 的容量相匹配。有兩個目標:第一個目標是將 FPGA 資源利用率控制在一個閾值內(nèi),以確保流暢的布局布線。第二個目標是盡量減少分區(qū)之間的互連,這是影響原型速度的最重要因素。

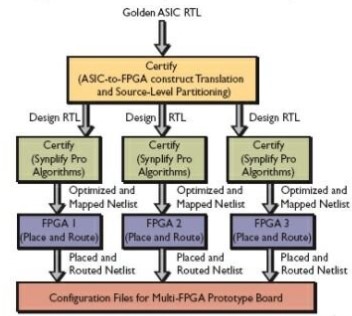

Szczur 說:“在兩個 FPGA 的情況下,這個過程相對簡單,但在增加下一個分區(qū)時,難度就會迅速增加,尤其是在設(shè)計結(jié)構(gòu)(層次結(jié)構(gòu))與原型板布局不一致的情況下。”一種方法是手動分區(qū),這需要更改設(shè)計源。分區(qū)塊在 HDL 中創(chuàng)建,以匹配原型驗證板資源和連接性。由于 FPGA I/O 的限制,每個分區(qū)都必須與互連物理層和多路復(fù)用器或串行器的定制實現(xiàn)進行手動封裝。這種方法不僅容易出錯、難以擴展或涵蓋設(shè)計變更,而且需要修改設(shè)計,從而對 ASIC 后端綜合優(yōu)化產(chǎn)生負面影響。為了降低這種風險,可以為 FPGA 原型和 ASIC 設(shè)計流程保留不同的 HDL 源集和配置。但這樣一來,在 FPGA 原型驗證過程中真正驗證的是什么就值得懷疑了。比手動分區(qū)好得多的方法是使用編譯原始設(shè)計 HDL 源文件的軟件,這有助于在設(shè)計層次結(jié)構(gòu)中對模塊實例進行分組,從而將其分成不同的分區(qū)“。

圖 1:自動分區(qū)工具。來源:Aldec

執(zhí)行分區(qū)

分區(qū)由軟件架構(gòu)師完成,他們負責設(shè)計整體結(jié)構(gòu)并確定分區(qū)算法的工作方式。這些架構(gòu)師由工程師團隊提供支持,工程師團隊負責具體實施。”有些人只負責引腳復(fù)用,例如分區(qū)之間的連接,“Cadence 的 Jaeger 說。”另一些人則只負責貼片,專注于如何拆分。然后再細分到各個專家小組“。

這在很大程度上取決于設(shè)計/驗證團隊的規(guī)模。”他解釋說:“架構(gòu)是實現(xiàn)良好分區(qū)的關(guān)鍵。”第二重要的可能是全局布局。如何將不同的設(shè)計塊放置到不同的 FPGA 中。連接和引腳復(fù)用是機械工作。沒有太多的創(chuàng)造性。它只是實現(xiàn)它。正如你所能想象的那樣,當你有多個東西需要一起工作時,你總得從某個地方入手。你必須把木樁放在地上,‘我把這個放在這里,把那個放在那里,再把那個放在那里。讓我們看看現(xiàn)在它們是如何結(jié)合在一起的。所有的算法都是以種子或隨機起點為基礎(chǔ)的。然后,這些算法經(jīng)過多次迭代,對起點進行變化“。

在這一領(lǐng)域,我們正在努力提高可預(yù)測性,包括機器學習。”預(yù)測算法在其中發(fā)揮了作用,有助于提高可預(yù)測性,因為這樣做的目的是,當你提高了可預(yù)測性,你就不需要那么多的迭代,不需要那么多的重復(fù),就能得到好的結(jié)果。這就是為什么我們希望將更多的機器學習引入其中,“Jaeger 說。

這是一個計算能力問題,也是一個時間問題。”這其中很重要的一點是,并不是每個問題都能解決。比方說,你有一個特定的設(shè)計,你說’我想把它裝進四個 FPGA‘。但由于種種原因,可能無法實現(xiàn)。可能有太多的門。中間的連接可能太多,也許還有其他原因。當你熟悉 FPGA 時,往往要花上好幾天時間才能發(fā)現(xiàn)它無法進行布局布線,而且沒有解決方案。您需要盡快了解情況。ML 算法能在幾分鐘或半小時后幫助你,所以你不用等上兩三天,直到你的軟件說’哎呀,我做不了‘。他補充說:“你可以提前知道,也可以提前做出改變。

不過,目前還不清楚該行業(yè)是否已準備好在這一領(lǐng)域應(yīng)用機器學習。”雖然機器學習可以實現(xiàn),但挑戰(zhàn)在于你需要有大量的運行來優(yōu)化這種機器學習,“Stahl 說。”如果你花費了足夠的計算能力,你就可以進行優(yōu)化,運行許多次,然后找到一個更優(yōu)化的版本。因此,就像任何本質(zhì)上略帶啟發(fā)式的優(yōu)化問題一樣--放下電纜本質(zhì)上也略帶啟發(fā)式--人工智能算法可以使其受益。今天我們還沒有進入市場,但未來一定會進入市場。

分區(qū)最佳實踐

在構(gòu)建 FPGA 原型時,有一些關(guān)鍵的注意事項需要牢記。

Imagination Technologies 開發(fā)平臺團隊首席系統(tǒng)架構(gòu)師 Daniel Aldridge 說:“最有用的第一種方法是在設(shè)計時考慮到 FPGA。”作為 FPGA 工程師,我們傾向于你計劃放入 FPGA 的 IP 核是’FPGA 友好型‘的,這意味著它沒有會大量消耗 FPGA 資源或難以在 FPGA 之間拆分的組件。如果設(shè)計能事先考慮到這些因素,如果最終產(chǎn)品將被放入 FPGA 或至少是其變體,那就更好了。如果 IP 核必須為硅設(shè)計,那么硅面積和速度就是首要考慮因素。那么,我們就必須將就。有時,這就意味著用經(jīng)過正式測試的、可用于 FPGA 的同類元件來替換同類元件。歸根結(jié)底,就是’你能不能讓進入 FPGA 的元件盡可能對 FPGA 友好?

在多 FPGA 平臺上,如果設(shè)計必須拆分,那么最好能在已注冊的邊界上拆分,這樣就有了協(xié)議。

Aldridge 說:“這樣就可以在 FPGA 之間拉動寄存器到寄存器。Aldridge 說:”它為你提供了一條引腳數(shù)相對較少的總線,而你最終不得不拆分這條總線。如果是像 AMBA 總線這樣的總線,引腳數(shù)不會太多。雖然仍有數(shù)百個,但不會達到數(shù)萬個。但是,這并不總是可能的。因此,我們需要在 FPGA 和 PCB 上拆分設(shè)計,而這些設(shè)計在硅片中一直是相鄰的。這就是我們開始尋找工具來幫助實現(xiàn)這一過程自動化的原因。如果要拆分通過有效協(xié)議連接的高級模塊,手工編輯這些子組件的實例是一件相對容易的事情。如果你要開始拆分次層級的區(qū)塊,或者拆分許多大型區(qū)塊,這些區(qū)塊之間有數(shù)千或數(shù)萬個信號,那么我們就需要使用工具來幫助實現(xiàn)流程自動化。這可以幫助你自動計算模塊將占用的面積,從而計算出哪些模塊應(yīng)該放在哪里,還可以幫助你計算出哪些信號將在哪些FPGA之間傳輸,以及需要進行哪些復(fù)用。這就是我們開始討論的地方,現(xiàn)在最大的 FPGA 有幾千個 I/O 引腳。但是,如果你要放一萬個信號,你仍然需要進行某種時分復(fù)用,將信號從一個 IP 塊或 IP 的子塊傳輸?shù)搅硪粋€塊。

區(qū)塊大小對分區(qū)也有很大影響。

Aldridge 說:“如果你能讓一個組件的大小不超過 FPGA,那么你的工作就會變得更輕松。”在 ASIC 領(lǐng)域,這就是子塊可能占用的平方毫米面積。然后,從這些大得多的設(shè)計的 ASIC 布局出發(fā),開始考慮這些塊之間的互連是什么。從 FPGA 的角度來看,當你進行原型設(shè)計時,我們希望在設(shè)計階段就考慮到這一點。從一開始,當 IP 核的架構(gòu)完成后,你就應(yīng)該考慮應(yīng)該將其分解到哪個層次,應(yīng)該有哪些分層。是否應(yīng)該在它們之間商定一個最大 I/O 或通用 I/O 接口?確保有流水線階段,因為這將有助于 FPGA 時序和 ASIC 時序。希望你能事先說服設(shè)計人員,這對大家都有好處。

多 FPGA 原型開發(fā)將走向何方?

如今,設(shè)計原型的依賴性如此之大,下一步的發(fā)展方向也在不斷變化。

EDA 領(lǐng)域主要解決的一個問題是,當連接多個分區(qū)時,F(xiàn)PGA 之間的邊界有不同的布線方式。這包括如何進行引腳多路復(fù)用,以及數(shù)據(jù)傳輸后的轉(zhuǎn)換速度。

Jaeger 說:“越來越多的引腳復(fù)用方案采用混合方案。”你可以采用非常傳統(tǒng)的異步引腳多路復(fù)用。你以相對較低的速度運行線路,然后超頻,這樣就可以在另一端恢復(fù)數(shù)據(jù)。如果引腳多路復(fù)用率較小,這種方法就非常有效。它的延遲非常低,因此線路中的延遲非常短。如果你有成百上千個信號需要通過一條線發(fā)送,這將是一個限制因素。因此,你需要使用基于 SerDes 的高速連接技術(shù),在這種技術(shù)中,你基本上是在運行一條傳輸線,并以千兆赫茲的速度在電線上運行。這樣做的缺點是,設(shè)置這些端點的串行化/反串行化會增加延遲,因此只有在引腳復(fù)用率非常高的情況下才有意義“。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論