本款帶LDO架構的15 W無線充電接收器參考平臺采用我們MWPR1516接收控制器IC,能夠管理和執行實施無線充電接收器解決方案所需的全部功能。該解決方案經過高度優化,采用內部LDO控制器,能夠以

2018-06-25 17:42:44

將LVDS信號傳輸給液晶面板。液晶面板的LVDS接收器再對信號做轉換處理并顯示。

另外需要給液晶面板提供液晶的背光,背光電路一般放在驅動板,主控通過PWM信號對面板背光進行調節。若液晶面板帶觸摸功能

2023-06-05 17:31:08

)。從這些產品的數據表中我可以看出,對于大多數上述FPGA來說,這應該是可行的。然而,該設計可以使用比標準1.25V共模低的共模電壓。這可能是600mV的共模電壓。當共模電壓從標稱值1.25V降低時,FPGA上LVDS接收器的速度是否會降低?

2020-06-16 08:44:15

同步LVDS時鐘對。接收方接收到該串行LVDS數據,對其進行反序列化,并將其對齊到原始單詞邊界,生成7個并行LVTTL數據位。7:1發送器將7個LVTTL并行數據位串行化為一個LVDS數據位,并將

2019-12-11 09:51:59

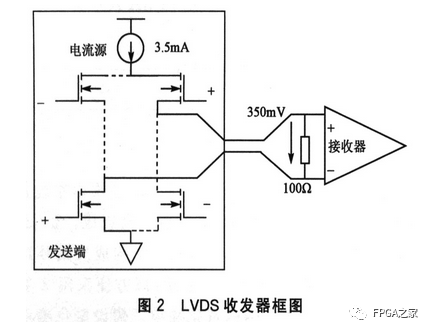

的目的是為點對點拓撲中的驅動器和接收器提供通用電氣層規范。點對點拓撲是一種半雙工鏈路,包含支持差分端接的單個驅動器及接收器。下圖 1 是一個點對點配置:圖 1:點對點下一種架構是多支路拓撲。LVDS

2022-11-22 07:43:47

管腳懸空,所有未使用的LVDS和TTL輸出管腳懸空,將未使用的TTL發送/驅動器輸入和控制/使能管腳接電源或地。2.6 媒質(電纜和連接器)選擇2.7 在噪聲環境中提高可靠性設計LVDS 接收器在內部

2011-02-23 09:55:17

那位老師可以幫我開發一個調頻調幅同步接收器,有意者加微信***有報酬最少5000人民幣。

2022-11-16 14:23:46

接收器子系統的電路是怎樣組成的?接收器子系統有哪幾個主要誤差源?

2021-05-21 06:38:39

接收器技術的最新發展:接收器百年創新史選編第2部分:接收器架構

2021-01-21 07:17:17

接收器百年創新史選編

2021-01-26 07:27:05

您好:

我準備用FPGA來對接AD9122,FPGA發送LVDS數據,DAC接收。

如果FPGA是LVDS接收的話,FPGA可以使能內部的差分電阻,就是在P-N之間使能了一個100歐姆的電阻

2023-12-21 08:30:31

在使用HDMI/DVI 接收器時,你有遇到過以下問題嗎? HDMI Receiver 產品中的 EDID 必須要使用嗎?將 將 HDMI Receiver 的輸出連接到顯示設備后 ,一直是藍屏狀態

2017-06-25 14:05:51

、Adobe RGB、Adobe YCC 601和xvYCC擴展顏色范圍兼容CEC 1.4·HDMI接收器最小化傳輸差分信號(TMDS)時鐘頻率:165 MHz(最大值)24位輸出像素總線·音頻支持S/PDIF

2015-09-15 14:26:05

AS3933是15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能奧地利微電子推出業內性能最出色的15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能。 3

2018-11-26 09:59:05

`AS3933是15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能奧地利微電子推出業內性能最出色的15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能。3

2018-12-21 15:39:15

3)參考600Mhz時鐘通過LVDS發送數據FPGA1)接收單行lvds數據2)我使用“Camera Link接收器”和“相位檢測器”和“重新定時”選項。3)我在FPGA(PLL)上生成600MHz

2019-07-17 06:40:58

特征 ●單電源+3.3V電源 ●B/LVDS接收器輸入接受LVPECL信號 ●三態輸出 ●信號丟失(LOS)引腳檢測非驅動總線 ●接收器輸入閾值《±100 mV ●1.4ns的快速

2020-07-14 14:48:54

嗨,我集成了dp v1.1接收器IP,項目屏幕截圖如下。和display_port_sink_policy_maker沒關系。我使用SDK創建比特流,然后使用download.bit對FPGA進行

2020-07-19 07:44:20

1 概述GM8284DD 型 28 位 LVDS 圖像收器主要用于視頻/圖像傳輸中的接收部分,實現的功 能是將高速串行 LVDS 信號解碼為并行 TTL 數據,完成數據的解碼功能。該器件可將 4

2020-12-03 10:02:18

過程中產生比特錯誤。在下圖 3 中,我舉了兩個實例,用以說明如何在 CML 驅動器、LVPECL 驅動器和 LVDS 接收器之間實施 AC 耦合。圖3:不同接口的互連連接任意兩個不同接口時可使用這種相同

2018-09-13 14:28:38

MS90C104 ——+3.3V 175MHz 的 30bit 平板顯示器(FPD)LVDS 信號接收器功能概述 MS90C104 芯片能夠將 5 通道的低壓差分信號(LVDS)轉換成 35bit

2021-01-10 17:48:07

:BGA鍵都很好。經過這些步驟后,看起來內部的Virtex LVDS接收器在內部出現問題。 A / D和Virtex電源均來自相同的3.3V電源,因此我不認為這是電源競爭問題,特別是因為A / D輸出

2020-05-28 13:32:49

類型:接收器 協議類別:LVDS 驅動器/接收器數:0/4 數據速率:400Mbps

2023-03-28 18:28:02

你好,我支持現有的設計,其中有一個攝像機鏈接接收器(3個LVDS數據線和1個LVDS幀時鐘)。這似乎與Xapp1064的案例1相匹配。數據線以315Mbps運行。輸入時鐘沒有放在CLK引腳上,因此

2019-02-14 07:23:17

大家好這是我第一次發布東西,我正在設計一個lvds發射器,我需要知道virtex-6 FPGA中lvds接收器的輸入電容能夠測試我的發射器嗎?我查看了數據手冊,發現輸入芯片電容為8pF,這與virtex-6中lvds接收器的輸入電容相同。提前致謝易卜拉欣·艾哈邁德

2020-06-11 06:07:12

AS3933是15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能奧地利微電子推出業內性能最出色的15–150kHz頻率范圍、3通道低頻喚醒接收器,且具備自動天線調諧功能。3通道

2018-05-12 15:03:49

嗨,每個人,我都使用V4 FPGA從CMOS接收LVDS數據。同時,CMOS輸出一個LVDS時鐘資源'dck'作為同步時鐘。數據在上升沿和下降沿傳輸,如下圖所示。 我清楚地知道在verilog

2020-04-20 10:21:22

關于GPS接收器測試的分析

2021-05-08 07:05:37

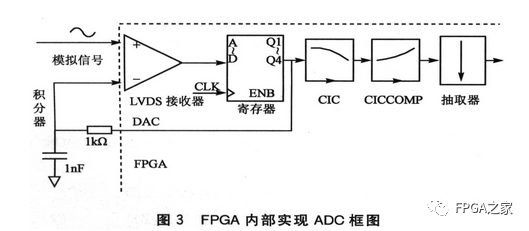

,所以500M采樣率工作時,LVDS數據輸出的隨路時鐘是250Mhz,一般的芯片沒有可以的達到該速率的接收器,所以必須使用FPGA來作為該芯片的數據接收與后續的信號處理。 明德揚AD9684 ADC接口

2019-12-06 15:33:22

哪位大神給個基于FPGA的IR接收器VHDL語言的程序

2017-05-20 20:43:57

你好!我正在使用斯巴達6 lx100與斯巴達6 lx9進行通信,它位于不同的主板上。它們之間的連接是點對點的,通過30厘米電纜和100Mhz LVDS信號。我應該使用外部驅動器和接收器還是fpga

2019-06-24 15:44:23

于智能手機應用。 本文將介紹基于FPGA的無線充電器接收器系統的解決方案。無線充電器接收器嚴格遵循最新的WPC Qi標準。接收器系統包含一個模擬模塊和一個FPGA模塊。模擬模塊由分立式組件組成,包括全橋

2018-09-27 15:35:58

的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種

2019-07-29 07:03:50

22.4Gbps(Kintex-7).2. 1對LVDS接收時鐘+16對LVDS接收數據.本人可以提供FPGA源代碼.同時還可以在Xilinx評估板ML555/ML605/KC705上演示驗證.如有高速LVDS數據傳輸相關方面的技術合作,可聯系我。聯系方式:neteasy163z@163.com

2014-03-01 18:47:47

基站接收器集成化的進展

2019-08-27 09:05:39

如何使用MLD優化MIMO接收器的性能?

2021-05-24 06:16:55

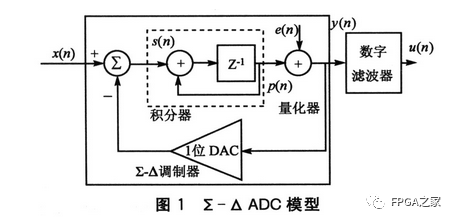

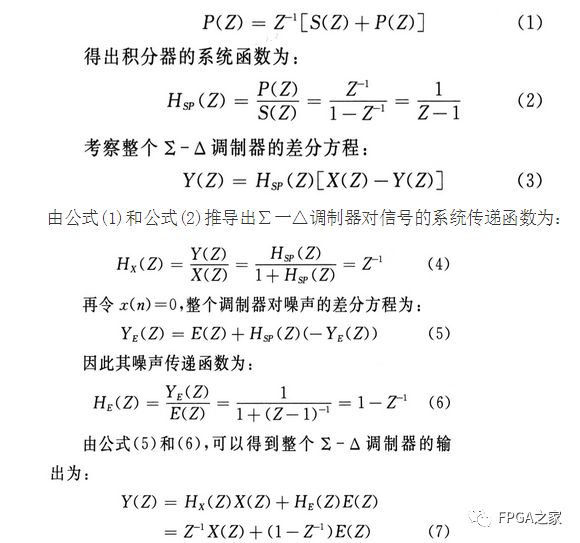

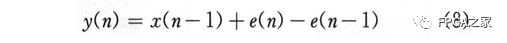

∑一△ADC原理是什么?LVDS收發器標準及其原理是什么?如何利用LVDS接收器去實現ADC?

2021-06-03 06:23:35

Spartan-3 FPGA系列如何僅通過在接收器數據通路中加入一個倒相器即可避免大量使用過孔?如何利用Spartan-3 FPGA進行LVDS信號倒相設計?

2021-05-06 07:30:25

在串行數據傳輸的過程中,如何在FPGA中利用低頻源同步時鐘實現LVDS接收字對齊呢?

2021-04-08 06:39:42

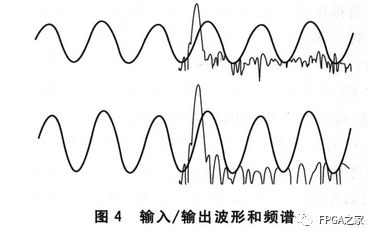

本文介紹如何確定接收器增益,以及接收器增益設置太高時對接收SNR的負面影響。文章也討論如何正確優化數字波束成形器、濾波器、檢波器的動態范圍以及壓縮信號映射。實現上述優化后,系統將最大程度地發揮高SNR接收器的優勢,大幅提高診斷性能。

2021-04-19 10:00:39

`` 隨著工業無線遙控器的廣泛使用,需普及更多的遙控器專業知識給大家,方便大家進行安全的生產和生產更順暢;今天主要給大家講解接收器天線及隔離器的安裝注意事項,因為在進行上門售后的過程中,技術工程師

2021-04-17 10:28:15

`求大神講解下他的構成,我要制作的話,需要什么?現在知道他是個無線接收器,接收距離3000`

2013-04-05 19:07:43

現在的無線充電器都是通過線圈來發送的,需要配合無線接收器才能完成充電過程。大部分充電接收器在充電過程中會出現過熱的情況,不知道大家怎么看?

2014-08-22 17:59:27

嗨,是否有Xilinx提供的視頻LVDS serdes發送器/接收器IP內核?如果是這樣請分享詳細信息。

2020-05-22 14:34:10

目前使用的的時xilinx kintex7 核心板,使用Bank14作為LVDS輸入和輸出,Bank14供電為2.5V,并聯100歐電阻,測量出來有輸出也有輸入,但是FPGA讀不到數據,為什么?

2023-09-14 10:19:21

本人想做一個直接接入到FPGA或者DSP等基帶處理系統的RF接收器,頻段是2.4Ghz的,希望能夠選擇一到兩個芯片完成從天線到LNA、下變頻、IQ調制的2.4Ghz RF接收器子板,然后通過ADC

2013-10-11 20:26:06

你好,我目前正在設計一個LVDS接收器和DAC ASIC。DAC是12位。我需要使用來自FPGA / Eval板的LVDS信號進行測試。任何人都可以推薦我可以用來測試我的ASIC的評估板或FPGA嗎?謝謝。問候,尼基爾

2019-09-19 12:27:09

DIY紅外遙控接收器

2012-08-15 22:36:16

您好: 我準備用FPGA來對接AD9122,FPGA發送LVDS數據,DAC接收。 如果FPGA是LVDS接收的話,FPGA可以使能內部的差分電阻,就是在P-N之間使能了一個100歐姆的電阻, 現在

2018-10-29 10:34:15

大家好。我已經模擬了1到10個與XAPP1017相關的DDR數據,我不清楚理解反序列化lvds數據的理論誰能給我一個關于如何用XAPP1017實現1到12 DDR數據接收器的例子

2020-08-06 10:44:54

你好,我目前正在設計一個LVDS接收器和DAC ASIC。DAC是12位。我需要使用來自FPGA / Eval板的LVDS信號進行測試。任何人都可以推薦Xilinx的評估板或FPGA,我可以使用它來測試我的ASIC嗎?謝謝。問候,尼基爾

2019-08-28 07:03:41

那位老師可以幫我做一款調頻調幅同步無線接收器。

2022-11-16 21:25:57

轉換接收器芯片LTM9004資料下載內容主要介紹了:LTM9004功能和特點LTM9004引腳功能LTM9004內部方框圖LTM9004典型應用電路

2021-03-30 06:01:33

時鐘信號,因為用戶為UART硬件提供了必要的時序信息。實際上,有一個時鐘信號,但是它不是從一個通信設備傳輸到另一個通信設備的;相反,接收器和發送器都具有內部時鐘信號,這些時鐘信號控制如何生成變化的邏輯

2020-09-18 09:00:00

時鐘信號,因為用戶為UART硬件提供了必要的時序信息。實際上,有一個時鐘信號,但是它不是從一個通信設備傳輸到另一個通信設備的;相反,接收器和發送器都具有內部時鐘信號,這些時鐘信號控制如何生成變化的邏輯

2020-09-25 17:43:01

畢業設計:功放機遙控接收器的設計,用到了PT2314這個芯片,不懂啊,求幫忙!

2013-05-28 20:16:03

MAX9111/MAX9113單路/雙路低壓差分信號(LVDS)接收器專為需要超小功耗、空間和噪聲的高速應用而設計。這兩款器件均支持超過500Mbps的開關速率,同時采用+3.3V單電源供電,并具有

2023-07-12 16:11:19

MAX9111/MAX9113單路/雙路低壓差分信號(LVDS)接收器專為需要超小功耗、空間和噪聲的高速應用而設計。這兩款器件均支持超過500Mbps的開關速率,同時采用+3.3V單電源供電,并具有

2023-07-12 16:16:25

驅動器/接收器,驅動器/接收器原理是什么?

5V雙RS232驅動器/接收器

T1780/LT1781雙RS驅動器

2010-03-08 13:27:01 1818

1818 光接收器,光接收器原理和結構組成是什么?

光接收器的定義:

在光纖通信系統中,光接收

2010-03-19 17:03:21 12852

12852 光接收器件,什么是光接收器件

光接收機用于接收光纜中的光信號,再將之轉換為電信號送入電纜網絡。

其

2010-04-02 16:02:49 4129

4129 本文描述TI 的客戶在不用 LVDS (低壓差分信號傳輸)驅動器時,如何采用LVDS 接收器于其他驅動器配合解決一些簡單的問題。

2011-07-18 15:21:36 30

30 介紹了LVDS技術的原理,對LVDS接口在高速數據傳輸系統中的應用做了簡要的分析,著重介紹了基于FPGA的LVDS_TX模塊的應用,并通過其在DAC系統中的應用實驗進一步說明了LVDS接口的優點。

2012-01-11 10:46:04 99

99 低電壓差分信號(LVDS)是一種高速點到點應用通信標準。多點LVDS (M-LVDS)則是一種面向多點應用的類似標準。LVDS和M-LVDS均使用差分信號,通過這種雙線式通信方法,接收器將根據兩個互補

2013-08-22 16:09:00 93

93 低功耗數據傳輸領域的主流技術。它具有信號擺幅小、速度快、功耗低、抗共模噪聲能力強、電磁干擾小等優點。 LVDS接口技術的原理可簡單概括為:由驅動器( driver)將CMOS或TTL信號轉換成LVDS差分信號,并經過互連線傳輸到接收器端,而接收器又將差分信

2017-11-01 15:50:08 11

11 的作用下由DVI發送器進行編碼并串行化后,通過TMDS通道發送給DVI接收器;DVI接收器對其進行串/并轉換、通道對齊、解碼等一系列處理后發送給顯示設備。

2017-11-22 14:27:02 4895

4895 電子發燒友網為你提供TI(ti)SN55LVDS32相關產品參數、數據手冊,更有SN55LVDS32的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SN55LVDS32真值表,SN55LVDS32管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-11-02 19:01:06

電子發燒友網為你提供TI(ti)SN65LVDS32相關產品參數、數據手冊,更有SN65LVDS32的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SN65LVDS32真值表,SN65LVDS32管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

電子發燒友網為你提供TI(ti)SN65LVDS2相關產品參數、數據手冊,更有SN65LVDS2的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SN65LVDS2真值表,SN65LVDS2管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

LVDS接收器可以承受至少±1V的驅動器與接收器之間的地的電壓變化。由于LVDS驅動器典型的偏置電壓為+1.2V,地的電壓變化、驅動器偏置電壓以及輕度耦合到的噪聲之和,在接收器的輸入端相對于接收器的地是共模電壓。

2018-11-01 16:47:28 74230

74230

在電纜應用中,接收器將不總是由發送器驅動,并且接收器輸入上可能存在超過20 mV的差分噪聲,應考慮使用額外的故障保護電阻。

2021-05-21 06:24:00 2846

2846 ADN4668:3 V LVDS四路CMOS差分線路接收器數據表

2021-05-08 17:13:41 1

1 ADN4664:雙路3 V CMOS LVDS差分線路接收器數據表

2021-05-09 17:49:57 2

2 ADN4662:單路、3 V、CMOS、LVDS差分線路接收器數據表

2021-05-25 19:48:08 5

5 ADV7782:帶LVDS、HDCP和MIPI支持的APIX2接收器數據表

2021-05-27 18:32:53 7

7 VP386 數據表 8/28 位 LVDS 視頻接收器

2023-04-27 19:34:18 0

0 紅外遙控接收器模塊,非常簡單,也是由GND,VCC和數據三個引腳組成,通過杜邦線可以直接連接在FPGA的IO口上,產品細節如下

2023-10-15 10:53:49 415

415

簡介:本文將介紹基于FPGA的無線充電器接收器系統的解決方案。無線充電器接收器嚴格遵循最新的WPC Qi標準。接收器系統包含一個模擬模塊和一個FPGA模塊。模擬模塊由分立式組件組成,包括全橋整流器

2023-11-09 15:26:30 5

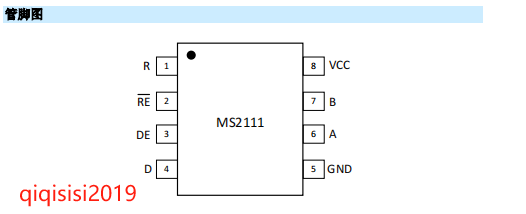

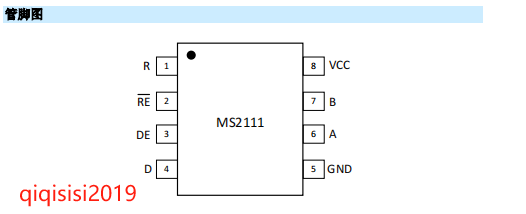

5 產品簡述 MS2111 是多點低壓差分(M-LVDS)線路驅動器和接收器。經過 優化,可運行在高達 200Mbps 的信號速率下。所有部件均符合 M LVDS 標準 TIA / EIA-899

2024-01-25 11:20:58 263

263

電子發燒友App

電子發燒友App

評論