今天給大俠帶來Xilinx ZYNQ 動手實操演練,話不多說,上貨。當我們一提到?Xilinx ZYNQ,大家腦海大多數就會浮現一個描述的詞匯,高端,其實這個詞很貼切的形容了Zynq系列產品,Xilinx (賽靈思公司)推出的行業第一個可擴展處理平臺Zynq系列,旨在為視頻監視、汽車駕駛員輔助以及工廠自動化等高端嵌入式應用提供所需的處理與計算性能水平。 ? ? ?

名稱的由來

Zynq這個詞很容易讓人聯想到zinc,也就是電池、日光屏、合金制品和藥品中最常見的化學元素鋅。鋅與其他金屬的合金可實現增強型功能,根據合金的不同對象表現為不同的色彩。鋅最常見的用途就是電鍍。那么這個名稱與電鍍之間有什么聯系?

在2010年4月硅谷舉行的嵌入式系統大會上,賽靈思發布了可擴展處理平臺的架構詳情,這款基于無處不在的ARM處理器的SoC可滿足復雜嵌入式系統的高性能、低功耗和多核處理能力要求。賽靈思可擴展處理平臺芯片硬件的核心本質就是將通用基礎雙ARMCortex-A9MPCore處理器系統作為“主系統”,結合低功耗28nm工藝技術,以實現高度的靈活性、強大的配置功能和高性能。由于該新型器件的可編程邏輯部分基于賽靈思28nm7系列FPGA,因此該系列產品的名稱中添加了“7000”,以保持與7系列FPGA的一致性,同時也方便日后本系列新產品的命名。

除了芯片外,賽靈思Zynq-7000系列還構成了最終平臺產品的基礎。賽靈思聯盟計劃生態系統和ARM互聯社區的成員提供的軟件開發與硬件設計實現工具、廣泛采用的操作系統、調試器、IP及其他元素的工具就好像“電鍍”在一起一樣,從而使可擴展處理平臺成為了可能。

Zynq-7000為何不是FPGA?

Zynq-7000可擴展處理平臺是采用賽靈思新一代FPGA(Artix-7與Kintex-7FPGA)所采用的同一28nm可編程技術的最新產品系列。可編程邏輯可由用戶配置,并通過“互連”模塊連接在一起,這樣可以提供用戶自定義的任意邏輯功能,從而擴展處理系統的性能及功能。不過,與采用嵌入式處理器的FPGA不同,Zynq-7000產品系列的處理系統不僅能在開機時啟動,而且還可根據需要配置可編程邏輯。采用這種方法,軟件編程模式與全功能的標準ARM處理SoC毫無二致。

“可擴展”意味著什么?

在軟件工程領域,可擴展性(有時會同前向兼容性相混淆)是指實現方案考慮到未來發展需求的系統設計原理。這是一種能夠擴展系統的系統性舉措,也是實現擴展所需的工作。擴展可體現為增加新功能,也可體現為現有功能的修改。其核心主題就是在盡可能減少現有系統功能變動的基礎上實現變革。

在系統架構中,可擴展性意味著系統設計時包含了通過新功能擴展/改進自身的機制和元素(hook),而且無需對系統基礎架構進行較大的修改。良好的架構反映了實現上述目的的設計原理,也為今后可能的構建工作制定了發展藍圖。請注意,這通常是指最終交付的產品中包含了尚不會(實際上可能永遠不會)用到的功能和機制,但這種功能并不是可有可無的,而是可維護性的必要元素,有助于避免產品過早被淘汰。

ZYNQ=processor

Zynq-7000嵌入式處理平臺系列的每款產品均采用帶有NEON及雙精度浮點引擎的雙核ARMCortex-A9MPCore處理系統,該系統通過硬連線完成了包括L1,L2緩存、存儲器控制器以及常用外設在內的全面集成。該處理系統不僅能在開機時啟動并運行各種獨立于可編程邏輯的操作系統(OS),而且還可根據需要配置可編程邏輯。利用這種方法,軟件編程模式與全功能的標準ARM處理SoC毫無二致。

應用開發人員利用可編程邏輯強大的并行處理能力,不僅可以解決多種不同信號處理應用中的大量數據處理問題,而且還能通過實施更多外設來擴展處理系統的特性。系統和可編程邏輯之間的高帶寬AMBA-AXI互聯能以極低的功耗支持千兆位級數據傳輸,從而解決了控制、數據、I/O和存儲器之間的常見性能瓶頸問題。

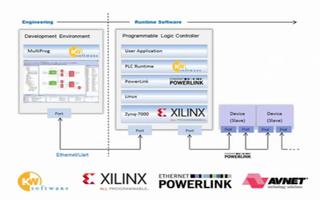

編程環境

Zynq-7000系列提供了一個開放式設計環境,便于可編程邏輯中雙核Cortex-A9MPCore和定制加速器的并行開發,從而加速了產品上市進程。軟件開發人員可以充分利用基于Eclipse的XilinxPlatformStudio軟件開發套件(SDK)、ARM的DS-5和ARMRealViewDesignSuite(RVDS),或ARM互聯社區和賽靈思聯盟計劃生態系統的領先廠商(諸如Lauterbach、WindRiver、PetaLogix、MathWorks、MentorGraphics、Micrium和MontaVista等)提供的編譯器、調試器和應用。

此外,利用賽靈思屢獲殊榮的ISE設計套件的優勢,Zynq-7000系列的可編程結構經定制可以最大化系統級性能,滿足特定應用的各種需求。該套件提供了包括開發工具、AMB4AXI4即插即用IP核和總線功能模型(BFM)等在內的完整硬件開發環境,有助于加速設計和驗證工作。賽靈思通過收購高級綜合技術領先公司AutoESL進一步提升了在工具方面的進程,提供C,C++以及系統C綜合優化Zynq-7000器件架構。未來的版本也將促進Zynq-7000產品系列中處理器和可編程邏輯之間關鍵算法的無縫銜接。

隨著時間的推移,ARM互聯社區和賽靈思聯盟計劃生態系統的第三方廠商將進一步擴展上述解決方案,這是賽靈思目標設計平臺的一部分,可提供包括IP核、參考設計、開發套件及其他資源等在內的高效統一的開發環境,從而滿足特定應用和設計領域要求。

可編程邏輯架構

Zynq-7000系列的可編程邏輯完全基于賽靈思最新7系列FPGA架構來設計,可確保28nm系列器件的IP核、工具和性能100%兼容。最小型的Zynq-7000、Zynq-7010和Zynq-7020均基于專門針對低成本和低功耗優化的Artix-7系列;較大型的Zynq-7030和Zynq-7040器件基于包括4至12個10.3Gbps收發器通道,可支持高速片外連接的中端Kintex-7系列。所有四款產品均采用基于2個12位1MspsADC(模數轉換器)模塊的新型模擬混合信號模塊。

Zynq的一些概念

ZYNQ,總的來說,就是兩大功能塊,PS 部分和 PL部分, 直面意思理解就是ARM的SOC部分,和FPGA部分。

PS:?處理系統 (Processing System) , ?就是與FPGA無關的ARM的SOC的部分。

PL:?可編程邏輯 (Progarmmable Logic), 就是FPGA部分。之所以叫PL,而不是叫FPGA,原因主要是考慮到讓做軟件的大俠們不要望而生畏。對于邏輯而言,在這里就不多說了,單純做軟件的也不要去考慮了。

下一個層級, APU部分:

APU:?應用處理器單元(Application Processor Unit), 位于PS里面的中心位置。APU這三個字,AMD公司曾經用過,特指全稱是“Accelerated Processing Units”,加速處理器,它是融聚了CPU與GPU功能的產品,電腦上兩個最重要的處理器融合,相互補足,發揮最大性能。XILINX 的APU與AMD的APU在縮寫上就是截然不同的兩個詞, 不要混淆了。

APU 這個詞,在Xilinx內部的術語中,也是存在撞車的。在Xilinx 的 PowerPC體系中,?有一個輔助處理單元“Auxiliary Processing Unit” 的概念,指的是在PowerPC硬核外掛的浮點協處理器之類的單元。

在這個位置上的處理器, 還有各種其他的叫法, 有MCU (微控制器處理單元Microcontroller Unit),MPU (微處理器單元Microprocessor Unit),等等。? MCU這個叫法,暗示了處理器功能不強,只能搞搞輸入輸出控制啊,寫個小狀態機啊, 一般都是8位機。? MPU呢,就更先進了一些,成prcessor了,這意味著處理器通常是32位的, 能干點計算的事。但是有一個micro詞根在里面,說明干的是小活,通常沒有正式的和全尺寸的操作系統, 通常沒有內存管理單元MMU。? ARM 的Cortex-M系列是干這類活的。

APU,帶了Application這個詞, 意味著在上面可以跑應用程序, 暗示著這個系統是需要全尺寸的操作系統的,和現在炙手可熱的應用商店app store 遙相呼應。?

APU里面具體包含的內容嘛,就是雙ARM-CortexA9核,加上高速緩沖,DMA,定時器,中斷控制,浮點和NEON協處理,硬件加速器一致性控制器ACP神馬的。也就是處理器核心部分。

套用時下越來越流行的詞匯,“嵌入式計算”, "embedded computing", 可以這么說,用MCU,MPU搭出來的東東,通常叫嵌入式系統。而APU搭出來的東東, 就夠格叫嵌入式計算系統了。

TTC, 這個詞,當年猜了半天也拿不準,看了文檔,發現,是Triple Time Counter的意思。就是這個計數器里面有3個獨立通道,可以獨立計數。掛在APB上,為系統或外設提供定時或計數服務的。

WDT, ?看門狗定時器,有兩個,分別監視ARM-Cortex A9用的。如果軟件跑飛,無法清定時器,一段時間后,看門狗就復位。

SWDT,系統級看門狗定時器, 這個看門狗的時鐘和復位信號,都可以來自于芯片外部, 這樣,即使系統有嚴重故障,比如時鐘頻率本身都有問題了,仍然可以通過與系統無關的外部信號計數,計數滿就復位。?

SCU, Snoop Control Unit, ?用來保持雙核之間的數據Cache的一致性。也就是是說,第一個A9處理器寫存儲時,只是寫在了緩存里,沒有進主存,如果第二個A9讀操作,涉及到第一個寫臟了的數據段, SCU要保證第二個A9的緩存里是最新的數據。? 如果第二個A9寫同樣數據段的數據,需要在第一個中體現出寫的內容。

SCU的存在,才使得兩個核成互相聯系的“雙核”,才能成為MPsoc。在原先Xilinx的雙PowerPC的芯片中, 是不存在的。不少學校的老師拿Xilinx的雙powerpc練手和教學,從頭搭一個Snoop協議在裸的雙PowerPC中,倒也不錯。

開發環境

Zynq的開發環境,可以在ISE或者Vivado,不過ISE在14.7之后就停止了更新,建議安裝VIVADO,畢竟Vivado號稱是把各種開發工具集成并且支持圖形化建模的功能強大的開發軟件。

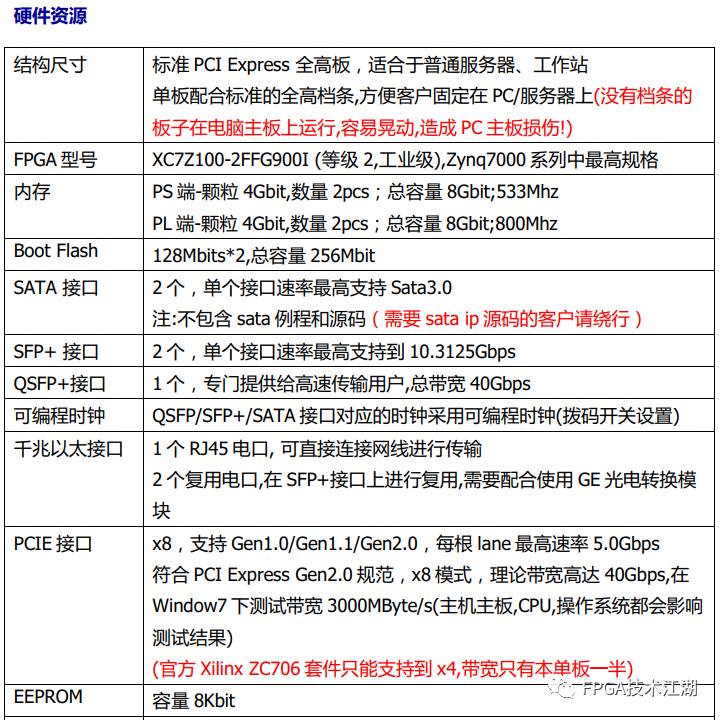

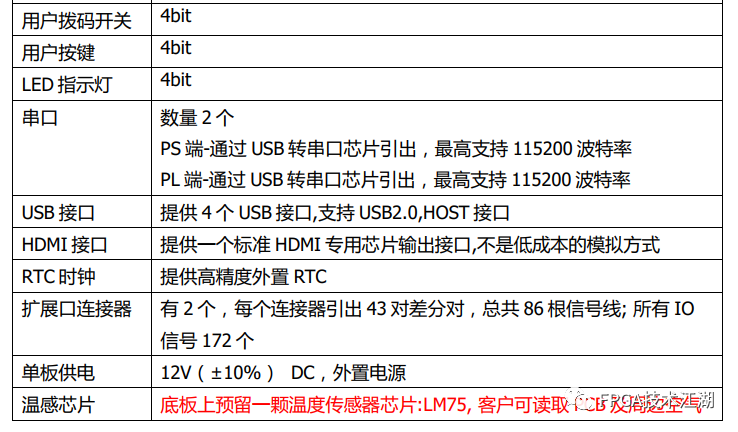

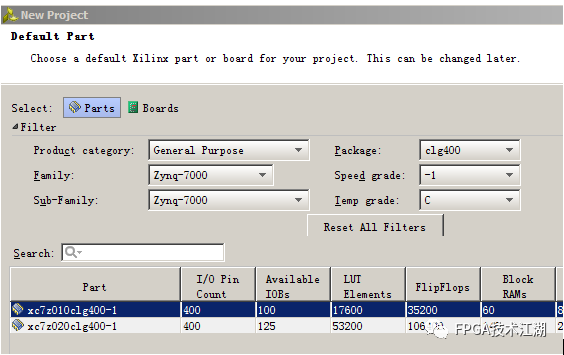

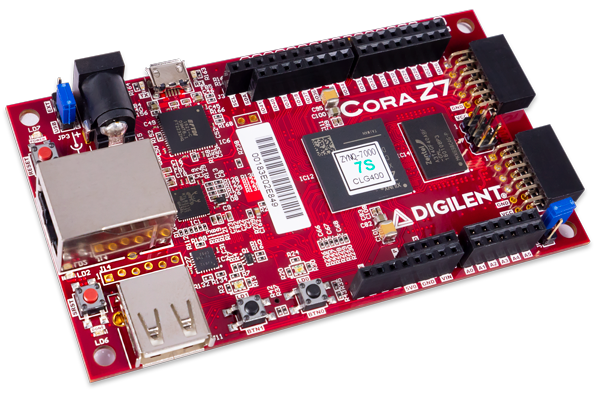

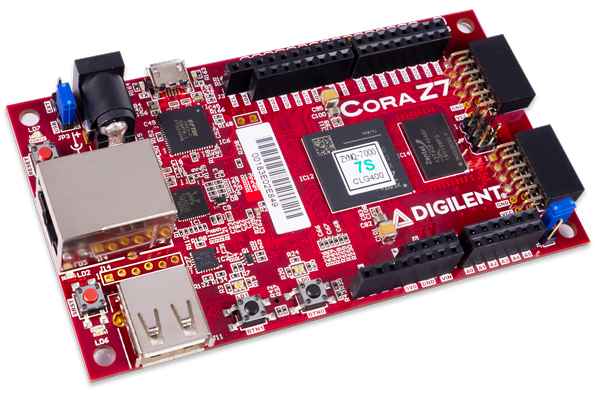

Vivado的安裝教程公眾號前篇推送過,各位大俠如有需要可以翻一下,這里放個超鏈接,Xilinx Vivado 2017.2安裝教程,說了這么多,下面介紹一下開發硬件環境Zynq 7000 XC7Z100,Zynq 7000系列中頂配型號,Zynq + Kintex7最強組合,提供豐富的芯片內部資源。

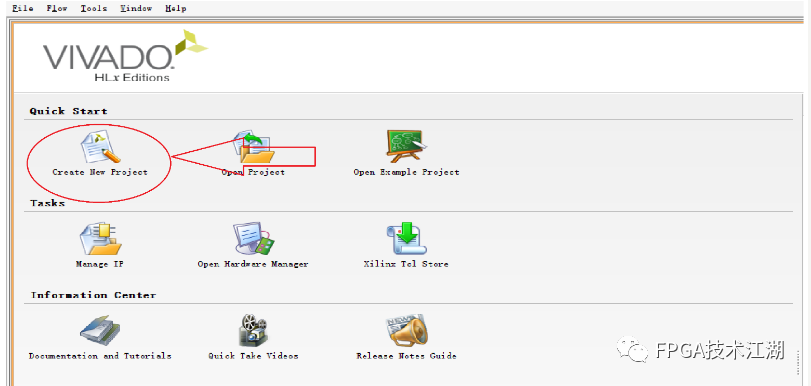

首先打開安裝的Vivado 2017.2,打開界面如下:

實操演示

下面做一個從uart打印hello world的實驗,只用PS,不用PL部分,程序從SD卡啟動,跑在PS的內部RAM。

zynq 7000的PS雖然也是CPU,但是開發方法不像普通的CPU只需要一個SDK就可以了,它還需要vivado硬件設計軟件。

ZYNQ 7000的PS開發需要兩個工具,一個是vivado,?另一個是SDK。

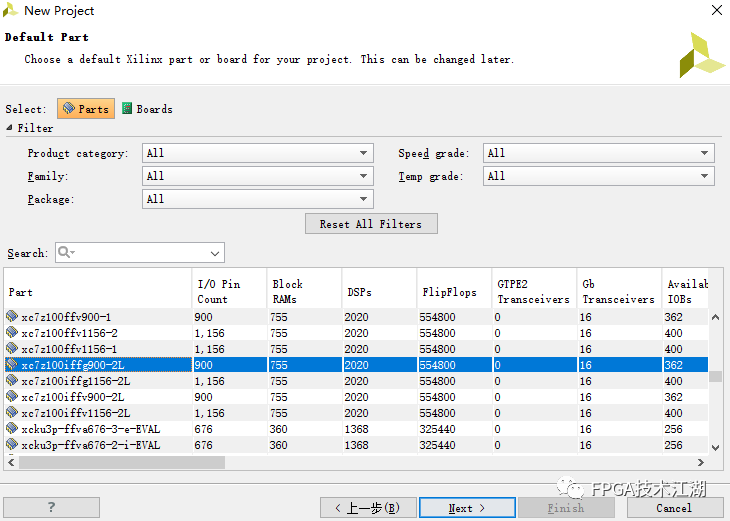

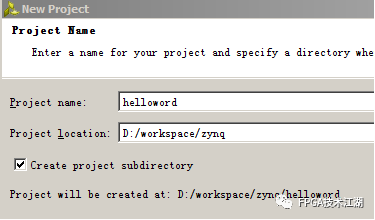

1. 打開vivado軟件-->Create New Project,工程名和目錄:

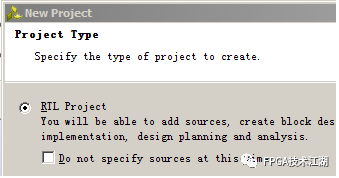

2. next->選RTL Project->Add Sources,Add existing IP和Add constraints界面直接點next。

? 3. New Parts界面。

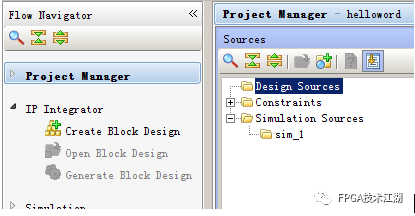

4. 添加IP,在Flow Navigator的IP Integrator 下點擊Create Block Design。

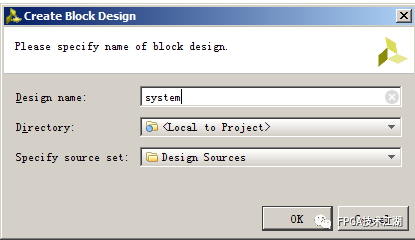

下一步,Create Block Design如下,點OK。

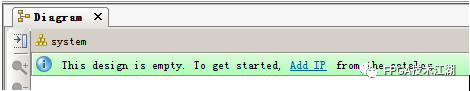

下一步,在Diagram界面點擊Add IP。

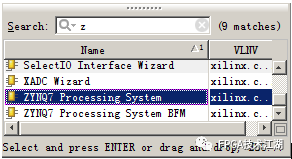

? 下一步,雙擊ZYNQ7 Processing System,添加CPU。

? 5. 設置CPU。 在Diagram界面點擊Run Block Automation,不做修改,點Finish就可以。在Diagram界面雙擊。

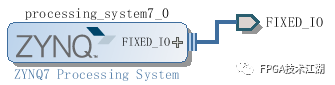

進入設置界面,我們把所有的接口去掉,只留下FIXED_IO。

<1> PS-PL Configuration->General->Enable Clock Resets->去掉FCLK_RESET0_N

<2> PS-PL Configuration->GP Master AXI Interface->去掉 M AXI GP0 interface

<3> Clock Configuration->PL Fabric Clocks->去掉FCLK_CLK0

<4> DDR Congiguration->去掉Enable DDR

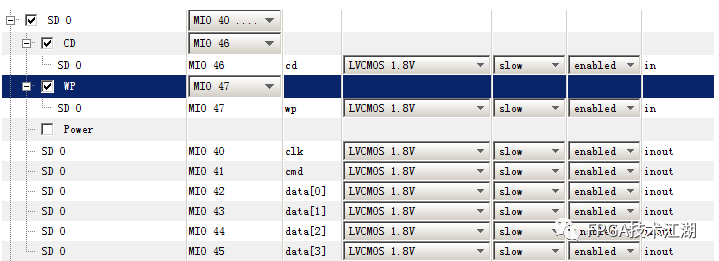

<5> 設置SD和UART引腳

MIO Configuration->Bank1 IO Voltage選LVCMOS 1.8V

MIO Configuration->IO Peripherals->選上SD 0, SD 0的引腳配置:

6. 點擊OK返回Diagram界面, 把DDR接口刪掉,配置之后的界面。

7. 生成設計文件

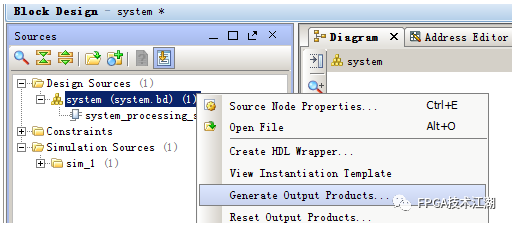

右擊system項->Generate Output Products->直接點Generate, 之后會提示文件生成成功。

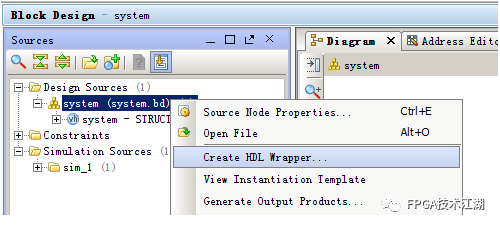

? 下一步,右擊system項->Create HDL Wrapper。

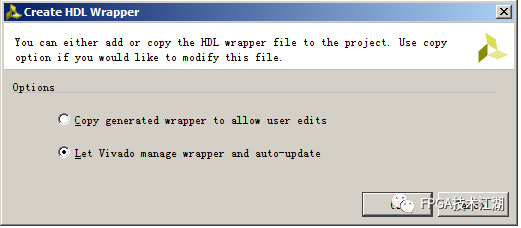

? 下一步,選下面一項,點OK。

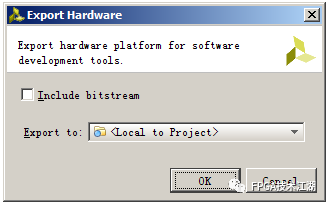

注意:如果重新修改了CPU配置,上面兩個步驟一定要重新實行。 ? 8. 導出硬件設計文件到SDK 導出前要確保Block Design是打開的,即Diagram界面要打開File->Export->Export Hardware->直接點OK,這樣會把硬件文件system_wrapper.hdf導到helloword.sdk文件夾下,SDK工程也在該目錄下。

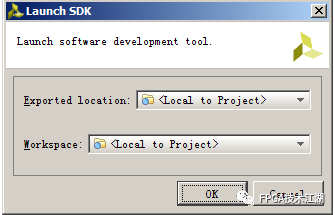

? 9. 啟動SDK File->Launch SDK->直接點OK。

? 下一步,SDK啟動后就自動添加了硬件相關的工程。

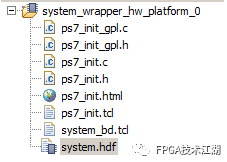

? system.hdf是system_wrapper.hdf文件的copy; ps7_init.tcl是PS初始化的TCL腳本,PS不能執行TCL腳本,所以將該腳本轉換為了C文件--ps7_init.c和ps7_init.h.;? ? 前面用vivado的硬件設計就是為了生成這兩個文件,ps7_init.c主要初始化CPU的時鐘,引腳復用,ddr和外設等。后面的helloword工程只需要這兩個文件,其他的文件都不需要。? ? ? ??

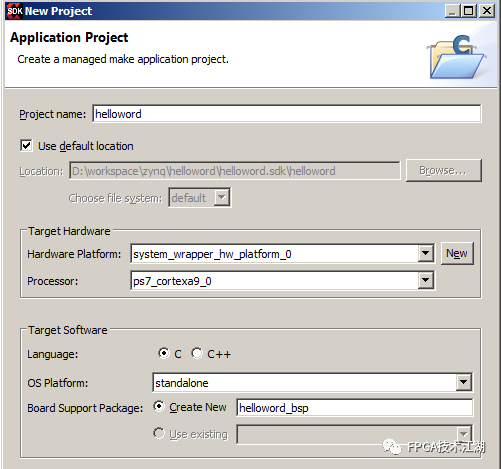

? ?? 10.添加helloword工程? 在SDK中->File->New->New Application Project->設置如下,點next->選hello world。

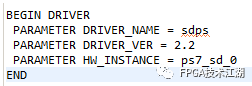

? 11. 修改源碼 多了兩個工程,一個是app,另一個是bsp. ,發現SD V2.3驅動有問題,將其退為2.2。 在helloword_bsp工程下打開system.mss文件,點擊左下角的source,修改sd驅動版本為2.2。

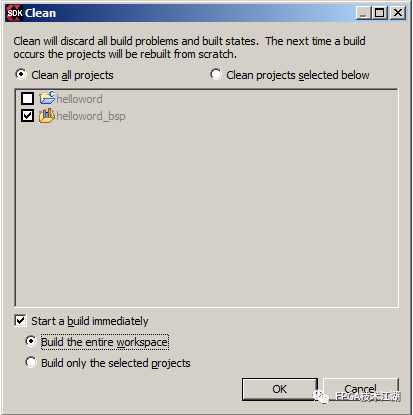

? 修改之后重新生成BSP源碼,點system.mss左下角的overview->Re-generate BSP Sources。?? 將ps7_init.c和ps7_init.h copy到helloword/src目錄下,也可以創建連接,這里就直接copy了。? ? 修改helloword/src/platform.c --init_platform函數,將ps7_init()函數的comment去掉,?? ? ? ? ?? --包含頭文件#include "ps7_init.h" ? 12. 編譯代碼->project->Clean->OK

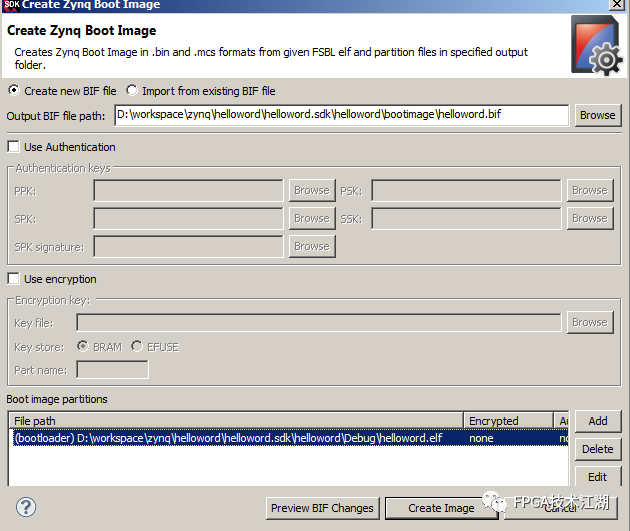

? 13. 生成boot.bin啟動文件

右擊helloword工程->Create boot Image->Create Image。

? 注意:helloword.elf 前面的bootloader一定要出現,表示該文件是bootloader,啟動后運行的第一個文件,可點edit來修改。

? ?? 14.? 將生成的BOOT.bin文件copy到SD卡(已用HP USB Disk Storage Format Tool格式化成啟動盤),啟動,從串口可看到打印信息。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論