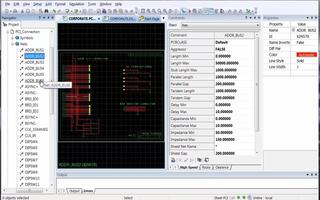

對話框的約束部分下,選擇默認約束設置作為活動約束設置;包含在Xilinx設計約束(XDC)文件中捕獲的設計約束的一組文件,可以將其應用于設計中。兩種類型的設計約束是: 1) 物理約束:這些約束定義引腳

2020-11-23 14:16:36 4342

4342

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2022-07-25 10:13:44 4280

4280 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1457

1457 在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 7060

7060

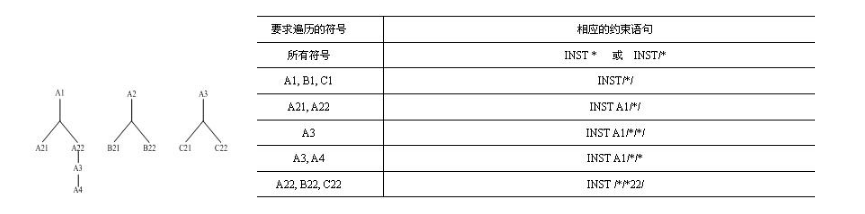

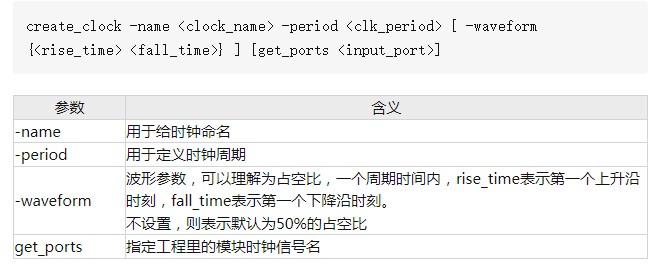

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1441

1441 前面幾篇FPGA時序約束進階篇,介紹了常用主時鐘約束、衍生時鐘約束、時鐘分組約束的設置,接下來介紹一下常用的另外兩個時序約束語法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 995

995 在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。

2023-06-26 14:47:16 1005

1005

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 923

923

,FPGA上的全局時鐘管腳用完了就出現不夠用的情況。FPGA全局時鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

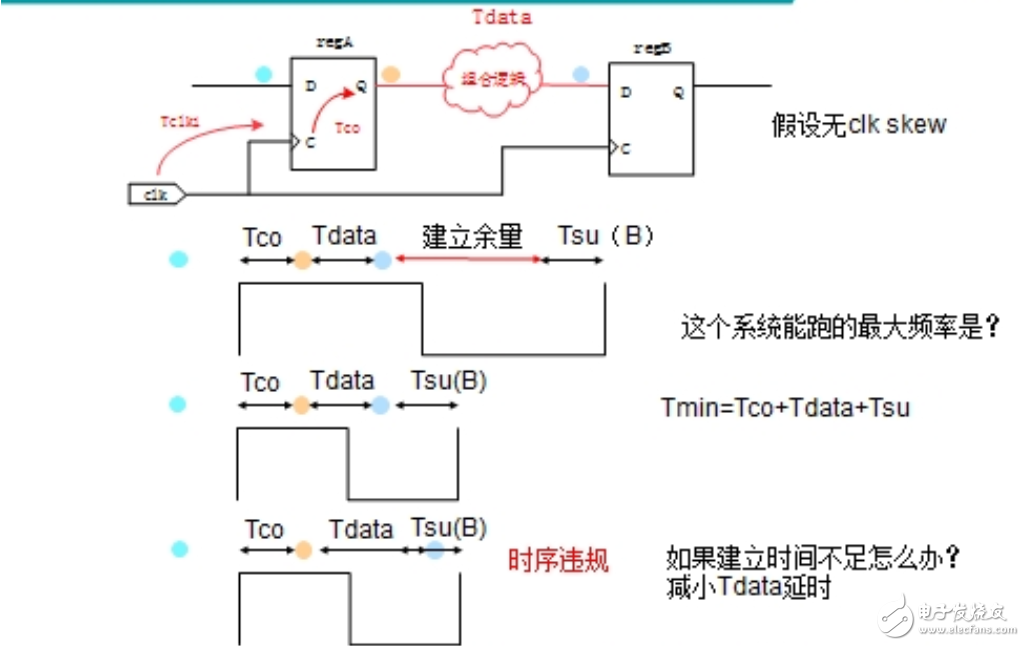

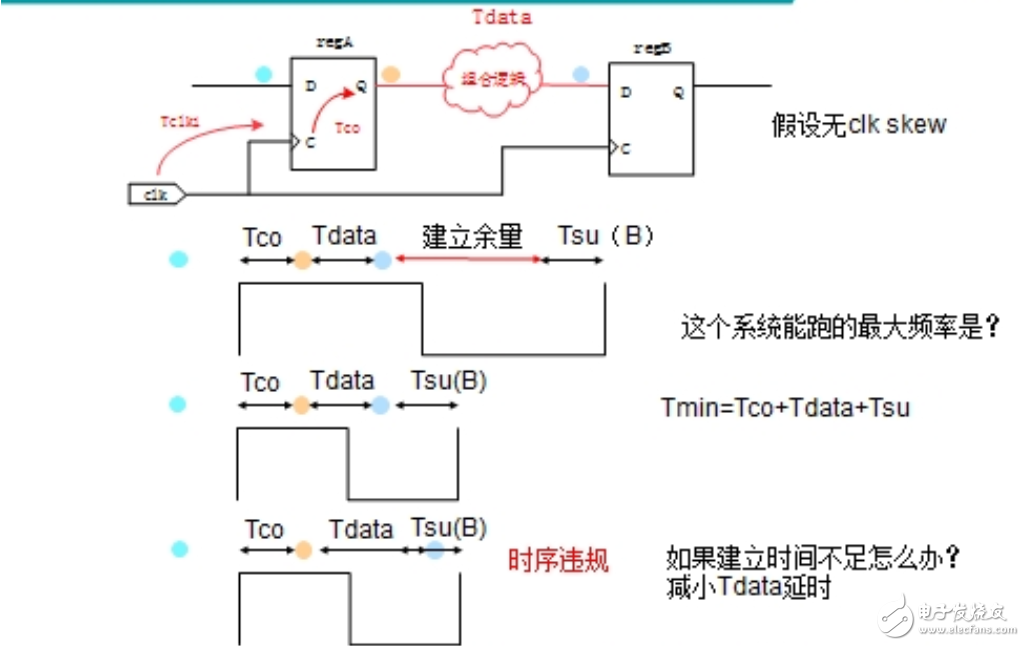

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

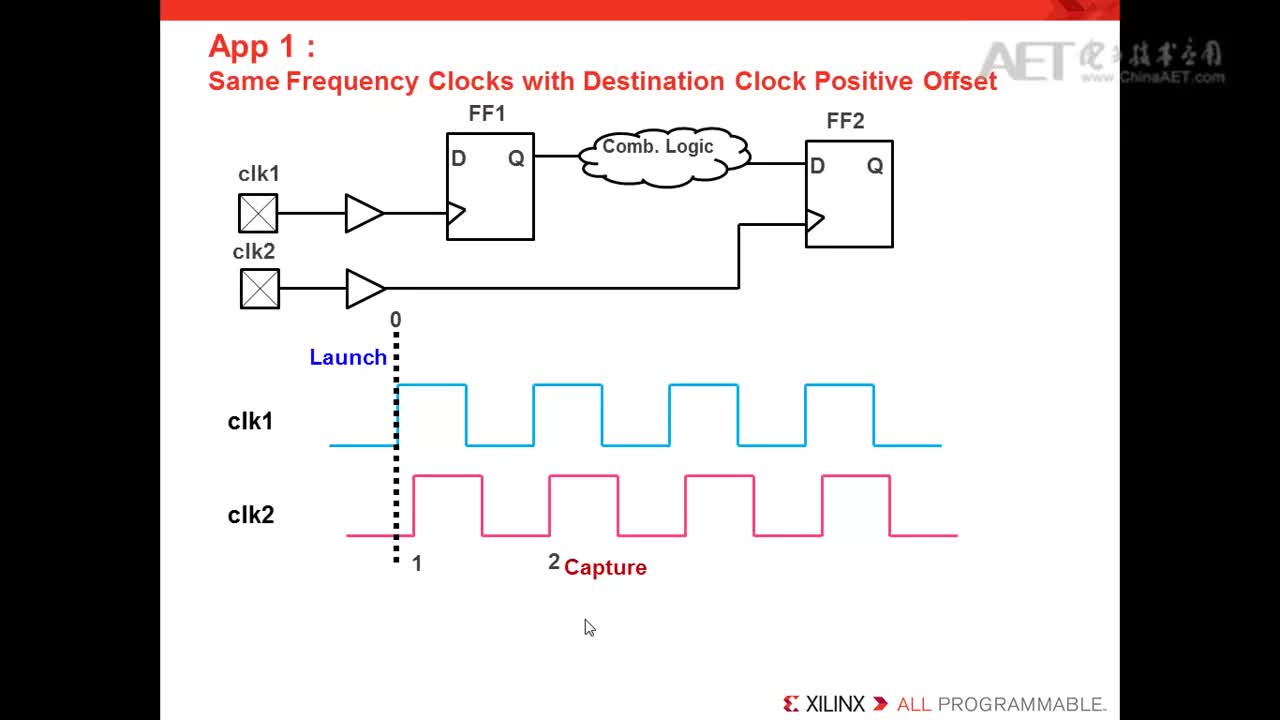

FPGA時序約束,總體來分可以分為3類,輸入時序約束,輸出時序約束,和寄存器到寄存器路徑的約束。其中輸入時序約束主要指的是從FPGA引腳輸入的時鐘和輸入的數據直接的約束。共分為兩大類:1、源同步系統

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束

2016-06-02 15:54:04

不是最完整的時序約束。如果僅有這些約束的話,說明設計者的思路還局限在FPGA芯片內部。 2. 核心頻率約束+時序例外約束+I/O約束 I/O約束包括引腳分配位置、空閑引腳驅動方式、外部走線延時

2017-12-27 09:15:17

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

FPGA的DCM模塊,40MHz時鐘輸入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。對40MHz時鐘添加了約束,系統不是會自動對三個輸出時鐘進行約束

2017-05-25 15:06:47

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

本帖最后由 china198 于 2013-8-30 12:28 編輯

XILINX的作品---時序約束,寫的非常棒

2013-08-30 12:26:47

各位大神,請問Xilinx FPGA中的DCI是如何使用的?我知道是把每個Bank的VRP、VRN管腳分別下拉、上拉,除此之外,在HDL代碼和約束中應該如何寫呢?查了半天資料沒有查到,所以來論壇問問。@LQVSHQ

2017-08-20 20:51:57

大家好!想請教一下,Xilinx FPGA可以設置引腳帶內部上拉電阻嗎? 怎么設置?

2013-10-11 20:59:26

本帖最后由 eehome 于 2013-1-5 09:52 編輯

不可多得的Xilinx FPGA中文培訓材料教程,涉及到virtel的基本架構、賽靈思設計流程、如何閱讀報告、時序約束等經典

2012-03-02 09:51:53

用notepad++的關聯設置Lesson07 特權Xilinx FPGA SF-SP6入門指南 -- ISE與Modelsim聯合仿真之庫編譯Lesson08 特權Xilinx FPGA SF-SP6入門

2015-07-22 11:49:20

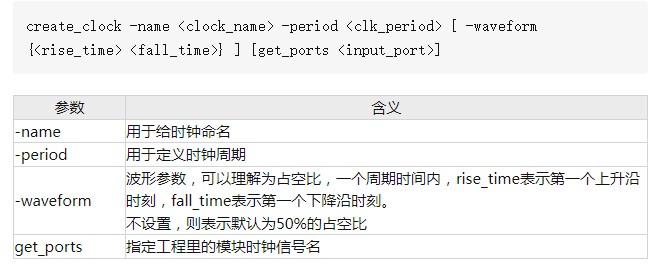

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

2024-04-12 17:39:04

(TX_CLK_o)。我想使用下面的約束命令來設置時鐘轉發,但我在合成時發現了警告。警告是什么意思?// constraints命令create_generated_clock -name TX_CLK_o

2020-05-04 08:04:41

在給 FPGA 做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在 FPGA 中都包含有4 種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入 到輸出的純組合邏輯

2012-03-05 15:02:22

Xilinx_fpga_設計:全局時序約束及試驗總結

2012-08-05 21:17:05

完成頂層模塊的實現并且仿真正確后,還需要編寫用戶約束文件,其中引腳約束文件是必不可少的,它將模塊的端口和 FPGA 的管腳對應起來。具體步驟如下。(1)創建約束文件。新建一個源文件,在代碼類型中選

2018-09-29 09:18:05

` 本帖最后由 eehome 于 2013-1-5 10:07 編輯

Xilinx FPGA開發實用教程第1章 FPGA開發簡介1.1 可編程邏輯器件基礎1.1.1 可編程邏輯器件概述1.1.2

2012-04-24 09:23:33

大家好, 誰能告訴我如何在RTL或xilinx spartan fpga的約束文件中插入1.56ns延遲緩沖區?這是為了避免xilinx工具在進行合成后報告的保持時間違規。問候馬赫什以上來自于谷歌

2019-06-18 07:18:04

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產品介紹使用Xilinx的FPGA、SoC和ACAP進行設計和開發

2021-01-22 06:38:47

1.工藝節點 首先不管選擇什么廠家的產品,都建議在其主流產品中選擇合適的芯片。 以上是目前 Xilinx 主流的也是常用的幾個 FPGA 產品系列,這里不談傳說中的后兩個系列

2020-12-23 17:21:03

大家好,我正在使用XC6SLX25-3CSG324IFPGA和版本13.4 Xilinx工具。根據數據表,這個FPGA能夠在100C的結溫下運行,我想確保在該溫度下關閉時序。我已經成立了溫度

2019-07-08 07:23:05

大家好我正在使用Virtex5 FPGA,我在設計中添加了一個OFFSET IN約束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

FPGACPLD設計工具——Xilinx ISE使用詳解的主要內容:第1章 ISE系統簡介第2章 工程管理器與設計輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 197

197 十分鐘學會Xilinx FPGA 設計

Xilinx FPGA設計基礎系統地介紹了Xilinx公司FPGA的結構特點和相關開發軟件的使用方法,詳細描述了VHDL語言的語法和設計方法,并深入討

2010-03-15 15:09:08 177

177 本書系統地論述了Xilinx FPGA開發方法、開發工具、實際案例及開發技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發基礎與進階、Xilinx FPGA電路原理與系統設計

2012-07-31 16:20:42 11371

11371

本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 Xilinx FPGA設計進階(提高篇)

有需要的下來看看

2015-12-29 15:45:48 12

12 輕松高效地設置 PCB 設計約束的八個步驟

2016-01-06 14:49:57 0

0 Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發環境的配置

2016-01-18 15:30:20 34

34 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發環境

2016-01-18 15:30:32 45

45 Xilinx時序約束設計,有需要的下來看看

2016-05-10 11:24:33 18

18 賽靈思FPGA設計時序約束指南,下來看看

2016-05-11 11:30:19 48

48 輕松高效地設置 PCB 設計約束的八個步驟

2022-05-11 16:44:57 0

0 FPGA學習資料教程之Xilinx時序約束培訓教材

2016-09-01 15:27:27 0

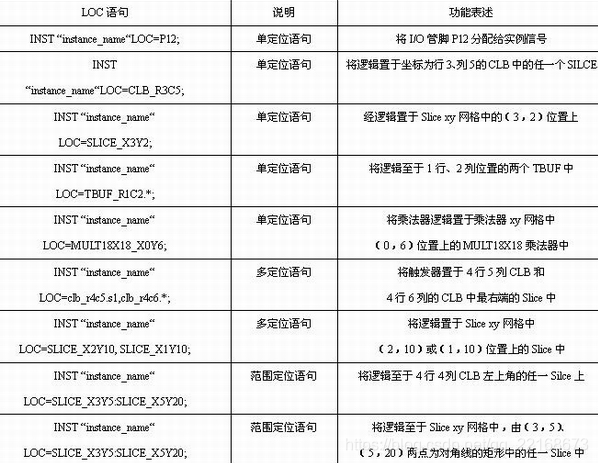

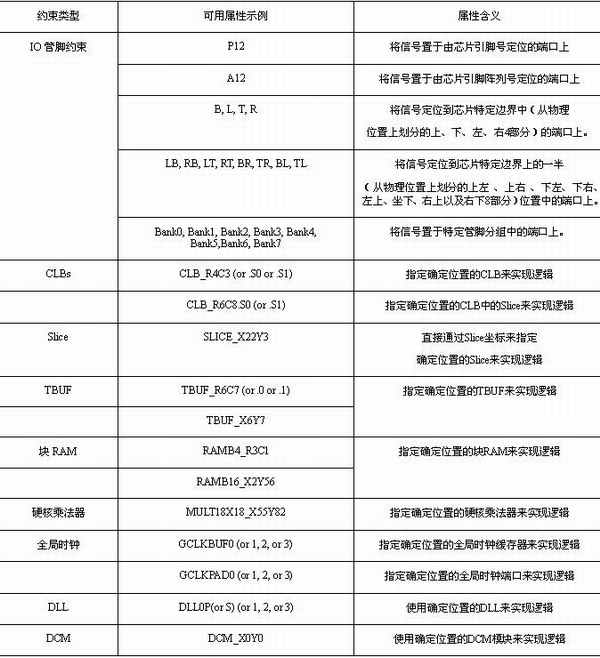

0 引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 10372

10372 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 4175

4175

FPGA設計中的約束文件有3類:用戶設計文件(.UCF文件)、網表約束文件(.NCF文件)以及物理約束文件(.PCF文件),可以完成時序約束、管腳約束以及區域約束。

2017-02-11 06:33:11 1459

1459 xilinx 約束實現

2017-03-01 13:12:47 15

15 文檔內容包含基于Xilinx FPGA的開發板代碼及原路圖,供網友參考。

2017-09-01 11:09:24 20

20 FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim參考設計

2017-10-31 09:59:24 23

23 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2357

2357

針對八通道采樣器AD9252的高速串行數據接口的特點,提出了一種基于FPGA時序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數據,利用FPGA內部的時鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 6558

6558

XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應用特性決定了其在接口上有多種構建和實現方式,所以從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要

2017-11-17 19:01:00 6761

6761

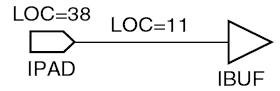

本文主要通過一個實例具體介紹ISE中通過編輯UCF文件來對FPGA設計進行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-24 19:59:29 2727

2727

摘要:本文主要通過一個實例具體介紹ISE中通過編輯UCF文件來對FPGA設計進行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-25 01:27:02 4786

4786

詳細講解了xilinx的時序約束實現方法和意義。包括:初級時鐘,衍生時鐘,異步時終域,多時終周期的講解

2018-01-25 09:53:12 6

6 介紹FPGA約束原理,理解約束的目的為設計服務,是為了保證設計滿足時序要求,指導FPGA工具進行綜合和實現,約束是Vivado等工具努力實現的目標。所以首先要設計合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 6432

6432 FPGA本身是有專門的時鐘cell的,以xilinx FPGA為例,就是primitive庫中的BUFG。

2018-12-22 15:33:59 1613

1613 了解如何將Altera的SDC約束轉換為Xilinx XDC約束,以及需要更改或修改哪些約束以使Altera的約束適用于Vivado設計軟件。

2018-11-27 07:17:00 4664

4664 Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 3376

3376 只需要簡單地用鼠標點擊幾下,就可定義、編輯和查看 PADS 原理圖環境中的網絡約束。為高速、布線和間距設置網絡和網絡類約束,為差分對設置特殊約束,或定義匹配長度組。高級工具提示會顯示如何操作。

2019-05-17 06:14:00 2642

2642

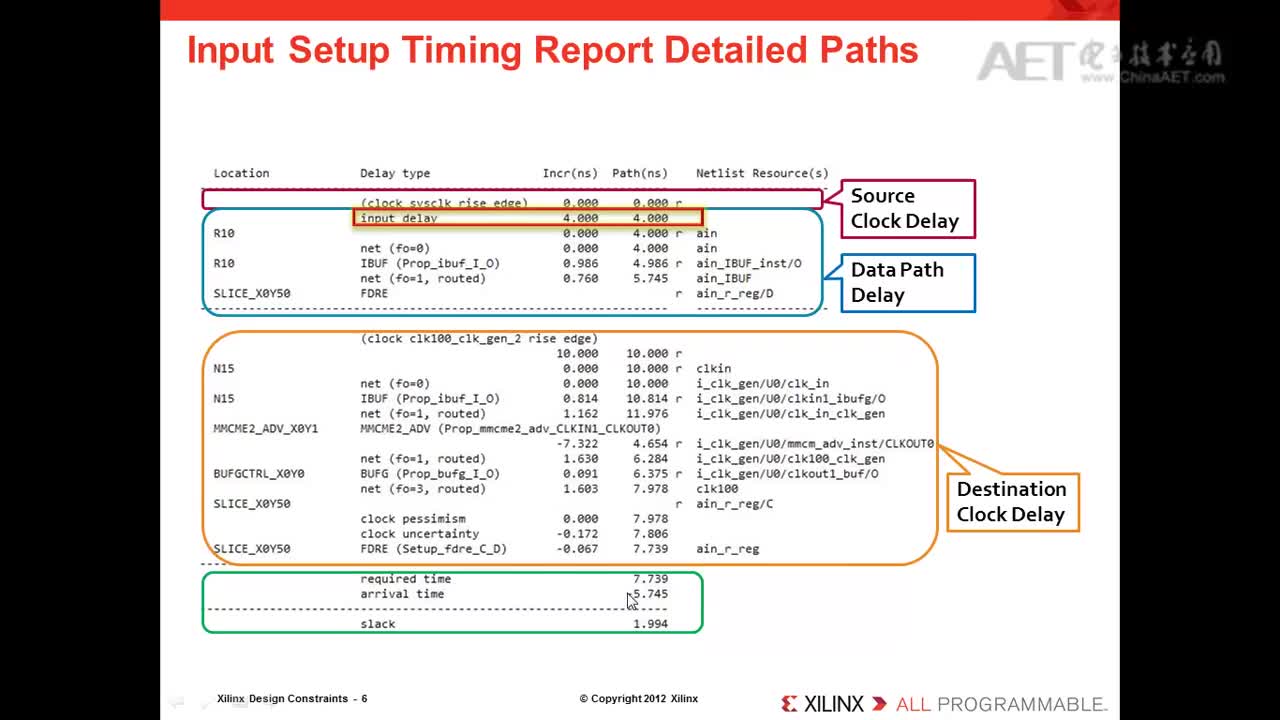

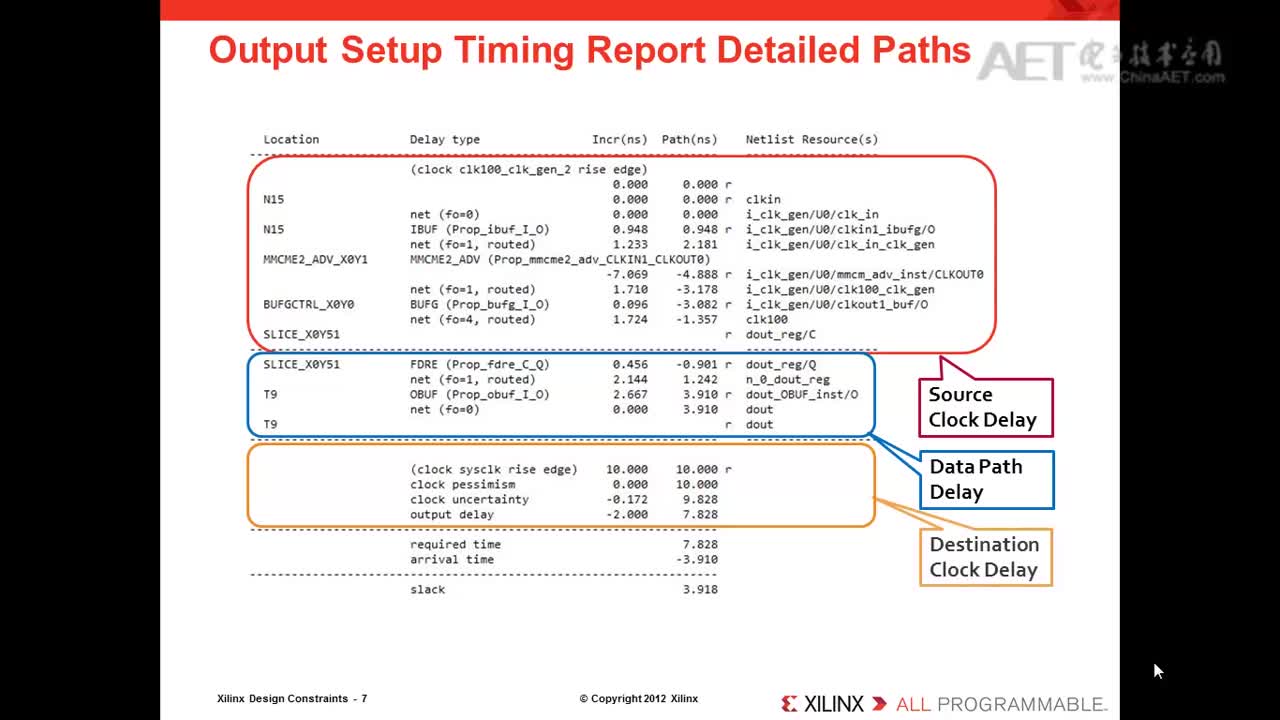

FPGA在與外部器件打交道時,端口如果為輸入則與input delay約束相關,如果最為輸出則output delay,這兩種約束的值究竟是什么涵義,在下文中我也會重點刨析,但是前提是需要理解圖1和圖2建立余量和保持余量。

2019-11-10 10:06:23 3740

3740

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5222

5222 1 I/O延遲約束介紹 要在設計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設計環境(IDE)僅在FPGA邊界內識別時序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 4453

4453 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個工藝級別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點 4.7系列

2020-11-13 18:03:30 14208

14208 本文檔的主要內容詳細介紹的是Xilinx的時序設計與約束資料詳細說明。

2021-01-14 16:26:51 32

32 有人希望能談談在做FPGA設計的時候,如何理解和使用過約束。我就以個人的經驗談談: 什么是過約束; 為什么會使用過約束; 過約束的優點和缺點是什么; 如何使用過約束使自己的設計更為健壯

2021-03-29 11:56:24 4598

4598

PCB設計-設置布線約束條件說明。

2021-04-13 09:54:24 0

0 AD5933 pmod Xilinx FPGA參考設計

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA參考設計

2021-04-22 13:35:23 11

11 引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2021-04-27 10:36:59 3217

3217

AD5628 pmod Xilinx FPGA參考設計

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA參考設計

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA參考設計

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA參考設計

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA參考設計

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA參考設計

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA參考設計

2021-05-24 10:29:20 18

18 本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-03-16 09:17:19 3285

3285

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1361

1361

Xilinx FPGA開發實用教程資料包免費下載。

2022-04-18 09:43:46 25

25 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-05-11 10:07:56 3595

3595

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

2022-07-25 15:37:07 2482

2482

約束文件是FPGA設計中不可或缺的源文件。那么如何管理好約束文件呢? 到底設置幾個約束文件? 通常情況下,設計中的約束包括時序約束和物理約束。前者包括時鐘周期約束、輸入/輸出延遲約束、多周期路徑約束

2022-12-08 13:48:39 946

946 FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 862

862 Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 380

380

FPGA設計中,時序約束對于電路性能和可靠性非常重要。

2023-06-26 14:53:53 939

939

ALLEGRO約束規則設置步驟(以DDR為例)

2022-12-30 09:19:29 10

10 Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 777

777

電子發燒友App

電子發燒友App

評論