軟件無線電(Software Radio)是指用軟件定義的、能實現(xiàn)多種功能的無線電通訊系統(tǒng),其核心思想是構造一個具有開放性、標準化、模塊化的通用硬件平臺,以將各種功能(如工作頻段、調(diào)制解調(diào)類型、數(shù)據(jù)格式、加密模式、通信協(xié)議等)用軟件來完成,從而通過加載不同的通信軟件來實現(xiàn)不同的通信模式和功能。由于功能的定義和實現(xiàn)都由軟件完成,所以可以通過配置不同的參數(shù)來支持不同電臺系統(tǒng)的互連互通,這使得軟件定義無線電具有很強的靈活性。

由于軟件無線電的諸多優(yōu)點,美軍的聯(lián)合戰(zhàn)術無線電系統(tǒng)(JTRS)計劃采用了軟件無線電的設計思想,并定義了軟件通信體系結(jié)構(SCA)規(guī)范。目的是實現(xiàn)電臺硬件的模塊化,軟件的可移植、可重用和可互操作性。將SCA體系結(jié)構逐漸擴展到2 GHz以上使用時,如果還在SCA的硬件體系結(jié)構中僅僅使用通用處理器(GPP)和DSP等,將無法滿足高速數(shù)字信號處理發(fā)展的需求,因此,能更好適應高速數(shù)字信號處理的可編程器件(FPGA)將不可避免的需要應用到SCA的硬件平臺中。目前,F(xiàn)PGA并不支持CORBA中間件,故不能直接應用到SCA體系結(jié)構中。另外,由于FPGA芯片的外部輸入/輸出端口沒有像通用處理器和DSP芯片那樣從應用程序中抽象出來,當每次應用程序代碼移植到新的平臺時,這些接口都要改變,這一點不利于實現(xiàn)波形應用的可移植性。

SCA3.0規(guī)范中提出了硬件抽象層連接(HAL-C)的概念。硬件抽象層可對具體硬件的實現(xiàn)進行抽象,它介于硬件平臺和運行于硬件平臺上的軟件之間。負責完成軟件設計中與硬件相關的內(nèi)容,并完成相關的接口功能,它可使軟件的設計很好地獨立于硬件,從而有效地提高軟件設計的可移植性。使得在JTRS設備的開發(fā)過程中能實現(xiàn)應用軟件的設計與通用硬件平臺的開發(fā)相分離,盡可能減小硬件平臺的具體結(jié)構對應用軟件設計的影響。

1硬件抽象層的基本概念及結(jié)構

HAL-C通過對硬件單元的對外接口進行抽象,從而定義了一系列標準的通信應用編程接口(API),以實現(xiàn)與外部的通信功能。這樣,當要求與外部通信時,僅需要通過對定義好的不同的API進行調(diào)用即可,這將極大地減小硬件平臺結(jié)構對軟件設計的影響,有效地降低對重要軟件組件接口進行重新編寫的可能性。

1.1基本概念

在硬件抽象層概念中,波形(Waveform)一般是指為了實現(xiàn)信息的無線傳輸而對信息所采取的一系列變換,一般包括無線通信雙方為實現(xiàn)傳輸而采取的所有協(xié)議;處理元件(Processing Element,PE)是指一個能夠執(zhí)行信號處理功能的硬件組件,通常GPP、DSP、FPGA、ASIC或者其它的能夠執(zhí)行信號處理功能的硬件設備都可以看作是一個處理元件;硬件抽象層組件(HAI-CCompONent,HC)是完成一定處理功能的一個功能模塊,它屬于波形應用的一個部分,通常HC是一個執(zhí)行于目標設備上的、由波形開發(fā)人員編寫的軟件模塊,HC需要運行于一個給定的PE上,且同一個PE可以運行多個HC。

1.2硬件抽象層基本結(jié)構

硬件抽象層連接時,可根據(jù)不同硬件模塊的特點對硬件模塊進行抽象,抽象后的硬件再對外接口。對于軟件模塊的設計者來說,只是提供收發(fā)數(shù)據(jù)的功能,那么,具體如何實現(xiàn)收發(fā)功能即不需要軟件設計者考慮。其典型的HAL-C模型如圖1所示。

如圖1所示,組件一般用于實現(xiàn)應用功能。這類組件由波形開發(fā)者依據(jù)HAL-C應用接口進行設計,而在硬件平臺上則依據(jù)PE的具體環(huán)境實現(xiàn)這些HAL-C應用接口。由硬件平臺提供的HAL-C應用接口可給HC提供一個底層的通信接口,這些底層API的主要目的是讓同一或者不同PE上的HC能夠通信。HC1、HC2之間的通信并不是直接進行的,而是通過HAL-C提供的通信機制來實現(xiàn)。HC1、HC2的開發(fā)者只需要把數(shù)據(jù)發(fā)送給HAL就可以了。具體數(shù)據(jù)如何從HC1傳輸?shù)紿C2,則是硬件抽象層要完成的工作。

通常可用一個貯存在HAL-C基層結(jié)構的簡單傳輸模塊Tx來描述數(shù)據(jù)的傳輸。有兩種類型的傳輸需要描述,一種是貯存在不同PE上的HC之間通過物理信道進行數(shù)據(jù)和控制信號的傳輸,如圖1中HC2到HC3的數(shù)據(jù)傳輸。它可以通過不同的物理信道實現(xiàn)(如PCI,RapidIO等),物理信道可以看作是傳輸在硬件平臺上的映射;另一種傳輸是在硬件內(nèi)部進行的傳輸,雖然組件自己可以實現(xiàn)數(shù)據(jù)的傳輸,但是若使用硬件抽象層連接來約束這種傳輸,則能提高組件的通用性。

為了簡化上面的連接模型,這里引入了end-point的概念。即一條從HC出發(fā),通過傳輸模塊的路徑被指定為一條邏輯通道。HC可使用HAL-C應用接口來訪問endpoint,以發(fā)送和接收數(shù)據(jù)。HAL-C基層結(jié)構負責把數(shù)據(jù)通過邏輯信道移動到指定的endpoint,這就可以把以前HC開發(fā)者應該做的工作轉(zhuǎn)移到硬件抽象層中來實現(xiàn),從而使波形開發(fā)與硬件相關資源相分離。

2 FPGA硬件抽象層連接接口

SCA規(guī)范中使用了兩種類型的接口:“provides”和“uses”。其中“provides”接口用來提供服務,“uses”接口用來使用這種服務。這種思想可被擴展應用到FPGA的組件級。也就是把一個由HAL-C基層結(jié)構向組件提供數(shù)據(jù)的接口定義為HAL-C基層結(jié)構的“provides”端口,然后由組件利用HAL-C基層結(jié)構的“uses”端口給其它組件提供數(shù)據(jù)。HAL-C API希望HC通過通用接口來發(fā)送和接收數(shù)據(jù)。在FPGA上,可使用source和sink來定義SCA中的這兩種端口。這些接口通常以線路和信號的形式存在。

2.1 source接口

source接口用于從HC向HAL-C基層結(jié)構傳遞數(shù)據(jù),它可根據(jù)硬件平臺的實現(xiàn)來確定信息被發(fā)送到指定的HC中。

source接口應當實現(xiàn)的信號如下:

clock:接口的同步時鐘,所有信號均應與該時鐘同步;

data:數(shù)據(jù)總線,其寬度可以是1,8,16,32,64位;

channel:與數(shù)據(jù)傳輸相關的邏輯通道號;

length:定義數(shù)據(jù)緩沖區(qū)中要傳輸?shù)淖止?jié)數(shù),可用MAXBUFFERSIZE描述數(shù)據(jù)的最大長度;

write:傳輸數(shù)據(jù)的使能信號;

socketRequest:寬度為MAXSOURCESOCK-ETS的矢量,用于描述一個指定的邏輯信道接口正在請求訪問sink的邏輯信道;

socketReady:寬度為MAXSINKSOCKETS的矢量所包含的一個流控制信號,用以應答source接口的請求信號。

source接口模塊如圖2所示。

2.2 sink接口

sink接口主要用于從HAL-C基層結(jié)構接收數(shù)據(jù)并送給HC。sink接口應當接收source接口輸出的信號,它應當接收大小由length信號確定的數(shù)據(jù)。socketReady表示當sink接口從source接口接收數(shù)據(jù)時的寬度,該寬度為MAXSINKSOCKETS的矢量所包含的一個流控制信號,是為source端口應答的信號。

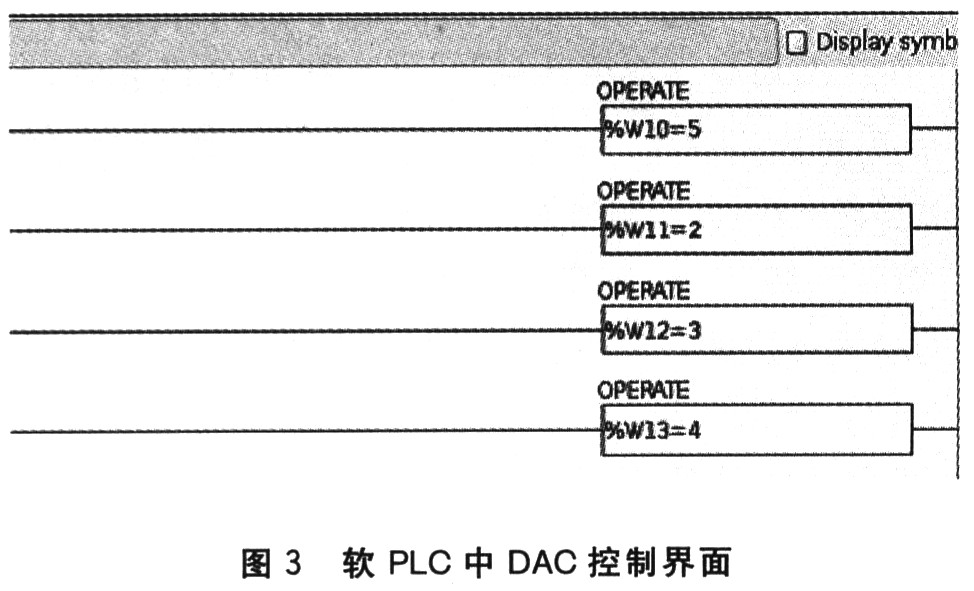

圖3所示為sink接口模塊圖。

2.3 source和sink的典型應用模型

FPGA是硬件可編程設備,F(xiàn)PGA的內(nèi)部功能模塊可通過直接線路或總線相互連接。這意味著一個包含多個功能模塊的FPGA內(nèi)部體系可以被分解成分散的子模塊,這些子模塊可通過外部連接機制相互連接。圖4所示是FPGA內(nèi)部使用sink和source的典型模塊圖。

在FPGA上運行的波形組件,在設計時只需要按照HAL-C所定義好的格式設計好波形組件與HAL-C的交互即可。數(shù)據(jù)與其他模塊間交互的具體過程可交給HAL-C去完成,即將與具體接口相關的工作交由HAL-C去完成。也就是說,在進行軟件設計時不需要關心底層硬件模塊能為軟件設計提供怎樣的具體端口形式,而只要硬件抽象層模塊能夠滿足軟件模塊設計所需的數(shù)據(jù)傳輸速率就行。

3 在硬件平臺上實現(xiàn)HAL-C應用

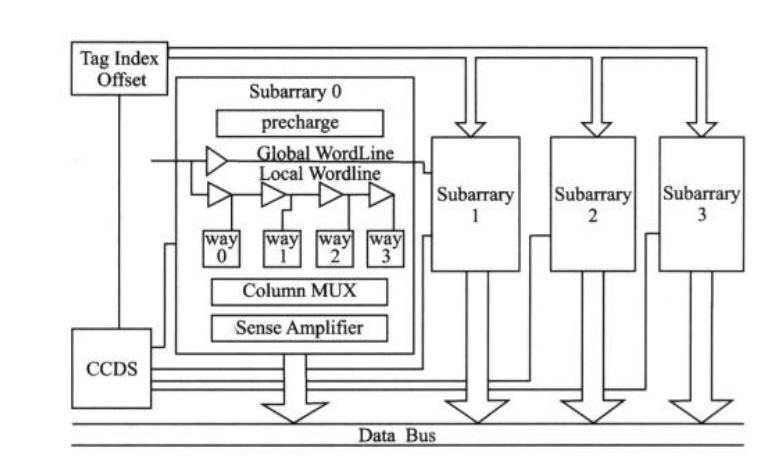

為實現(xiàn)SCA規(guī)范下的數(shù)字信號處理功能,可以設計一個通用硬件平臺,其結(jié)構如圖5所示。該方案以FPGA、DSP為信號處理平臺的算法核心,以CPLD為結(jié)構的控制核心,從而構造一個具有通用性、可擴充、易升級的多功能信號處理平臺。

本設計中的FPGA采用Xilinx公司Virtex 5系列的2200萬門器件XC5VLX220-1FF1760I以及500萬門器件XC5VSX95T-lFF1136I。DSP選用TI公司的TMS320C6416T,該DSP具有的豐富的集成外設,可適應各種不同的應用需求。通用FLASH采用Spansion公司的S29GL512N10TAI高密度NOR型FLASH。S9GL512N的容量高達512Mbit,可以存儲多個版本的DSP和FPGA程序。NOR型FLASH的讀操作時序和EEPROM相同,讀/寫操作最短周期為100NS,可以直接用于DSP的BOOT引導。TMS320C6416T與CPLD配合,可以控制FPGA配置文件的下載過程。FPGA芯片通過高速并行接口可與AD和DA直接相連,以進行高速的數(shù)字處理。DSP芯片可通過EMIFA(外部存儲器接口)接口與FPGA進行通信。

在實際應用中,平臺需以多模式的方式工作,并應根據(jù)需要實時更新功能程序。因此,用戶可在FLASH芯片中劃分區(qū)域,以將多種功能程序分別存儲在不同區(qū)域,并確定區(qū)域首地址。系統(tǒng)上電復位后,DSP和FLASH芯片先完成初始化,之后DSP會按照默認方式訪問默認首地址并加載默認DSP和FPGA功能程序,以便系統(tǒng)工作在默認模式下;當需要更新模式時,主控設備先發(fā)送指令,DSP檢測到指令后,DSP便按照指令要求查到對應首地址,并從新功能的首地址開始為DSP和FPGA加載新的功能程序,系統(tǒng)即工作在新模式下。如此便可在同一個硬件平臺上,通過動態(tài)調(diào)用不同的軟件程序來實現(xiàn)多功能、多模式的工作。

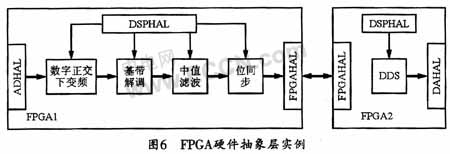

利用此硬件平臺還可實現(xiàn)MSK數(shù)字調(diào)制解調(diào)功能。FPGA的硬件抽象層的實現(xiàn)可將FPGA與外部接口在FPGA內(nèi),用一個專用的小模塊來實現(xiàn)對外交互,并在這個特定模塊里定義好HC與外部交互的接口形式(如數(shù)據(jù)總線,相關的時鐘信號、控制信號等)。然后根據(jù)功能需要在FPGA內(nèi)為AD、DA、DSP、CPLD以及互連的FPGA抽象出獨立的標準通信接口模塊ADHAL、DAHAL、DSPHAL、CPLDHAL和FPGAHAL,另外,還需要設計MSK調(diào)制和解調(diào)的HC模塊,其中調(diào)制部分包括DDS和數(shù)字正交上變頻兩個子模塊。數(shù)字正交上變頻可采用AD9779來實現(xiàn)。解調(diào)部分主要包括數(shù)字正交下變頻、基帶解調(diào)、中值濾波和位同步四個子模塊。這些HC模塊均為獨立的文件,而且各個模塊的參數(shù)均可配置。這樣便可利用上述編制好的文件來實現(xiàn)MSK調(diào)制解調(diào)功能。事實上,只需要在一個工程中把用到的文件包含進來,并在頂層文件中實例化各個模塊,同時根據(jù)實際硬件連接約束FPGA的引腳,最后通過綜合實現(xiàn)并生成FPGA配置文件,再用DSP和CPLD來完成配置,即可實現(xiàn)如圖6所示的FPGA內(nèi)部抽象層。也可以通過主機動態(tài)配置各個模塊的參數(shù)以及連接關系,以實現(xiàn)不同頻段的調(diào)制和解調(diào)。如果要完成其它方式的數(shù)字調(diào)制解調(diào),只需要把MSK調(diào)制和解調(diào)的HC模塊替換為其他數(shù)字調(diào)制解調(diào)算法,并通過主機發(fā)送指令重新對FPGA進行配置即可。這樣就可提高軟件模塊的可移植性、可重用和可互操作性。

4結(jié)束語

通過HAL-C提供的平臺,不但可使波形應用開發(fā)者從底層硬件的細節(jié)處理中脫離出來,專注實現(xiàn)組件的算法功能,而且,基于FPGA硬件抽象層連接設計的軟件,還具有很好的可移植性,因而能有效縮短系統(tǒng)開發(fā)周期,提高系統(tǒng)開發(fā)效率。

電子發(fā)燒友App

電子發(fā)燒友App

評論