在當前的數字集成電路設計中,同步電路占了絕大部分。所謂同步電路,即電路中的所有寄存器由為數不多的幾個全局時鐘驅動,被相同時鐘信號驅動的寄存器共同組成一個時鐘域,并可認為同時時鐘域內所有寄存器的時鐘沿同時到達。

然而,在實際電路中,同時鐘域內寄存器時鐘沿的到達時間存在偏差,即時鐘偏差。通過合理的時鐘設計,可以減少這種時鐘偏差,使其相對時鐘周期可以忽略不計,從而達到同步的效果。

1 ASIC的時鐘電路

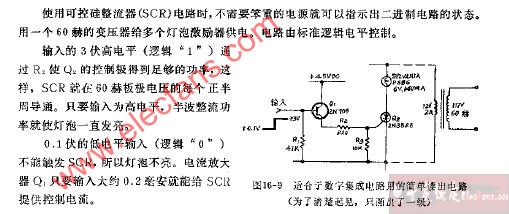

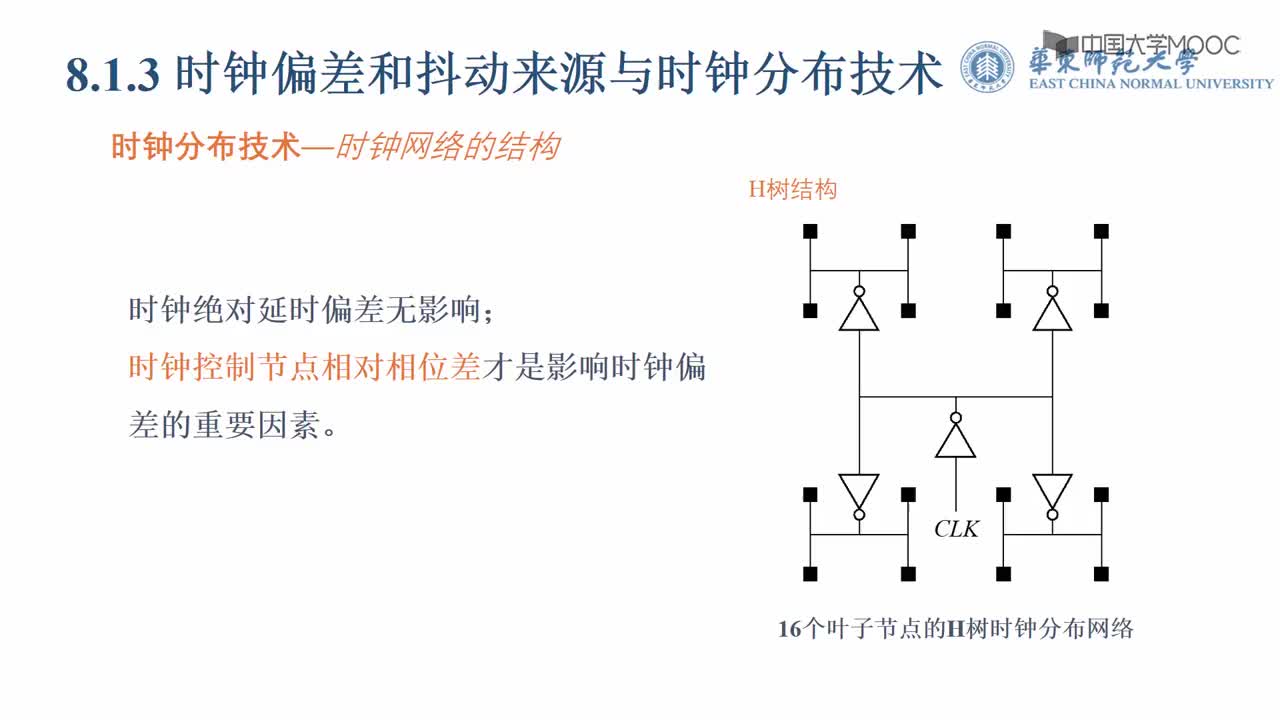

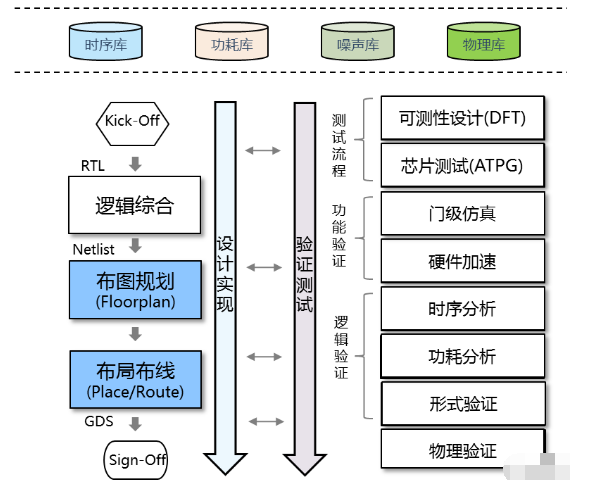

在ASIC的電路設計中,自動布局布線工具使用動態搭建時鐘緩沖器樹的方法來解決時鐘偏差問題。其基本思想就是控制時鐘源與寄存器之間的門延時與線 路延時。如果同時鐘域內所有寄存器的時鐘端與時鐘源之間的路徑,包含大體相同的時鐘緩沖器個數與連線長度,就可以近似地認為時鐘信號從時鐘源到各寄存器時 鐘端的延時是相等的,因此寄存器間的時鐘偏差可以忽略不計。

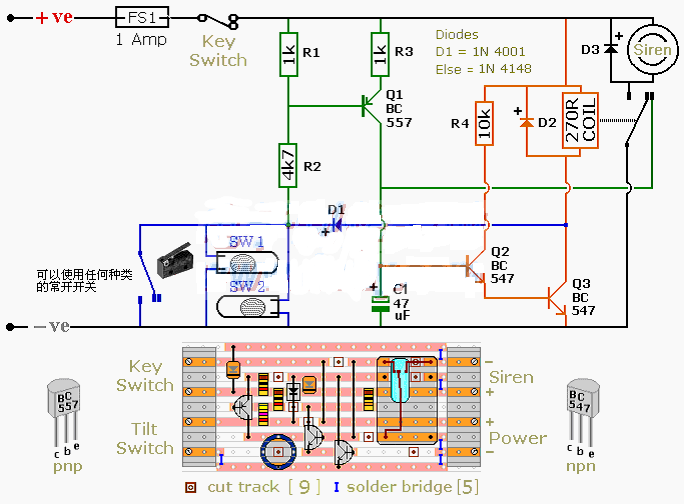

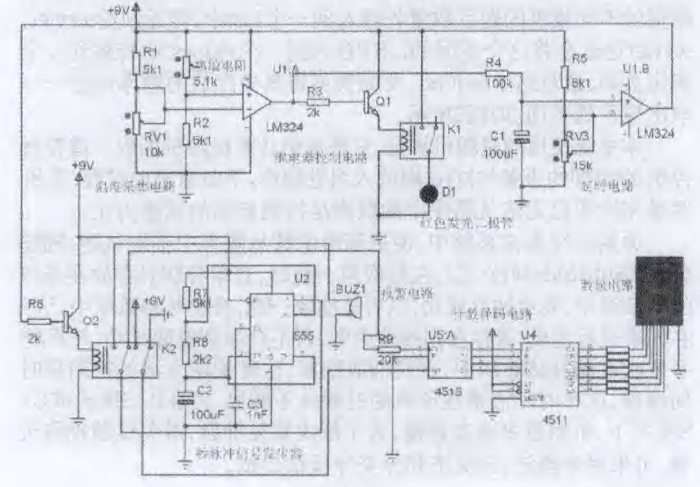

ASIC時鐘樹結構如圖1所示。

2 FPGA的時鐘電路

隨著FPGA集成度的不斷提升,單片FPGA已經可以完成百萬門級的集成電路設計。因此,很多ASIC設計可以利用FPGA完成流片前的功能驗證。 甚至直接使用FPGA進行商業生產。但是,FPGA的特殊結構決定了基于FPGA的設計不能直接照搬在ASIC設計當中的某些經驗,時鐘設計便是其中較突 出的一條。ASIC時鐘樹結構如圖1所示。

由于FPGA的生產工藝,在出廠之前,FPGA內部元件之間的連線已經完全固定。同時,FPGA具有連線延時相對門延時較大的特點,造成FPGA并 不能通過動態搭建時鐘緩沖器樹的方法解決時鐘偏差問題。實際上,時鐘樹結構已經被預先固化在芯片當中。針對Xilinx公司的Virtex Ⅱ系列的FPGA。其時鐘樹結構如圖2所示。

該系列FPGA直接利用單獨一層銅布線層搭建時鐘網絡。所有的時鐘信號,只能通過處于芯片縱向中軸線上下兩端的16個BUFGMUX進入時鐘網絡。 所有BUFGMUX輸出端一直延伸到芯片的中心,連接到銅布線層處于芯片中央縱向分布寬度為8的時鐘總線。縱向時鐘總線再連接到橫向的8條寬度為8的時鐘 總線,進而延伸到每一個CLB(Configurable Logic Block,可編程邏輯塊)的GRM(General Route Matrix,通用布線矩陣陣列)上。

也就是說,在Virtex Ⅱ結構的FPGA當中,最多可以存在16個時鐘域,然而同時只能存在最多8個全局時鐘(上下兩個對應的BUFGMUX共用一條時鐘總線)。由于每個寄存器 的時鐘端都通過橫向和縱向的時鐘總線連接到位于芯片中央的時鐘源,而時鐘源通過相同路徑長度的連線和BUFGMUX連接,因此可以認為從同一 BUFGMUX出發的時鐘信號到芯片內所有寄存器的延時相同,從而沒有時鐘偏差,經過實際工程驗證,同BUFGMUX構成的時鐘域內時鐘偏差最多不超過 0.3ns。

3 設計實例

為了更好的說明FPGA 時鐘電路的使用方法與其特殊的問題,下面將用一個在Virtex Ⅱ 6000 FPGA上實現的設計實例具體說明時鐘電路建立的方法。

3.1 問題分析

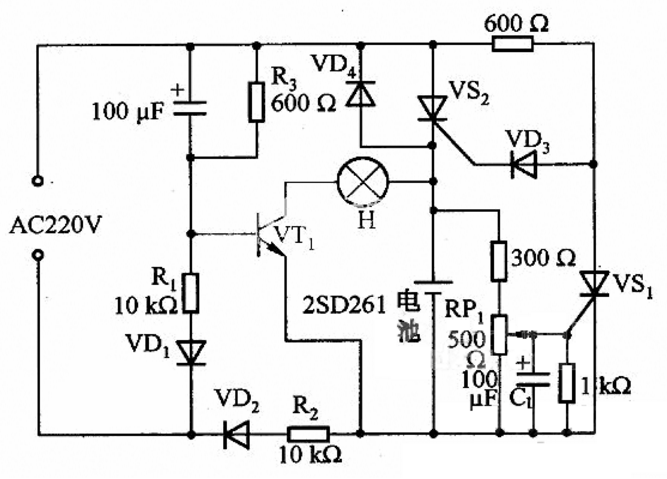

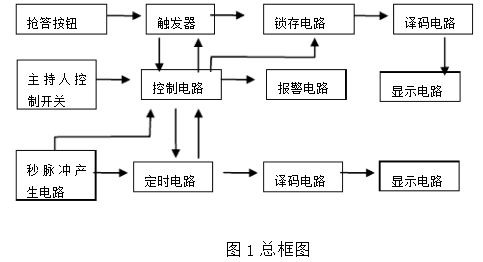

圖3顯示了在該設計當中的4個時鐘域。

這樣的時鐘結構,在ASIC的時鐘樹設計中,并不會引發很大的問題。但是在FPGA的設計中,如果不加處理,會引起電路綜合、布局布線的巨大壓力。其主要的問題源于FPGA綜合軟件對BUFGMUX的自動指定,造成門控時鐘和分頻時鐘與源時鐘之間出現較大的時鐘偏差。

一般,綜合軟件可以通過Verilog HDL的“posedge”和“negedge”關鍵字,或者VHDL當中的“event”關鍵字判斷出時鐘信號。然而,綜合工具并沒有判斷門控時鐘與分 頻時鐘的能力,即就是綜合工具認定的時鐘只能是一根網線,而不能穿越一般的邏輯門。為了讓同時鐘域的寄存器間沒有時鐘偏差。綜合工具會自動在時鐘的源頭為 時鐘信號指定BUFGMUX,使得時鐘信號使用銅布線資源。

經過綜合工具的自動指定,最終會將圖3當中時鐘結構轉換為圖4中的電路結構。

正如第2節所述,FPGA通過其特定的時鐘網絡,使得時鐘信號從BUFGMUX到每個CLB的時鐘端沒有時鐘偏差。但是,此結構的間接后果是為每個 CLB的時鐘端添加了一個相同的時鐘線延時,即從BUFGMUX通過時鐘網絡到達GRM的時間,在正常情況下,這個時間為6-7ns。

正是由于這一點,在綜合工具自動指定BUFGMUX之后,為了實現CLK_2XG這個門控時鐘,必須將CLK_2X時鐘信號通過與門,再經過 BUFGMUX重新連接到時鐘資源。顯而易見,CLK_2XG時鐘域的時鐘信號相對時鐘源CLK_IN來說經過了兩次BUFGMUX和CLK_2X的時鐘 域產生了至少6ns的時鐘偏差。同理,CLK_1XG和CLK_1X相應與CLK_2X之間存在12ns和6ns的時鐘偏差。相對CLK_2X 80MHz的時鐘頻率,一周期為12.5ns,顯然最大12ns的跨時鐘域的時鐘偏差是不能忍受的。從圖5的后仿波形當中,可以很明顯地看到這個時鐘偏差 達到了13.34ns。

3.2 解決方案

3.2.1 門控時鐘

實際上,BUFGMUX并不是簡單的時鐘緩沖器,他是一個具有低時鐘偏差、高驅動能力并帶有選擇端的雙路選擇器。使用不同的原語進行實例化,BUFGMUX可以構成時鐘選擇器、時鐘門控器或者簡單的時鐘緩沖器[1]。

盡管BUFGMUX就3種使用方式,但如果讓綜合軟件自動在合適的位置指定BUFGMUX,由于綜合軟件只能認出網線形式的時鐘信號,因而只會使用BUFG的方式使用BUFGMUX,造成了上述的問題。

為了去除由于門控時鐘造成的時鐘偏差,只能通過手動更改代碼,在合適的位置實例化BUFGMUX。在此例中可以為CLK_2X信號實例化BUFG原 語,而使用BUFGCE原語替代原來的與門,并直接使用CLK_IN為BUGCE的輸入。這樣CLK_2X和CLK_2XG都只經過了一個 BUFGMUX,因此可以近似地認為不存在時鐘偏差。同理CLK_1X和CLK_1XG之間的時鐘偏差也可以解決。

3.2.2 分頻時鐘

然而,BUFGMUX的3種使用方式并不能解決分頻寄存器造成的CLK_1X和CLK_2X之間的時鐘偏差問題。比較簡單的一種方法是使用CLK_IN作為分頻寄存器的輸入,而不對CLK_2X進行分頻。

盡管如此,由于分頻寄存器的器件延時和相應的連接線路延時,CLK_2X和CLK_1X之間仍然存在大約2-3ns的時鐘偏差,對于某些跨時鐘域的 關鍵路徑和時鐘保持(Hold Time)約束來說,仍然過大。另外,由于CLK_IN被分頻寄存器當作時鐘使用,可能會造成綜合軟件自動給CLK_IN指定BUFG,導致所有時鐘信號 都需要經過兩個BUFGMUX,產生一個12ns左右的輸入延時。

針對這種問題,可以使用FPGA當中的另一個特殊資源——DCM(Digital Clock Manager,數字時鐘管理單元)。DCM當中包含一個DLL(Delay-Locked loop,延遲鎖定電路),可以提供對時鐘信號的二倍頻和分頻功能,并且能夠維持各輸出時鐘之間的相位關系,即零時鐘偏差(更詳細的說明可查看參考文獻 [1,2]。

因此,針對分頻時鐘,可以直接利用DCM的分頻功能,從而省去分頻寄存器,徹底地解決了CLK_2X和CLK_1X之間的時鐘偏差。不過更合適的選擇是使用DCM的倍頻功能,這樣只需要為FPGA準備一個40MHz的低頻時鐘輸入,相對80MHz要更容易實現。

3.2.3 最終實現

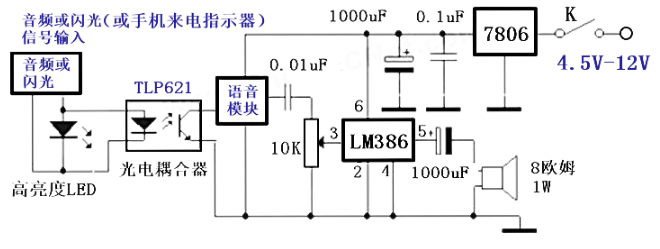

通過BUFGMUX和DCM的使用,可以將圖4改造為圖6所示的電路結構。

改造后,每個時鐘域的時鐘信號和信號源CLK_IN之間都只通過一個DCM和一個BUFGMUX,他們之間的時鐘偏差僅為時鐘網絡本身的時鐘偏差和 DCM的輸出到各BUFGMUX輸入端之間的線路延時偏差。如果進一步優化,通過在布局布線的步驟施加對BUFGMUX的位置約束,迫使圖5中的4個 BUFGMUX都處于FPGA的上方或者下方的8個BUFGMUX上,跨時鐘域的時鐘偏差在VIRTEX Ⅱ 6000FPGA當中可以控制在0.5ns以內,基本滿足80MHz的要求。改造后的時鐘電路的后仿波形如圖7所示,其最大的時鐘偏差為0.722ns。

實際上,DCM和BUFGMUX從VIRTEX Ⅱ開始,已經成為FPGA的標準元件,可以在SPARTAN-3,VIRTEX Ⅱ,VIRTEX Ⅱ PRO,VIRTEX-4等器件上直接使用,因此該電路結構也可相應推廣到這些FPGA的電路設計當中。

4 結語

本文通過比較ASIC時鐘樹結構和FPGA時鐘網絡的結構,說明了FPGA時鐘網絡的自身特點。通過一個設計實例,分析了直接使用綜合工具實現多時 鐘域的電路設計所存在的問題,并針對這些問題提出了利用BUFGMUX的三種使用方式代替門控時鐘與利用DCM代替分頻時鐘的方法,較好地解決了FPGA 時鐘電路的時鐘偏差問題,并具有一定的適用性。

電子發燒友App

電子發燒友App

評論