隨著基于FPGA進行原型設計的復雜性不斷增加,市場對更好調試技術的需求也日益增加。FPGA原型設計可用于驗證、早期軟件開發、概念證明等,因此變得非常重要。它的主要職責仍然是執行這些任務,而不是試圖找出因原型構建錯誤而造成的問題。

根據可用的設計或現有任務類型,可能需要不同的調試技術。采用合適的調試技術還可以縮短FPGA設計的驗證周期。

本文描述了有關FPGA的一些調試技術,采用這些技術可以加快驗證過程,文章同時也指出了它們的局限性。這些調試技術可以用于硅前驗證過程中所面臨的各種挑戰或問題,后面我們將會討論。

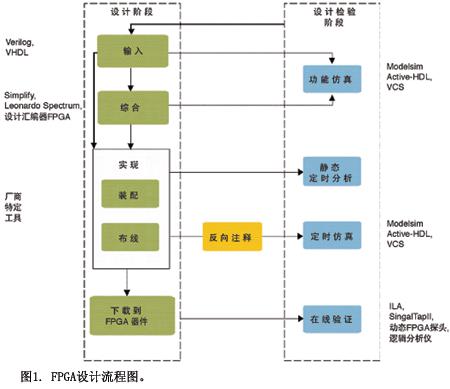

RTL仿真

在RTL還沒有完全穩定時,原型設計的一個主要需求是訪問和監控內部信號的活動,這有助于找到造成問題的根源,無論問題是由于原型錯誤還是RTL本身的一些異常造成的。

測試時,RTL仿真需要在模塊周圍建立一個完整的原型驗證仿真環境,能夠給予激勵,滿足內存要求(如果有的話),監控設計錯誤等。

圖1顯示了此類RTL仿真設計模型。

圖1:RTL仿真模型

圖字:要求 驗證計劃 原型RTL仿真 原型RTL模型 執行板上工作 找到Bug? 去除bug執行所有工作?

假設/優勢

● 此調試方法非常適用,而且在處理設計規模問題時,可以進行調整,目前驗證工具可以輕松地處理設計規模問題,但要求仿真時間不能很長,否則會使這種工作幾乎沒有ROI(投資回報率),而要配備復雜的測試臺。

● 如果是一個已經獲得驗證的設計,它能重新使用現有的驗證測試平臺,這樣就不需要從頭開始構建,可以節省時間和精力。

● 工作重點應該側重于調整現有測試平臺,以便使其不需要任何大的更改,就能夠運行驗證測試套件。

● 可以縮小問題,選擇只運行失敗仿真,減少對仿真的依賴,檢查可能引起問題的信號的仿真波形。

局限性

● 如果是大規模設計,幾乎不可能查看設計中的每個信號、監控其行為。

● 采用這種方法的一個前提條件是,驗證工程師或軟件工程師應該對設計和內部信號具有良好的洞察。

● 此方法比較費時,而且需要軟件開發人員付出額外的努力。

● 在設計被分區的情況下,RTL仿真可能沒有幫助。假設我們主要試圖“再利用”頂層驗證環境,并使其輕松為“受測設備原型”工作,要創建更多的層次和設計分區,則會需要進行額外的工作,以修改安裝在獨立驗證環境中的內部信號探針。

● 調試涉及復雜處理的大規模快速流輸出數據設計可能具有挑戰性,因為這個問題可能在設計層次的各個層級存在。

在復雜的設計中,必須考慮一些更好、更快的調試方式,我們將在后面的章節中討論。

使用邏輯分析儀的硬件調試

當調試總線位于FPGA的外部引腳上,并通過邏輯分析儀觀察它們時,硬件調試涉及內部信號的呈現。這種調試技術對小型邏輯設計真的非常有幫助,因為驗證工程師也可以使用邏輯分析儀觀察到內部設計信號,從而使調試更加方便快捷。

圖2顯示了此調試模型。

圖2:使用邏輯分析儀的硬件調試

圖字:邏輯分析儀 邏輯設計

在這里,可編程的邏輯設計在目標系統中高速運行,可以在真實環境下查看邏輯行為。

假設/優勢

● 如無法利用驗證測試平臺仿真環境,可以采用這種方法進行調試,因為從頭開始建立驗證測試平臺的仿真環境可能既繁瑣又費時。

● 此方法可以加快調試過程,因為它使驗證工程師能查看內部設計信號的活動。

● 此方法提供了一個進入運行設備的窗口,不需要執行任何額外的軟件任務。

● 由于所有驗證情況都在FPGA板上執行,因此這種方法可以用于設計,否則一般需要相當長的仿真時間。

局限性

● 設計人員需要手工調試設計,每次都需要手工編輯進行重復調試。調試需要內部節點,沒有在設計頂層就必須將它們路由到頂層。

● 電路板上的可用引腳數量制約著探針數量。

● 此方法需要在邏輯分析儀查看器中輸入信號名稱,以便跟蹤所顯示的設計信號,因而變得很繁瑣。

● 設計中的路由探針可能會導致設備運行或定時問題。

因此,用邏輯分析儀進行調試會非常耗時,喪失活力,不能用于調試復雜的設計。

插入板上調試邏輯

具有復雜邏輯實施的設計通常需要實時調試功能。這些都是更深入地洞察設計所必需的,無需建立復雜的測試平臺架構或實施外部硬件。

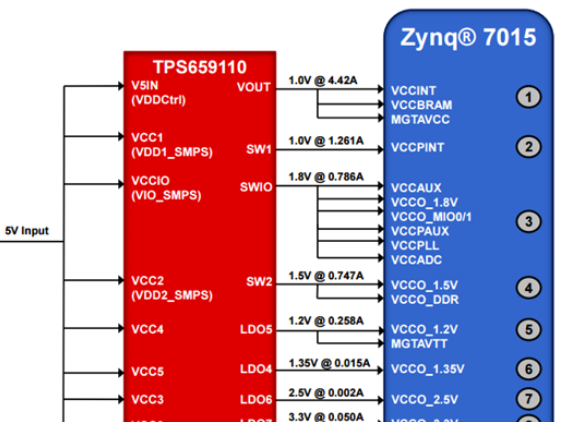

a) 插入調試邏輯以及基于FPGA的設計只需在初始時付出一些一次性的努力,因而可以節省調試時間和原本很大的精力。這將涉及編寫驅動的綜合邏輯,監控可以與設計本身集成、并可以移植到FPGA的IP。圖3顯示了使用板上調試邏輯的調試模型。

圖3:使用板上邏輯的調試模型

圖字:AHB,IPS通用界面 驅動IP 測試中的模塊 監控IP

另外,此板上邏輯可以使存儲器映射,以便通過調試器提取結果或在運行中驅動輸入。

b) 可以采用另一種方法讀取調試信號--使它們的存儲器映射。然后,可以使用調試器讀出這些值或通過CPU將這些值與這些信號的預測值進行比較。如果從設計輸 出數據出現的速度比讀出的速度更快,則可以實施FIFO。輸入數據能以更快的速率存儲,以更低的調試器時鐘頻率讀出。考慮到這兩個時鐘的頻率,可以確定 FIFO的深度。

假設/優勢

● 墊或GPIO消除可能因外部連接所引起的問題,因而不需要從外部驅動激勵。

● 頻率沒有被外部驅動頻率限制。

● 驅動激勵和監控結果是實時的,使調試速度更快。

● 顯示器完全不需要獲得外部引腳上的節點,因為可以從內部檢查它們,使用那些存儲器被映射的寄存器標記錯誤。

● 不需要位文件生成任何額外的循環來增加調試總線信號。

局限性

● 驅動器和顯示器需要是可綜合的,因此可能無法在驗證測試平臺重新使用它們。

● 驅動器和顯示器所使用的邏輯可能會導致過度利用FPGA資源。

● 采用此方法可能出現以下情況:如果其中任何一個有內存要求,而且超過了可用的FPGA資源,就不能實施驅動器和監視器。

● 添加額外的邏輯(如驅動器或監視器)可能導致難以滿足設計所需的時序要求。

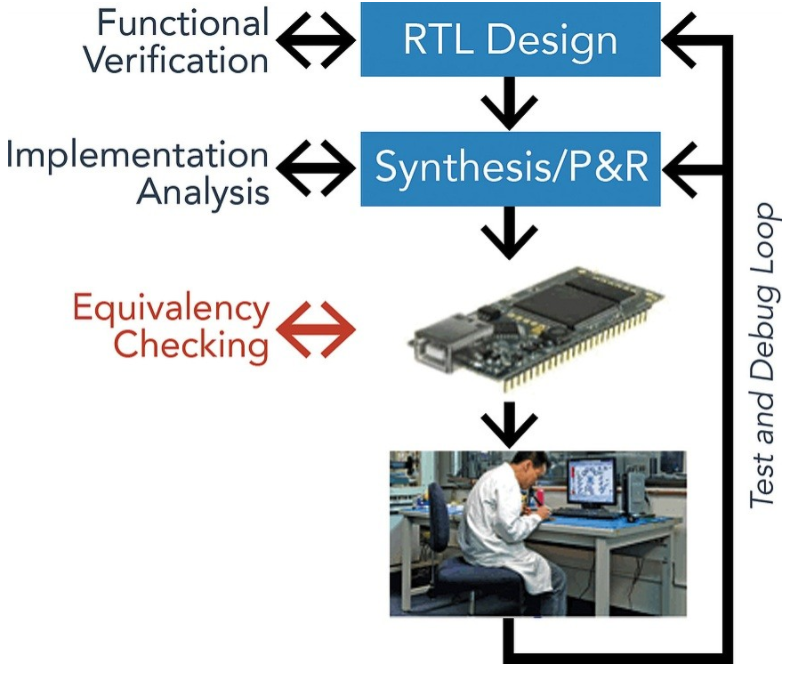

實時調試工具

這些調試工具不需要在板的頂層提取內部設計信號,并提供信號探測功能,以及實時調試。

在此類別中有多種工具,可用于實時調試設備。選擇合適工具的最佳方式將取決于設計的復雜性和功能以及所使用的FPGA技 術。這些工具在設計中用于插入探針,以便轉儲數據,并可控制啟動數據存儲的特定觸發器。設計得到檢測后,通過綜合、布局、布線在某個設備上實施,這樣,工 具提供的GUI界面可以用來檢查結果。使用這些工具可觀察到設計層次中的任何層級,因而不需要為了在設計頂層獲得它們而執行額外任務。

這樣的工具很少利用FPGA自身資源,像板上存儲器,用于儲存數據,而且它們不需要任何外部硬件。圖4顯示了此調試方法。

圖4:使用板上資源的調試工具

圖字:將波形從電路板中倒出,進行調試 信號探測 板上存儲器 邏輯設計

但這類工具所面臨的問題是:插裝探針后,設計在工作頻率和路由擁塞方面會有不可測的操作。

當然還有一些其他工具,也具有實時功能,可靈活配置運行觸發器。這些工具都配有相關硬件,因而提供必要的數據儲存,不使用任何FPGA資源。圖5顯示了這種調試方法。

圖5:使用外部硬件的調試工具

圖字:信號探測 將波形從電路板中倒出,進行調試 外部硬件(特定工具) 邏輯設計

假設/優勢

● 對于I/O數量相對較大的設計可以采用此調試方法,因為它不需要在電路板的頂層提取內部信號。

● 此方法可以用于設計仿真良好、但一旦集成到FPGA中、就不顯示預期行為的情況。同樣,調試這些問題需要不僅提供實時調試,而且還有信號探測功能的工具。

● 這些工具使調試過程變得相對容易,因為它們通常將波形/數據轉儲為使用最常用的仿真工具可以打開的格式。

● 這樣的調試工具還能儲存在自己的相關存儲器中捕獲的波形,它消耗FPGA板的資源,因而通常不用限制設計。

局限性

● 必需安裝外部硬件和軟件。

● 調試節點有數量限制。

● 設計層次的可見性取決于用于儲存轉儲數據的存儲器。

● 可獲得的頻率降低。

解決方法之一是:采用來自一個特定分層體或模塊的插裝信號創建同步build,這樣,可以采用調試模塊或塊的信號在比特流上運行一組測試。在執行階段遇到問題后,這肯定會節省創建build的時間。

本文小結

很顯然,現在還沒有出現公認的通用調試技術,而且沒有適合所有設計驗證的調試技術。不同的調試技術有不同的局限性和限制,但是,如果選擇得當,這些調試工具/技術真的可以有助于減少調試工作,縮短調試周期。

縮短調試時間可能成為加快硅前驗證的一個偉大的里程碑。加快硅前驗證是首要要求,這樣才能滿足上市時間需求,能夠推出第一個全功能硅。

電子發燒友App

電子發燒友App

評論