相比GPU和GPP,FPGA在滿足深度學(xué)習(xí)的硬件需求上提供了具有吸引力的替代方案。憑借流水線并行計算的能力和高效的能耗,FPGA將在一般的深度學(xué)習(xí)應(yīng)用中展現(xiàn)GPU和GPP所沒有的獨特優(yōu)勢。同時,算法

2016-07-28 12:16:38 7349

7349 DSP這幾年有點背,逐漸遠離主流 話題 ,所以有人就有了這樣的問題:DSP會被FPGA取代嗎? 網(wǎng)友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的 ARM 處理器替代。現(xiàn)在基本已

2022-11-29 10:25:02 4007

4007

頻傳。“FPGA將取代DSP”之聲日盛。這無疑撩動著傳統(tǒng)DSP大廠的敏感神經(jīng),德州儀器(TI)、CEVA、飛思卡爾、Microchip、ADI和NXP等早已紛紛表示了自己對于DSP技術(shù)未來發(fā)展的信心。

2013-12-27 14:47:49 9229

9229 DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護和升級,適合于實時視頻圖像處理,電機控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

本帖最后由 yicunyu 于 2016-7-18 16:45 編輯

DSP28335+FPGA的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA

2016-07-16 14:32:23

,DSP仿真器,網(wǎng)上大堆的,嫌不夠正規(guī),TI網(wǎng)站自己找教程和datasheet。FPGA:開發(fā)工具比較多,他分成綜合工具,仿真工具和開發(fā)板,綜合工具altera的Quartus和xilinx的ISE以及

2017-04-21 14:23:27

DSP亞洲業(yè)務(wù)區(qū)域經(jīng)理陸磊先生表示,未來FPGA與DSP更多是協(xié)同處理關(guān)系,由于雙方的可編程,重用性和算法升級都有共通性,因此,使用DSP或FPGA都能實現(xiàn)更低功耗和更高性能。 陸磊先生在被問到未來

2019-06-27 07:06:16

本人剛?cè)腴TFPGA,不知道如何實現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計,網(wǎng)上查詢有的說FPGA+DSP可以通過EMIF,IP核實現(xiàn),FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標要求大量的并行處理或者最大

2019-08-30 06:31:29

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

逐漸具備了與ASIC和ASSP相當?shù)男阅埽蛊浔粡V泛地應(yīng)用在各行各業(yè)的電子及通信設(shè)備中。FPGA、ARM和DSP與ASIC相比,FPGA、ARM和DSP都具備與生俱來的可編程特性。或許身處開發(fā)第一線

2021-11-02 06:30:00

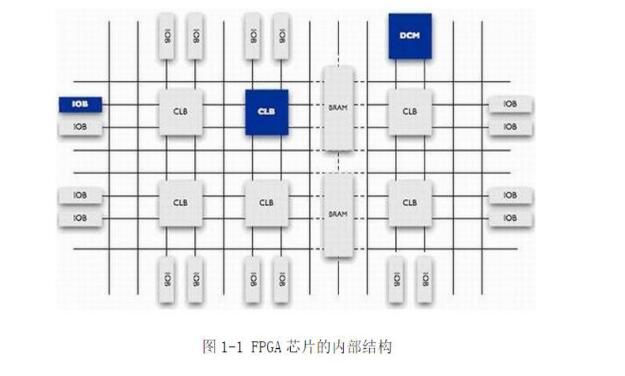

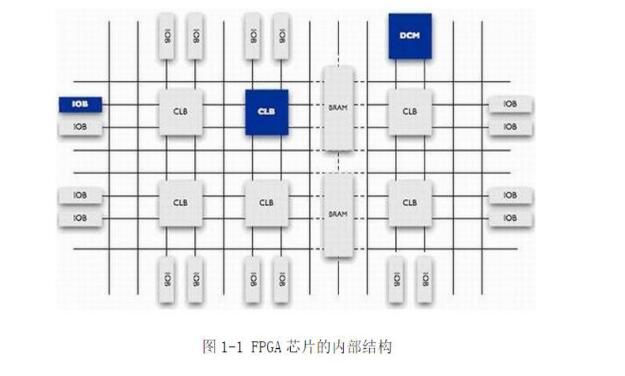

、功能多個角度解析兩者的不同。1、FPGA與DSP的特點FPAG的結(jié)構(gòu)特點片內(nèi)有大量的邏輯門和觸發(fā)器,多為查找表結(jié)構(gòu),實現(xiàn)工藝多為SRAM。規(guī)模大,集成度高,處理速度快,執(zhí)行效率高。能完成復(fù)雜的時序

2019-05-07 01:28:40

`電子發(fā)燒友網(wǎng)12月《處理器與DSP特刊》火熱下載 {:4_129:}近幾年,搭乘新興市場(智能工業(yè)、物聯(lián)網(wǎng)等)和先進半導(dǎo)體技術(shù)快速發(fā)展先機,FPGA憑借其性能優(yōu)勢不斷入侵并蠶食著DSP市場,以

2014-01-09 17:52:31

的多個硬件地址產(chǎn)生器; (7)可以并行執(zhí)行多個操作; (8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 FPGA是英文

2014-06-26 14:23:43

在嵌入式開發(fā)領(lǐng)域,ARM是一款非常受歡迎的微處理器,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協(xié)處理器,協(xié)助微處理器更好的實現(xiàn)產(chǎn)品功能。那三者的技術(shù)特點以及區(qū)別是什么呢?下文就此問題略

2013-05-06 15:56:02

隨著數(shù)字融合的進一步發(fā)展,系統(tǒng)的設(shè)計和實現(xiàn)需要更大的靈活性,以解決將完全不同的標準和要求整合為同類產(chǎn)品時引發(fā)的諸多問題。本文介紹FPGA在視頻處理中的應(yīng)用,與ASSP和芯片組解決方案相比,FPGA可根據(jù)目前設(shè)計工程師的實際需求提供不同層次的靈活性,并保持明顯優(yōu)于傳統(tǒng)DSP的性能。

2019-08-22 08:21:21

都可以用FPGA的邏輯門搭出來的。MCU編程和應(yīng)用相對簡單,不過只能用于地端產(chǎn)品,高端的話只能用ARM了。不過成本相對較低。DSP其實就是一種高端的MCU,它是在單片機的基礎(chǔ)上增加了很多個硬件乘加器

2018-08-30 09:13:25

等領(lǐng)域FPGA行使DSP“職能”,通過嵌入處理器核取代MCU一些應(yīng)用,FPGA未來發(fā)展空間惹人想象。 FPGA向DSP領(lǐng)域加速滲透一項研究顯示,在多個DSP高端應(yīng)用中FPGA將扮演越來越重要的角色

2013-12-25 19:37:36

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計算機算法的概念、理論、有限字長效用、FIR和IIR濾波器的實現(xiàn)、多速率和自適應(yīng)信號處理的FPGA實現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:22:42

可使產(chǎn)品上市時間更快,并具有更小的風(fēng)險。FPGA庫中的DSP核心不斷增加,許多現(xiàn)在就可使用。結(jié)果,設(shè)計人員可以利用比定制門陣列方案或多處理器解決方案所需要的時間短得多的時間就完成一項DSP設(shè)計。 加快

2011-02-17 11:21:37

Q1:FPGA設(shè)計與DSP設(shè)計相比,最大的不同之處在哪里? A1:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現(xiàn),但是它們的側(cè)重點有所不同。這里涵蓋的說一下。 1) 內(nèi)部資源

2019-06-27 06:22:39

Q:FPGA設(shè)計與DSP設(shè)計相比,最大的不同之處在哪里?A:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現(xiàn),但是它們的側(cè)重點有所不同。這里涵蓋的說一下。1) 內(nèi)部資源FPGA側(cè)重于設(shè)計具有

2019-04-10 08:00:00

請問一下各位牛人,我看spartan那個fpga里面有dsp 資源,我需要做一些浮點運算,請問fpga里面的dsp是怎么才能使用的啊,謝謝

2019-10-15 13:37:46

支持;(6)具有在單周期內(nèi)操作的多個硬件地址產(chǎn)生器;(7)可以并行執(zhí)行多個操作;(8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些

2021-09-08 17:49:20

;(7)可以并行執(zhí)行多個操作;(8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。FPGA是(Field

2019-04-01 06:20:23

STM32學(xué)習(xí)筆記①ARM、MCU、DSP、FPGA、SoC各是什么?區(qū)別是什么?(轉(zhuǎn))ARM、MCU、DSP、FPGA、SoC的比較CMSIS標準ARM、MCU、DSP、FPGA、SoC各

2021-12-09 07:08:05

Altera,就是對這一點篤信不疑。未來是萬物互聯(lián)的時代,而不斷部署在我們世界各處的傳感器將會采集到大量的數(shù)據(jù)。這些數(shù)據(jù)都會被上傳到云服務(wù)器中,通過數(shù)據(jù)中心來進行存儲和計算,而這些數(shù)據(jù)的采集和存儲都離不開FPGA。FPGA將是連接云服務(wù)和傳感設(shè)備之間的重要紐帶。`

2017-01-06 18:00:47

FPGA讀寫并行數(shù)據(jù)。在本例中數(shù)據(jù)總線的寬度取決于所使用的DSP的數(shù)據(jù)位。由于目前DSP處理器的多為64位或32位,而完成數(shù)據(jù)交互使用8位就夠了,因此這里采用8位的數(shù)據(jù)總線cpu_data[7..0

2011-03-17 10:23:56

我一直在使用TI TMS320c6713 DSP處理器開發(fā)DSP應(yīng)用程序,但我想看看與這個處理器或任何其他專用浮點處理器相比,FPGA的性能如何。最近我很高興地看到FPGA已經(jīng)準備好用于許多浮點

2019-05-31 12:38:52

TI科學(xué)家談浮點DSP未來發(fā)展 自十多年前浮點數(shù)字信號處理器(DSP)誕生以來,便為實時信號處理提供了算術(shù)上更為先進的備選方案。不過,定點器件至今仍是業(yè)界的主流--當然低成本是主要原因。定點DSP每

2009-11-03 15:18:49

處理器的數(shù)目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現(xiàn)。本課程以DSP設(shè)計在FPGA芯片上的開發(fā)為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

本帖最后由 mr.pengyongche 于 2013-4-30 02:22 編輯

DSP和FPGA是嵌入式開發(fā)處理器的三大巨頭之二,很多剛剛接觸嵌入式的朋友都會心存疑問,到底DSP和FPGA

2011-08-12 20:30:25

處理器的數(shù)目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現(xiàn)。本課程以DSP設(shè)計在FPGA芯片上的開發(fā)為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-24 13:07:08

arm,asic,dsp,fpga,mcu,soc各自的特點人工智能受到越來越多的關(guān)注,許多公司正在積極開發(fā)能實現(xiàn)移動端人工智能的硬件,尤其是能夠結(jié)合未來的物聯(lián)網(wǎng)應(yīng)用,對于移動端人工智能硬件的實現(xiàn)

2021-11-11 07:35:31

申請理由:學(xué)習(xí)DSP 和FPGA DSP優(yōu)越的計算能力 超高的編解碼速度 和FPGA 聯(lián)合使用 取長補短 快速實現(xiàn)視頻傳輸不是夢 。第一次申請。現(xiàn)在進行FPGA 的視頻傳輸部分項目描述:項目描述:先

2015-09-10 11:18:56

Q:FPGA設(shè)計與DSP設(shè)計相比,最大的不同之處在哪里?A:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現(xiàn),但是它們的側(cè)重點有所不同。這里涵蓋的說一下。1) 內(nèi)部資源FPGA側(cè)重于設(shè)計具有

2019-08-11 08:00:00

、現(xiàn)場可編程門陣列(FPGA)和數(shù)字信號處理器(DSP)。1.1. FPGA作為GPU在算法加速上強有力的競爭者,FPGA是否立即支持不同硬件,顯得尤為重要。FPGA與GPU不同之處在于硬件配置靈活

2018-08-13 09:33:30

本帖最后由 cytechsunsong 于 2017-12-17 02:27 編輯

DSP Builder 和DSP Builder Advance 的64位破解器,通吃過去、現(xiàn)在、未來的版本

2017-12-10 17:26:52

與DSP相比,St72141的缺點是什么?以上來自于谷歌翻譯以下為原文 what is the shortcoming of St72141 comparing with DSP

2019-01-25 12:13:58

語言、功能多個角度解析兩者的不同。[/url] 1、FPGA與DSP的特點 FPAG的結(jié)構(gòu)特點 片內(nèi)有大量的邏輯門和觸發(fā)器,多為查找表結(jié)構(gòu),實現(xiàn)工藝多為SRAM。規(guī)模大,集成度高,處理速度快,執(zhí)行

2016-12-23 16:56:04

,DSP是為各種數(shù)學(xué)運算量身打造的。圖1.4 DSP處理器相比之下,套用近些年業(yè)內(nèi)比較流行的一句廣告詞“All Programmable”來形容FPGA再合適不過了。ARM雖然有很多外設(shè),DSP雖然具備強大

2017-09-23 22:20:59

,數(shù)字信號處理與數(shù)字圖像處理沒有太大區(qū)別),就意味著可以用FPGA做硬件設(shè)計來實現(xiàn)DSP芯片的功能,當然,相比較專業(yè)的DSP芯片 成本太高,因此你也沒必要選擇FPGA+DSP,就選擇DSP芯片,算法...

2021-07-28 09:16:02

FPGA一般用來控制整個系統(tǒng)的時序,本設(shè)計采用集成微處理器的FPGA,同時完成信號模擬和時序控制的功能,改變了以往信號處理DSP+FPGA中FPGA作為協(xié)處理器的模式[1-3]。整個設(shè)計僅需要具有嵌入

2019-07-15 06:48:33

基于DSP與FPGA的運動控制器設(shè)計設(shè)計了一種基于DSP和FPGA的四軸伺服電機運動控制器,該控制器選用DSP與FPGA作為核心部件。針對運動控制中的一些具體問題,如高速、高精度、實時控制等,規(guī)劃

2009-09-19 09:43:00

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-10-12 06:40:30

的邏輯處理和控制算法,能實現(xiàn)多軸高速高精度的伺服控制。利用DSP與FPGA設(shè)計運動控制器,其中DSP用于運動軌跡規(guī)劃、速度控制及位置控制等功能;FPGA完成運動控制器的精插補功能,用于精確計算步進電機或伺服驅(qū)動元件的控制脈沖,同時接收并處理脈沖型位置反饋信號。那么,我們具體該怎么做呢?

2019-08-06 06:27:00

,生命周期縮短。實現(xiàn)功能強、性能指標高、抗干擾能力強、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號處理器已經(jīng)勢在必行。過去單一采用DSP處理器搭建信號處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。

2019-11-06 08:34:27

小七免殺論壇vip 2013源碼免殺培訓(xùn)課程目錄(今日免key發(fā)布)小七免殺論壇vip 2013源碼免殺培訓(xùn)課程解壓密碼:www.fanlu8.com如果www.fanlu8.com密碼不得就在

2012-10-05 17:35:17

,生命周期縮短。實現(xiàn)功能強、性能指標高、抗干擾能力強、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號處理器已經(jīng)勢在必行。過去單一采用DSP處理器搭建信號處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。

2019-08-19 06:38:12

這幾年有點背,逐漸遠離主流話題,所以有人就有了這樣的問題:DSP會被FPGA取代嗎?小編總結(jié)了各個網(wǎng)友的回答: 網(wǎng)友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的ARM處理器替代

2021-07-16 08:12:03

”視頻分析市場面臨著諸如安裝成本、源視頻質(zhì)量、攝像機處理能力以及實時判決等的重大挑戰(zhàn),相比傳統(tǒng)工控機或DSP方案,FPGA的解決方案究竟有何優(yōu)勢?基于FPGA的視頻分析解決方案無論在成本、性能、市場定制

2013-12-16 19:15:49

我做的一個基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個系統(tǒng),包括信號處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時鐘輸入為15MHz

2023-06-19 06:43:17

,與單獨的數(shù)字信號處理器相比,FPGA 技術(shù)能夠為高難度的 DSP 問題提供大為簡化的解決方案。要明白其中的緣由,需要回顧一下 DSP 的肇始和發(fā)展。用于實現(xiàn)專門目的的微處理器在過去二十年里,傳統(tǒng)

2018-08-15 09:46:21

的熱量轉(zhuǎn)化為電能,這或許能夠在未來讓可穿戴設(shè)備的續(xù)航大大增強,甚至再不用充電了。把熱能轉(zhuǎn)化為電能的貼片之前就曾出現(xiàn)過,不過由韓國先進科技學(xué)院(KAIST)開發(fā)出來的這個版本,可以在電量輸出最大化的同時

2016-02-23 15:49:26

介紹了一種基于DSP和FPGA的GPS-B碼時統(tǒng)終端系統(tǒng)的設(shè)計方案,提出了一種利用FPGA對IRIG-B碼進行解碼的設(shè)計方法。詳細論述了具體的設(shè)計方案及軟硬件的實現(xiàn)。通過將快速的DSP與FPGA相結(jié)

2010-02-24 13:48:49 22

22 FPGA實現(xiàn)DSP應(yīng)用

摘要:具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結(jié)構(gòu)和性能,不僅可實現(xiàn)VLSI DSP,且具有系統(tǒng)

2010-04-01 15:39:54 14

14 FPGA的DSP應(yīng)用

近年來由于多媒體技術(shù)和無線通信的發(fā)展,對DSP應(yīng)用的要求不斷地增長,但是這些應(yīng)用對信號處理要求高,需要采用處理速度高的硬件來實現(xiàn)DSP,所以,隨著CMOS工藝的

2010-04-07 14:25:58 16

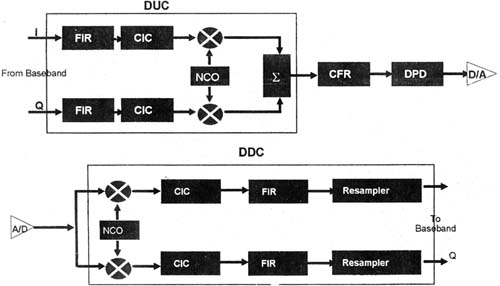

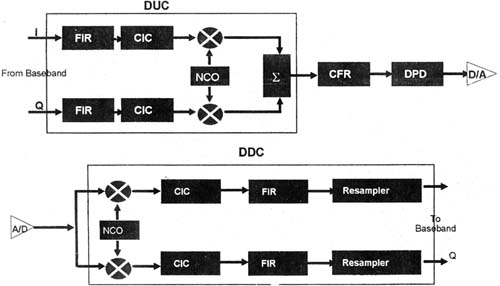

16 FPGA和DSP組合在無線基站中的應(yīng)用

在自動控制產(chǎn)品中,CPD+DSP+MCU的構(gòu)架是目前最為流行的成熟方案,而在通訊產(chǎn)品中,大量使用FPGA設(shè)計,合理使用FPGA

2009-10-12 11:20:11 975

975

基于DSP和FPGA的通用圖像處理平臺設(shè)計

摘要:設(shè)計一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺,運用FPGA實現(xiàn)微處理器接口設(shè)計,并對圖像數(shù)據(jù)進行簡單預(yù)處理,利用DSP

2010-02-01 11:10:21 1379

1379

安富利推出Xilinx Virtex-6 FPGA DSP開發(fā)工具套件安富利公司旗下運營機構(gòu)安富利電子元件宣布推出Xilinx Virtex -6 FPGA DSP開發(fā)工具套件。這套件是為DSP設(shè)計而打造,是Xilinx目標設(shè)計平

2010-04-24 09:56:31 1331

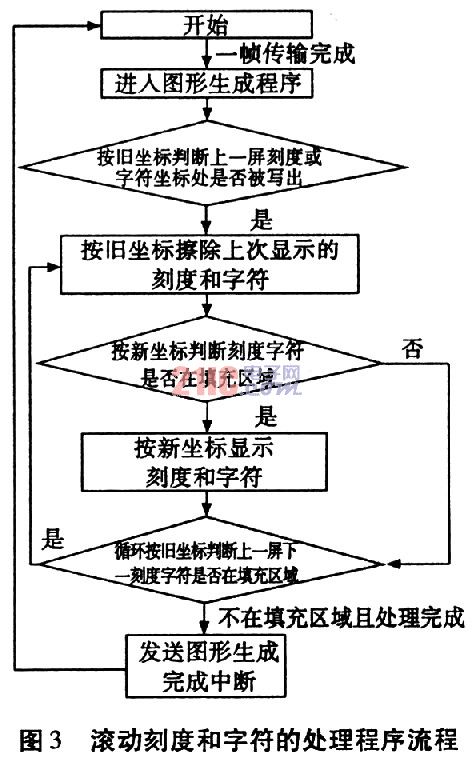

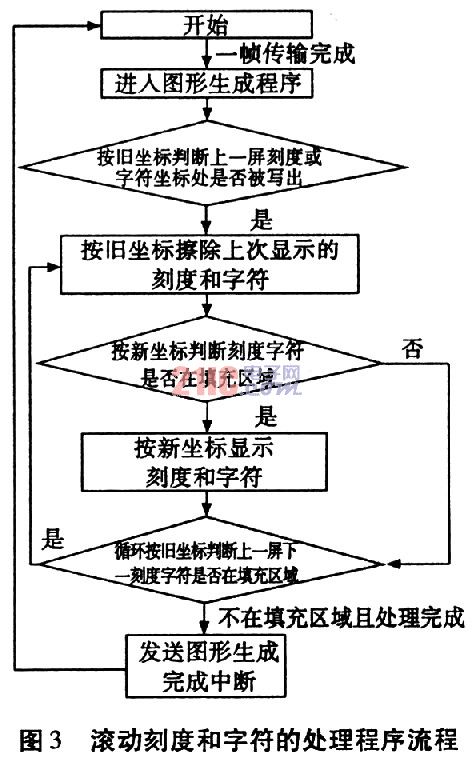

1331 本文設(shè)計了基于DSP與FPGA的系統(tǒng)結(jié)構(gòu),采用了軟硬件填充的圖形處理方法,先由DSP軟件完成圖形輪廓生成,然后FPGA硬件圖形處理器根據(jù)圖形輪廓完成耗時的圖形填充,使系統(tǒng)在實時性

2010-07-01 11:02:38 988

988

摘要:為了實現(xiàn)高速HDLC通訊協(xié)議,設(shè)計了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機;其中DSP用于實現(xiàn)數(shù)據(jù)控制,FPGA用于實現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 System Generator 工具由 MathWorks 與 Xilinx 合作開發(fā)而成,DSP 設(shè)計人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進行開發(fā)和仿真來完善 DSP 設(shè)計。 該工具為系統(tǒng)級 DSP 設(shè)計與 FPGA 硬件實現(xiàn)的融合起

2011-05-11 18:36:23 224

224 電子發(fā)燒友為您提供了ARM、DSP、FPGA三者的定義與其之間的區(qū)別!

2011-06-23 10:34:39 3665

3665 為滿足導(dǎo)航系統(tǒng)設(shè)計的小型化、實時性要求,本文提出了一種基于FPGA + DSP 的實現(xiàn)方案。該方案的設(shè)計思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 Alter FPGA的設(shè)計流程以及DSP設(shè)計.

2012-03-16 15:52:07 127

127 設(shè)計了一種基于DSP與FPGA的運動控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運動控制器與傳感器以及電機驅(qū)動器的接口電路。充分發(fā)揮了DSP強大的運算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 基于DSP和FPGA的SVPWM算法及其在變頻調(diào)速中的應(yīng)用。

2016-04-18 09:47:49 20

20 基于DSP與FPGA的運動控制器設(shè)計,下來看看。

2016-05-10 11:24:33 29

29 dsp fpga 電路 打標機上用的主板

2016-06-27 15:24:08 7

7 基于FPGA和DSP的圖像多功能卡的設(shè)計與實現(xiàn)

2016-09-22 12:32:08 28

28 基于DSP和FPGA的多頻聲納采集系統(tǒng)設(shè)計_劉寅

2017-03-19 11:45:23 0

0 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計_吳雷

2017-03-16 09:28:51 2

2 FPGA與ARM、DSP的區(qū)別

2017-03-15 08:00:00 9

9 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于FPGA的VME總線與DSP通信接口設(shè)計

2017-10-19 13:49:30 26

26 基于DSP與FPGA的便攜式超聲探傷儀

2017-10-19 14:21:56 7

7 DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計

2017-10-19 14:46:11 7

7 基于DSP的FPGA配置方法研究與實現(xiàn)

2017-10-19 16:15:19 36

36 摘要 利用異步FIFO實現(xiàn)FPGA與DSP進行數(shù)據(jù)通信的方案。FPGA在寫時鐘的控制下將數(shù)據(jù)寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數(shù)據(jù)讀入。文中給出了異步FIFO的實現(xiàn)

2017-10-30 11:48:44 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 10:48:09 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 13:58:57 7

7 的ASIC相比,它們提供的產(chǎn)品在多個方面都更勝一籌,例如具有更快的產(chǎn)品上市速度,以及更多的設(shè)計靈活性。然而截至目前,在與DSP的競爭中,人們卻普遍認為,FPGA在性價比方面的表現(xiàn)遠不如DSP。 不過,技術(shù)咨詢公司Berkeley Design Technology(BDTI)一項最新但是具有

2017-11-06 13:59:20 1

1 本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結(jié)構(gòu)特點與優(yōu)勢及DSP的基本結(jié)構(gòu)和特征,最后闡述了FPGA與DSP兩者之間的區(qū)別。

2018-05-31 09:51:25 35711

35711

FPGA是一種可編程的硅芯片,DSP是數(shù)字信號處理,當系統(tǒng)設(shè)計人員在項目的架構(gòu)設(shè)計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內(nèi)部資源、編程語言、功能多個角度解析兩者的不同。

2018-09-29 16:43:35 30755

30755 Q:FPGA設(shè)計與DSP設(shè)計相比,最大的不同之處在哪里?A:這個問題要從多個角度看。它們都用于某個功能的硬件

2019-05-03 10:59:00 4296

4296 相比GPU和GPP,FPGA在滿足深度學(xué)習(xí)的硬件需求上提供了具有吸引力的替代方案。憑借流水線并行計算的能力和高效的能耗,FPGA將在一般的深度學(xué)習(xí)應(yīng)用中展現(xiàn)GPU和GPP所沒有的獨特優(yōu)勢。

2019-10-18 15:48:14 1326

1326 型到大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號處理,如fft,通常一個復(fù)雜系統(tǒng)可以由單片機、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢和不足。 dsp通常用于運算密集型,fpga用于控制密集型,許多人都用dsp高算法,用fpga作外圍控制

2020-10-25 09:50:06 3085

3085 FPGA,arm,stm32,dsp特點對比

2021-11-19 13:21:02 24

24 廣州星嵌DSP/ARM/FPGA 選型手冊2023

2023-05-05 10:24:22 15

15 Q:FPGA設(shè)計與DSP設(shè)計相比,最大的不同之處在哪里?A:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現(xiàn),但是它們的側(cè)重點有所不同。這里涵蓋的說一下。1)內(nèi)部資源FPGA側(cè)重于設(shè)計具有

2022-01-19 09:53:10 620

620

fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設(shè)備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導(dǎo)致通訊數(shù)據(jù)的錯誤

2023-10-18 15:28:13 1060

1060

電子發(fā)燒友App

電子發(fā)燒友App

評論