為 FPGA 應(yīng)用設(shè)計(jì)優(yōu)秀電源管理解決方案不是一項(xiàng)簡(jiǎn)單的任務(wù),相關(guān)的技術(shù)討論有很多很多。今天小編要為大家分享的內(nèi)容『FPGA 的電源管理』主要有兩個(gè)目的——

??找到正確解決方案并選擇最合適的電源管理產(chǎn)品?

??如何優(yōu)化實(shí)際解決方案使其用于 FPGA

找到合適的電源解決方案

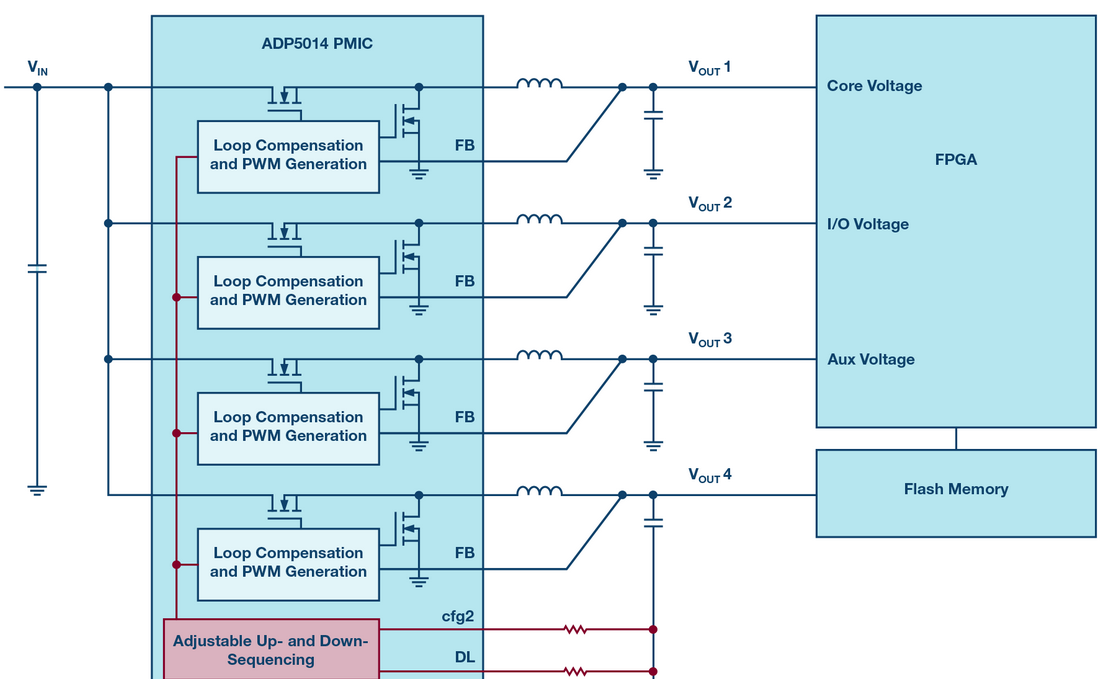

尋找為 FPGA 供電的最佳解決方案并不簡(jiǎn)單。許多供應(yīng)商以適合為? FPGA 供電的名義推銷某些產(chǎn)品。為 FPGA 供電的 DC-DC 轉(zhuǎn)換器選擇有何特定要求?其實(shí)并不多。一般而言,所有電源轉(zhuǎn)換器都可用來為 FPGA 供電。推薦某些產(chǎn)品通常是基于以下事實(shí):許多FPGA應(yīng)用需要多個(gè)電壓軌,例如用于 FPGA 內(nèi)核和 I/O,還可能需要額外的電 壓軌來用于 DDR 存儲(chǔ)器。將多個(gè)DC-DC 轉(zhuǎn)換器全部集成到單個(gè)穩(wěn)壓器芯片中的 PMIC(電源管理集成電路)常常是首選。

一種為特定 FPGA 尋找優(yōu)秀供電解決方案的流行方法是使用許多 FPGA 供應(yīng)商都提供的已有電源管理參考設(shè)計(jì)。這對(duì)于優(yōu)化設(shè)計(jì)來說是一個(gè)很好的入門方式。但此類設(shè)計(jì)往往需要修改,因?yàn)?

FPGA 系統(tǒng)通常需要額外的電壓軌和負(fù)載,這些也需要供電;

在參考設(shè)計(jì)上增加一些東西常常也是必要的;

FPGA 的輸入電源不是固定的,輸入電壓在很大程度上取決于實(shí)際的邏輯電平以及 FPGA 所實(shí)現(xiàn)的設(shè)計(jì)。

完成對(duì)電源管理參考設(shè)計(jì)的修改之后,它看起來將與最初的參考設(shè)計(jì)不同。可能有人會(huì)辯稱,最好的解決方案是根本不用電源管理參考設(shè)計(jì),而是直接將所需的電壓軌和電流輸入到電源管理選型與優(yōu)化工具中,例如 ADI 公司的 LTpowerCAD 等。

?

圖1. 通過 LTpowerCAD 工具選擇合適的 DC-DC 轉(zhuǎn)換器來為 FPGA 供電。

LTpowerCAD 可用來為各個(gè)電壓軌提供電源解決方案。它還提供一系列參考設(shè)計(jì),以讓設(shè)計(jì)人員快速入門。LTpowerCAD 可以從 ADI 公司網(wǎng)站免費(fèi)下載。?下載鏈接:http://www.analog.com/cn/design-center/ltpowercad.html

如何優(yōu)化實(shí)際解決方 案以用于FPGA

一旦選擇了電源架構(gòu)和各個(gè)電壓轉(zhuǎn)換器,就需要選擇合適的無源元件來設(shè)計(jì)電源。做這件事時(shí),需要牢記?FPGA 的特殊負(fù)載要求——

各項(xiàng)電流需求 ?

電壓軌時(shí)序控制?

電壓軌單調(diào)上升?

快速電源瞬變?

電壓精度

FPGA?輸入電容

各項(xiàng)電流需求

FPGA 的實(shí)際電流消耗在很大程度上取決于使用情況。不同的時(shí)鐘和不同的FPGA 內(nèi)容需要不同的功率。因此,在 FPGA 系統(tǒng)的設(shè)計(jì)過程中,典型 FPGA 設(shè)計(jì)的最終電源規(guī)格必然會(huì)發(fā)生變化。FPGA 制造商提供的功率估算工具有助于計(jì)算解決方案所需的功率等級(jí)。在構(gòu)建實(shí)際硬件之前,獲得這些信息會(huì)非常有用。但是,為了利用此類功率估算工具獲得有意義的結(jié)果,F(xiàn)PGA 的設(shè)計(jì)必須最終確定,或者至少接近最終完成。

通常情況下,工程師設(shè)計(jì)電源時(shí)考慮的是最大 FPGA 電流。如果最終發(fā)現(xiàn)實(shí)際 FPGA 設(shè)計(jì)需要的功率更少,設(shè)計(jì)人員就會(huì)縮減電源。

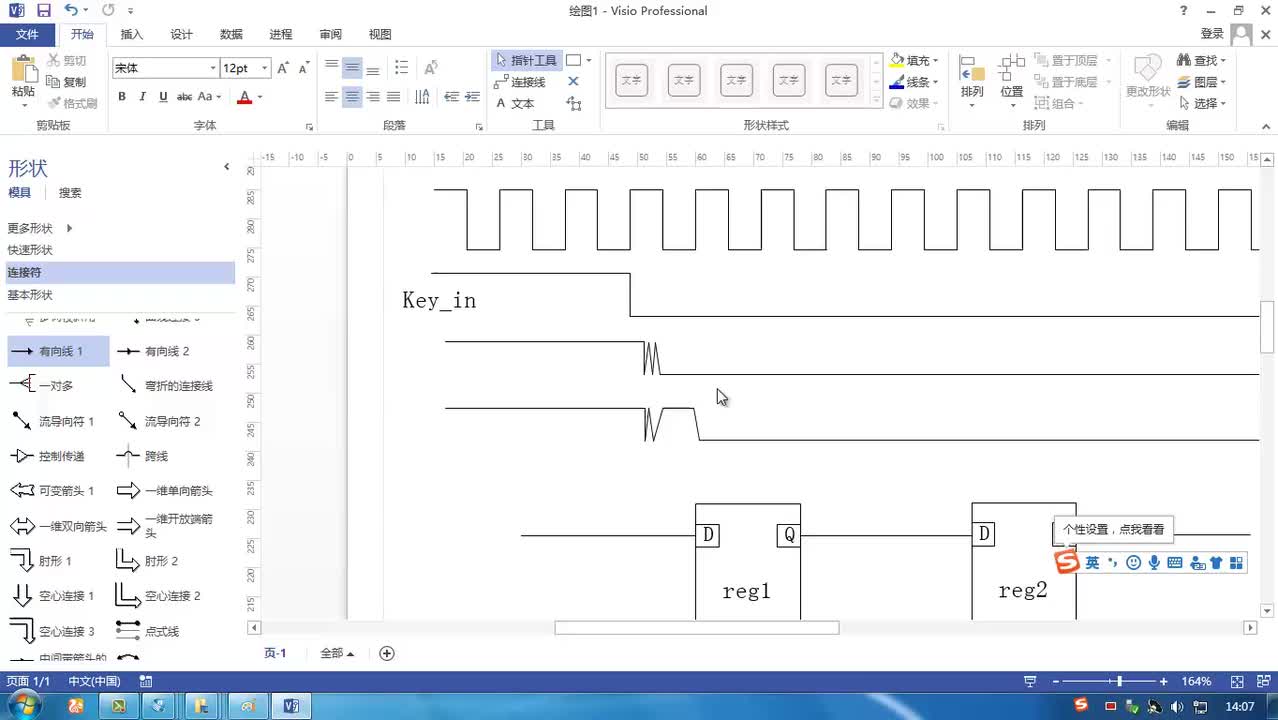

電壓軌時(shí)序控制

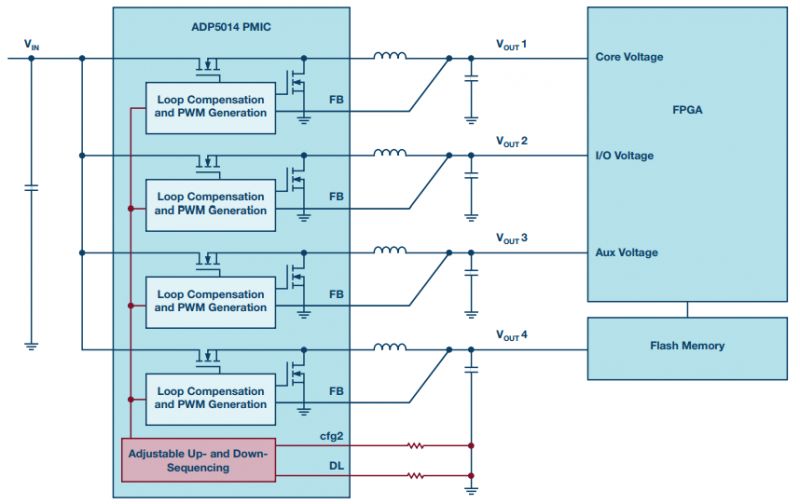

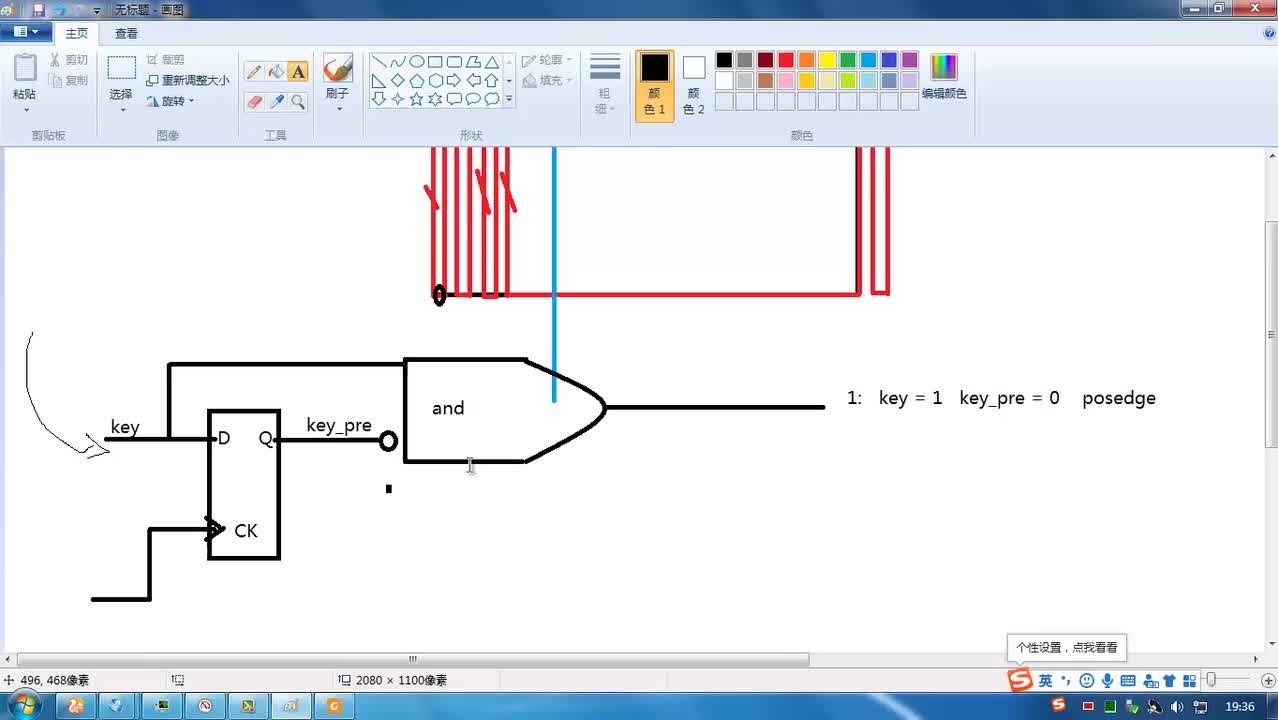

許多 FPGA 要求不同電源電壓軌以特定順序上電。內(nèi)核電壓的供應(yīng)往往需要早于 I/O 電壓的供應(yīng),否則一些 FPGA 會(huì)被損壞。為了避免這種情況,電源需要按正確的順序上電。使用標(biāo)準(zhǔn) DC-DC 轉(zhuǎn)換器上的使能引腳,可以輕松實(shí)現(xiàn)簡(jiǎn)單的上電時(shí)序控制。然而,器件關(guān)斷通常也需要時(shí)序控制。僅執(zhí)行使能引腳時(shí)序控制,很難取得良好的結(jié)果。更好的解決辦法是使用具有高級(jí)集成時(shí)序控制功能的 PMIC,例如 ADP5014。圖2中用紅色表示的特殊電路模塊支持調(diào)整上電和關(guān)斷時(shí)序。?

圖2. ADP5014 PMIC 集成了對(duì)靈活控制上電/關(guān)斷時(shí)序的支持。

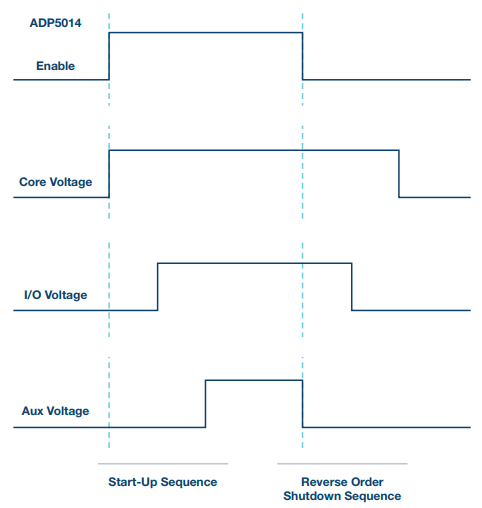

圖 3 顯示了利用此器件實(shí)現(xiàn)的時(shí)序控制。通過 ADP5014 上的延遲 (DL) 引腳可以輕松調(diào)整上電和關(guān)斷時(shí)序的時(shí)間延遲。

圖3. 多個(gè)FPGA電源電壓的啟動(dòng)和關(guān)斷順序。

如果使用多個(gè)單獨(dú)的電源,增加時(shí)序控制芯片便可實(shí)現(xiàn)所需的上電/關(guān)斷順序。一個(gè)例子是 LTC2924,它既能控制 DC-DC 轉(zhuǎn)換器的使能引腳來打開和關(guān)閉電源,也能驅(qū)動(dòng)高端 N 溝道 MOSFET 來將 FPGA 與某個(gè)電壓軌連接和斷開。

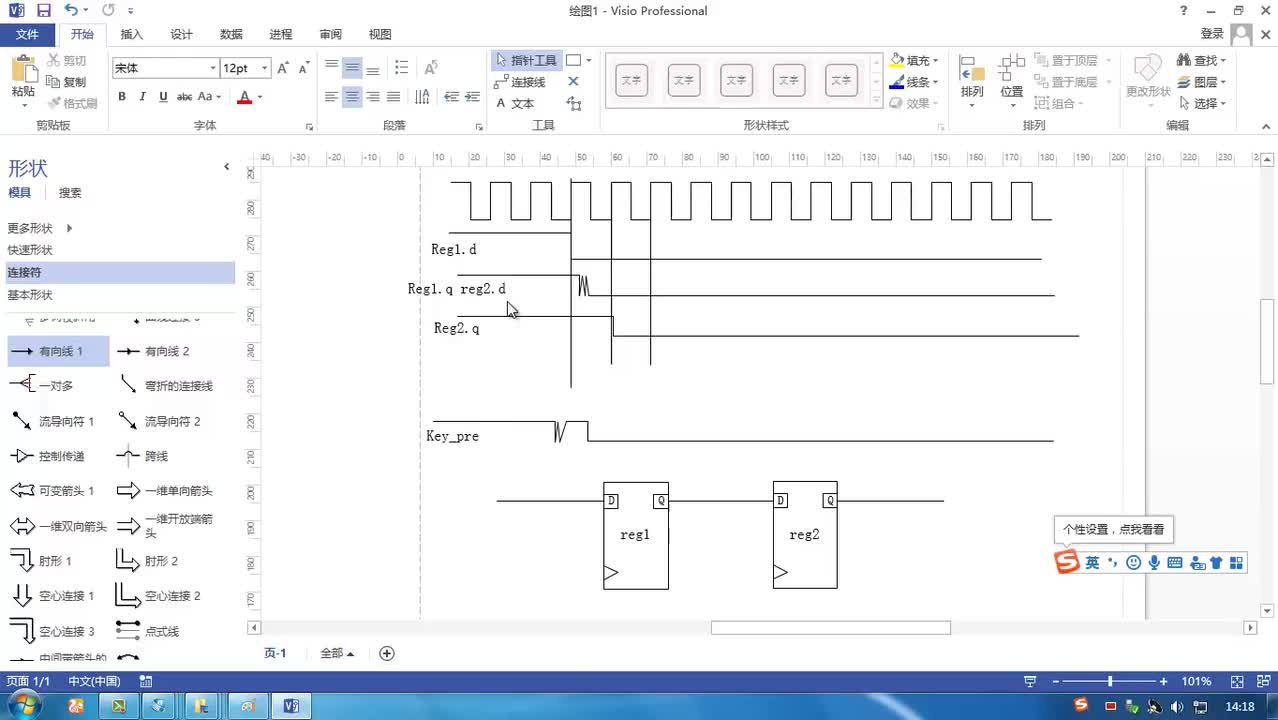

電壓軌單調(diào)上升

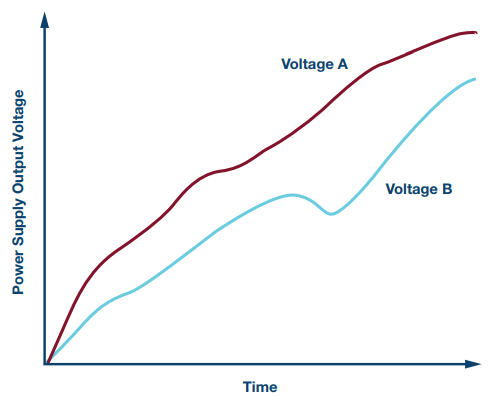

除了電壓時(shí)序之外,啟動(dòng)過程中還可能要求電壓?jiǎn)握{(diào)上升。這意味著電壓僅線性上升,如圖 4 中的電壓 A 所示。此圖中的電壓 B 是電壓非單調(diào)上升的例子。在啟動(dòng)過程中,當(dāng)電壓上升到一定電平時(shí)負(fù)載開始拉大電流,就會(huì)發(fā)生這種情況。防止這種情況的一種辦法是延長(zhǎng)電源的軟啟動(dòng)時(shí)間,并選擇能夠快速提供大量電流的電源轉(zhuǎn)換器。

圖4. 電壓A單調(diào)上升,電壓B非單調(diào)上升。

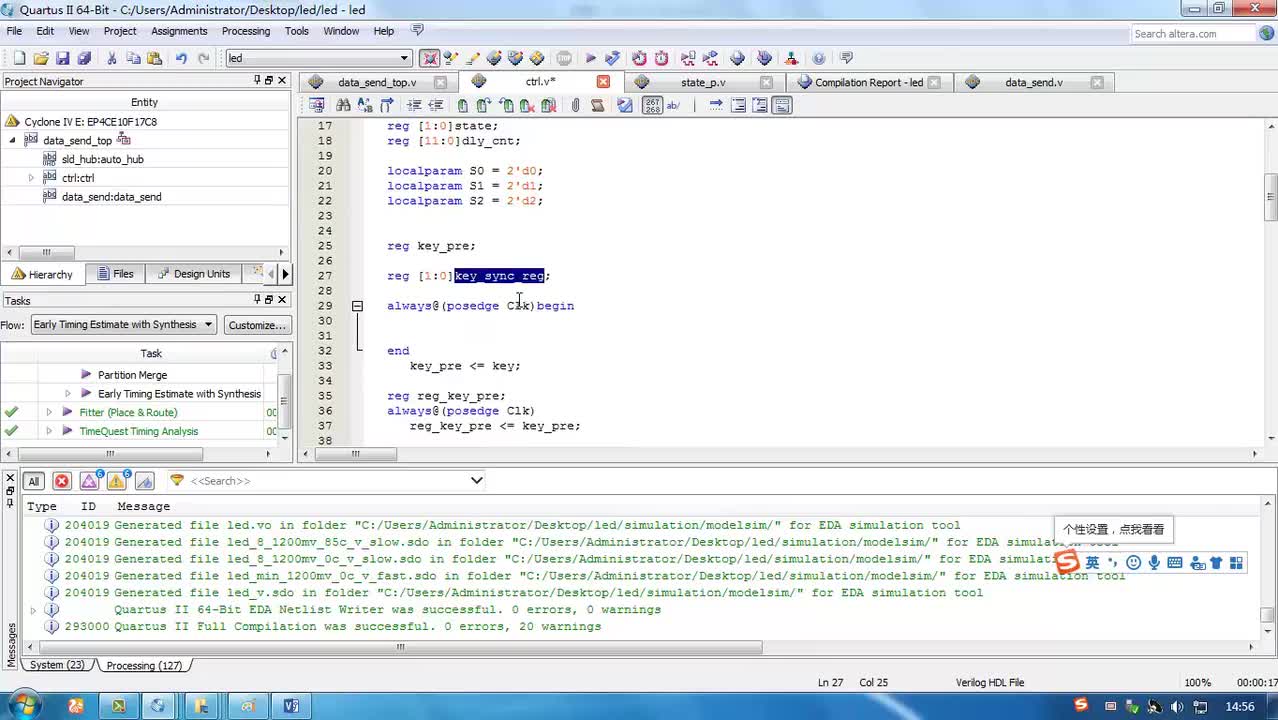

快速電源瞬變

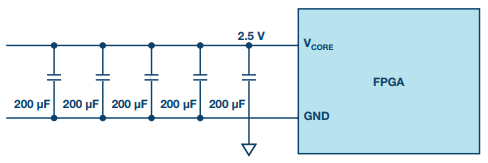

FPGA 的另一個(gè)特點(diǎn)是它會(huì)非常迅速地開始抽取大量電流。這會(huì)在電源上造成很高的負(fù)載瞬變。出于這個(gè)原因,許多 FPGA 需要大量的輸入電壓去耦。陶瓷電容非常靠近地用在器件的 VCORE 和 GND 引腳之間。高達(dá) 1 mF 的值非常常見。如此高電容有助于降低對(duì)電源提供非常高峰值電流的需求。但是,許多開關(guān)穩(wěn)壓器和 LDO 規(guī)定了最大輸出電容。FPGA 的輸入電容要求可能超過電源允 許的最大輸出電容。?

電源不喜歡非常大的輸出電容,原因有兩點(diǎn)——

在啟動(dòng)期間,開關(guān)穩(wěn)壓器的輸出電容看來像是短路的。對(duì)此問題有一個(gè)解決辦法。較長(zhǎng)的軟啟動(dòng)時(shí)間可以讓大電容組上的電壓穩(wěn)定地升高,電源不會(huì)進(jìn)入短 路限流模式。

圖5. 很多FPGA的輸入電容要求。

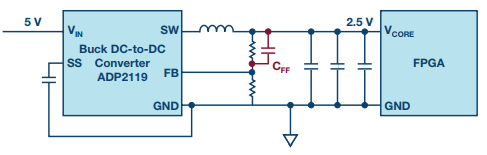

該電容值會(huì)成為調(diào)節(jié)環(huán)路的一部分。集成環(huán)路補(bǔ)償?shù)霓D(zhuǎn)換器不允許輸出電容過大,以防止穩(wěn)壓器的環(huán)路不穩(wěn)定。在高端反饋電阻上使用前饋電容常常可以影響控制環(huán)路,如圖6所示。

圖6. 當(dāng)沒有環(huán)路補(bǔ)償引腳可用時(shí),利用前饋電容可以調(diào)節(jié)控制環(huán)路。

針對(duì)電源的負(fù)載瞬變和啟動(dòng)行為,開發(fā)工具鏈(包括 LTpowerCAD,尤其是 LTspice)是非常有幫助的。該工具可以很好的建模和仿真,從而有效實(shí)現(xiàn) FPGA 的大輸入電容與電源的輸出電容的去耦。?圖 6?就展示了這一概念。

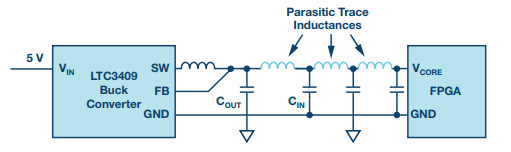

雖然 POL(負(fù)載端)電源的位置往往靠近負(fù)載,但在電源和 FPGA 輸入電容之間常常存在一些 PCB 走線。當(dāng)電路板上有多個(gè)彼此相鄰的 FPGA 輸入電容時(shí),離電源最遠(yuǎn)的那些電容對(duì)電源傳遞函數(shù)的影響較小,因?yàn)樗鼈冎g不僅存在一些電阻, 還存在寄生走線電感。這些寄生電感允許 FPGA 的輸入電容大于電源輸出電容的最大限值,即使所有電容都連接到電路板上的同 一節(jié)點(diǎn)也無妨。在 LTspice 中,可以將寄生走線電感添加到原理圖中,并且可以模擬這些影響。當(dāng)電路建模中包含足夠的寄生元件時(shí),仿真結(jié)果接近實(shí)際結(jié)果。

圖7. 電源輸出電容與FPGA輸入電容之間的寄生去耦。

電壓精度

FPGA電源的電壓精度通常要求非常高。3%的變化容差帶是相當(dāng) 常見的。例如,為使0.85 V的Stratix V內(nèi)核電壓軌保持在3%的電壓精度窗口內(nèi),要求全部容差帶僅為25.5 mV。這個(gè)小窗口包括 負(fù)載瞬變后的電壓變化以及直流精度。同樣,對(duì)于此類嚴(yán)格要 求,包括LTpowerCAD和LTspice在內(nèi)的可用電源工具鏈在電源設(shè)計(jì) 過程中非常重要。

FPGA 輸入電容

為了快速提供大電流,F(xiàn)PGA?的輸入電容通常選擇陶瓷電容。此類電容很適合這種用途,但需要小心選擇,使其真實(shí)電容值不隨直流偏置電壓而下降。一些陶瓷電容,尤其是 Y5U 型,當(dāng)直流偏置電壓接近其最大額定直流電壓 時(shí),其真實(shí)電容值會(huì)降低到只有標(biāo)稱值的20%。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論