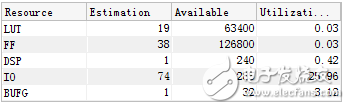

對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 8153

8153 本文描述了復位的定義,分類及不同復位設計的影響,并討論了針對FPGA和CPLD的內部自復位方案。

2016-07-11 14:33:49 6228

6228

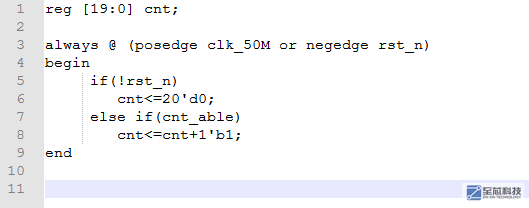

大家好,博主最近有事忙了幾天,沒有更新,今天正式回來了。那么又到了每日學習的時間了,今天咱們來聊一聊 簡談FPGA的上電復位,歡迎大家一起交流學習。 在基于verilog的FPGA設計中,我們常常

2018-06-18 19:24:11 19894

19894

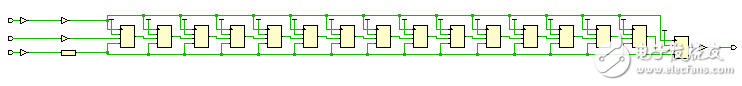

隨著FPGA設計越來越復雜,芯片內部的時鐘域也越來越多,使全局復位已不能夠適應FPGA設計的需求,更多的設計趨向于使用局部的復位。本節將會從FPGA內部復位“樹”的結構來分析復位的結構。 我們的復位

2019-02-20 10:40:44 1068

1068

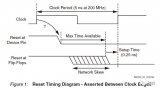

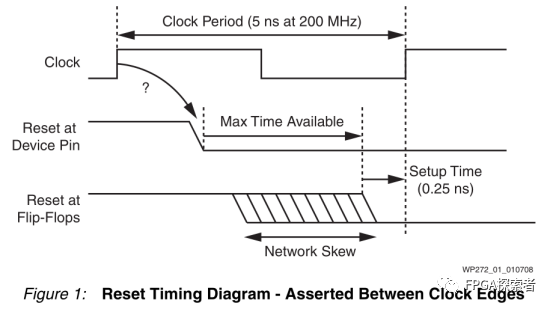

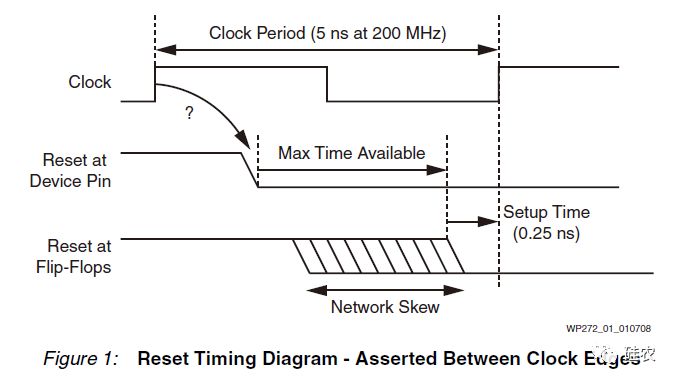

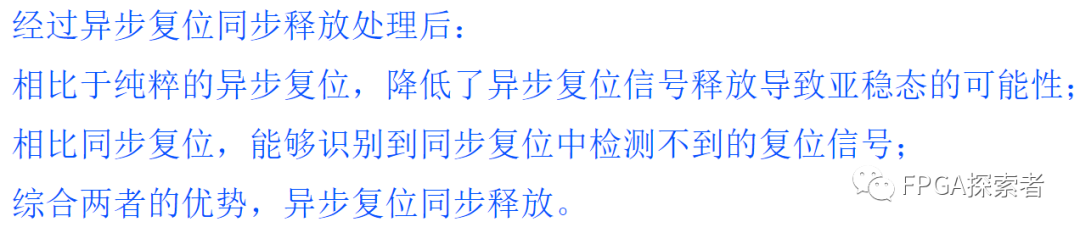

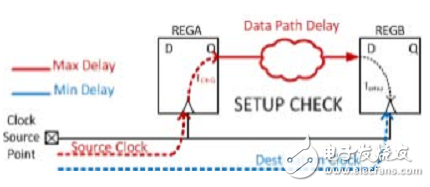

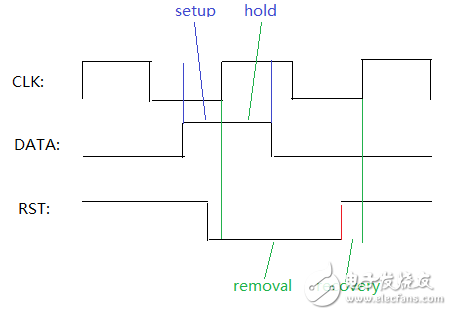

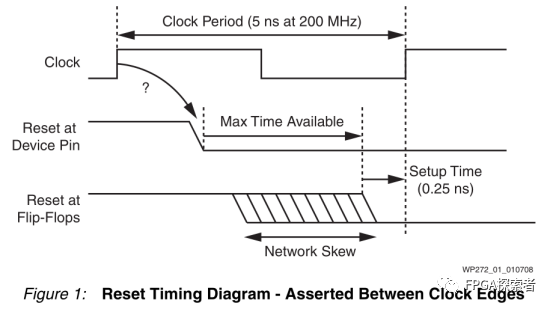

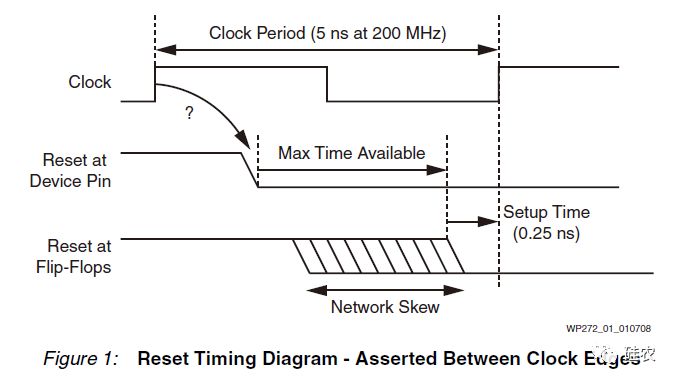

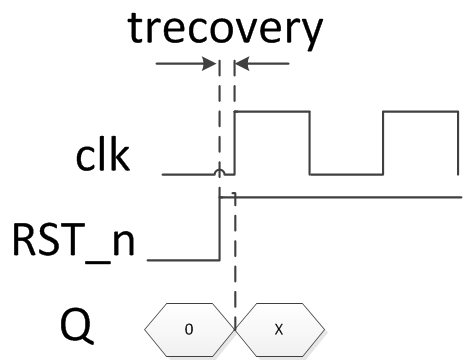

異步復位信號a是異步復位信號源,異步復位信號b、c、d是到達觸發器的異步信號。我們可以看到,b信號是在本周期就撤離了復位;c信號則由于復位恢復時間不滿足,則可能導致觸發器輸出亞穩態;而d信號則由于延時太長(但是滿足了復位去除時間),在下一個周期才撤離復位。

2020-06-26 05:36:00 22799

22799

在復位電路中,由于復位信號是異步的,因此,有些設計采用同步復位電路進行復位,并且絕大多數資料對于同步復位電路都認為不會發生亞穩態,其實不然,同步電路也會發生亞穩態,只是幾率小于異步復位電路。

2020-06-26 16:37:00 1232

1232

最近看advanced fpga 以及fpga設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-09-01 15:37:07 1461

1461

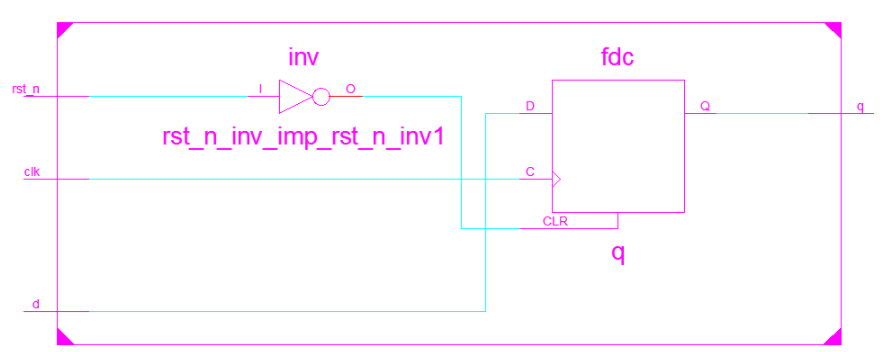

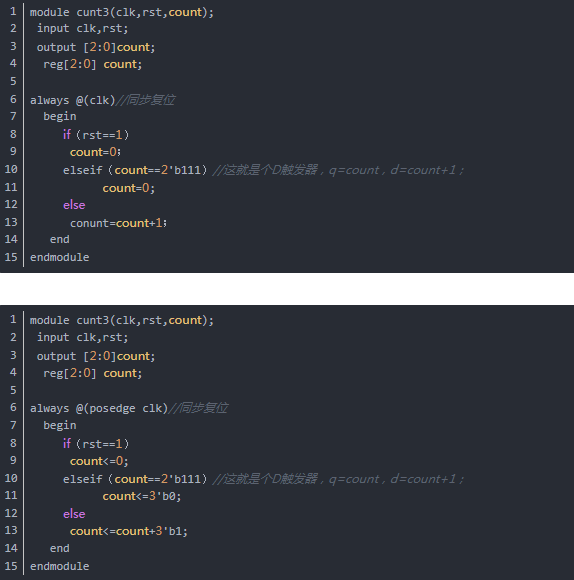

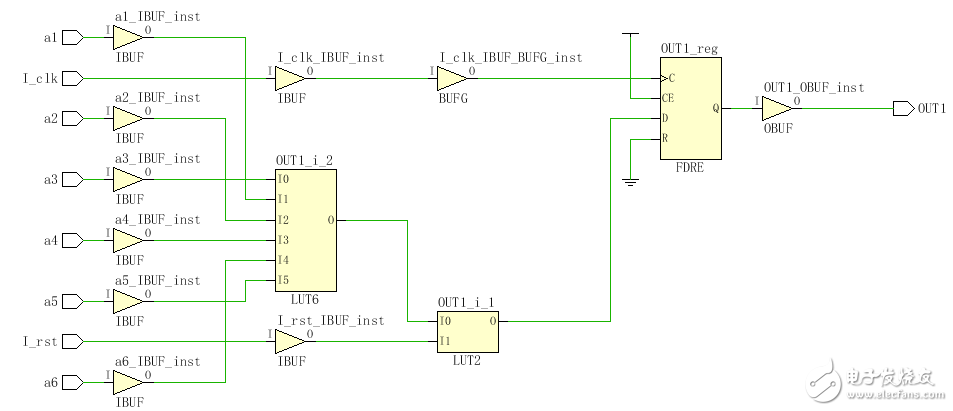

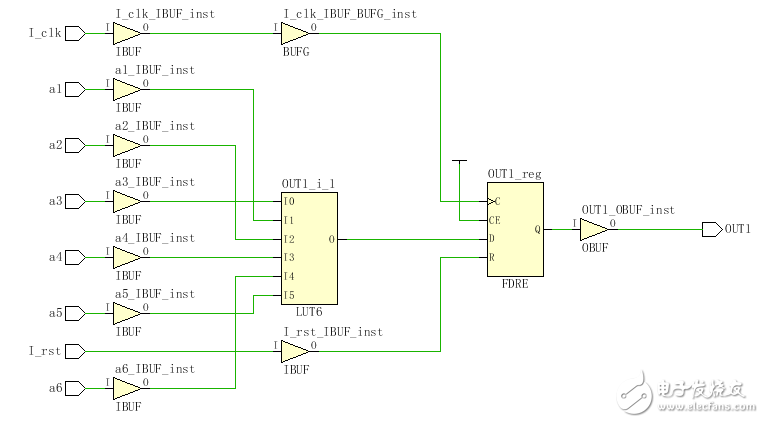

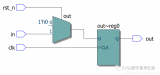

根據代碼,容易推斷得出這是一個高電平觸發、異步復位的觸發器(或者叫異步置位),這也與前面的內容相符合(高電平觸發復位,所以不用加反相器)。

2020-11-14 11:32:00 9350

9350

: ① 首先,上電后肯定是要復位一下,不然仿真時會出現沒有初值的情況; ② 最好有個復位的按鍵,在調試時按一下復位鍵就可以全局復位了; ③ 也許是同步復位,也許是異步復位,不同的工程師可能有不同的方案

2020-11-18 17:32:38 3110

3110 內都是將復位信號作為一個I/O口,通過撥碼開關硬件復位。后來也看了一些書籍,采用異步復位同步釋放,對自己設計的改進。 不過自從我研讀了Xilinx的White Paper后,讓我對復位有了更新的認識

2020-12-25 12:08:10 2303

2303

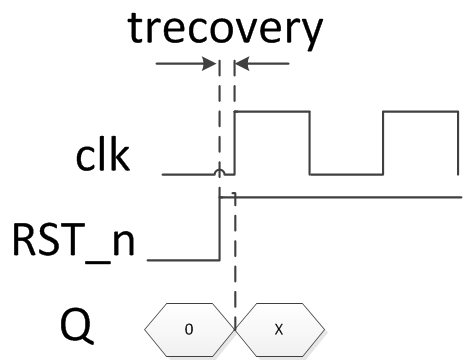

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復位電路:同步復位、異步復位和異步復位同步釋放,以及相應的Verilog代碼示例。

2023-05-14 14:44:49 1679

1679

在FPGA設計中,當復位整個系統或功能模塊時,需要將先關寄存器被清零或者賦初值,以保證整個系統或功能運行正常。在大部分的設計中,我們經常用“同步復位”或“異步復位”直接將所有的寄存器全部復位,這部分可能大家都習以為常。但實際上,是否需要每個寄存器都進行復位呢?這是一個值得探討的問題。

2023-05-14 14:49:19 1701

1701

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2023-06-21 09:59:15 647

647

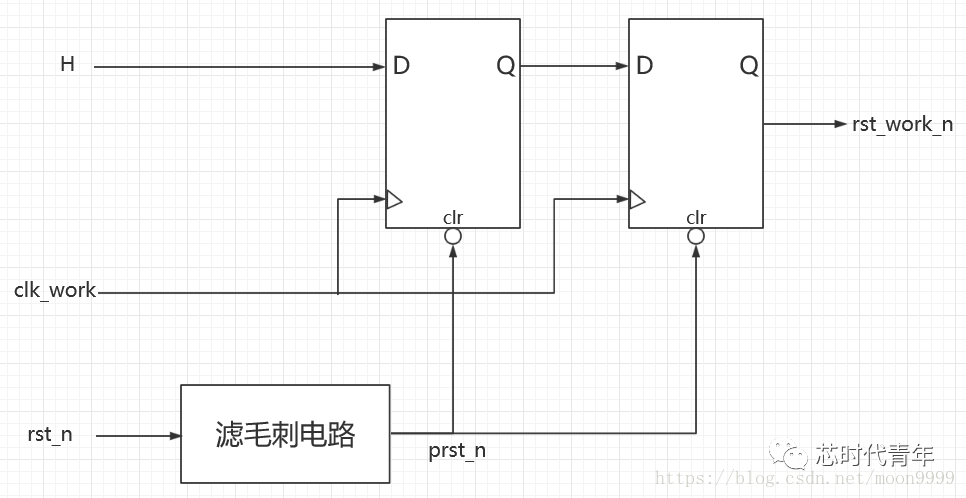

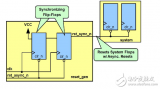

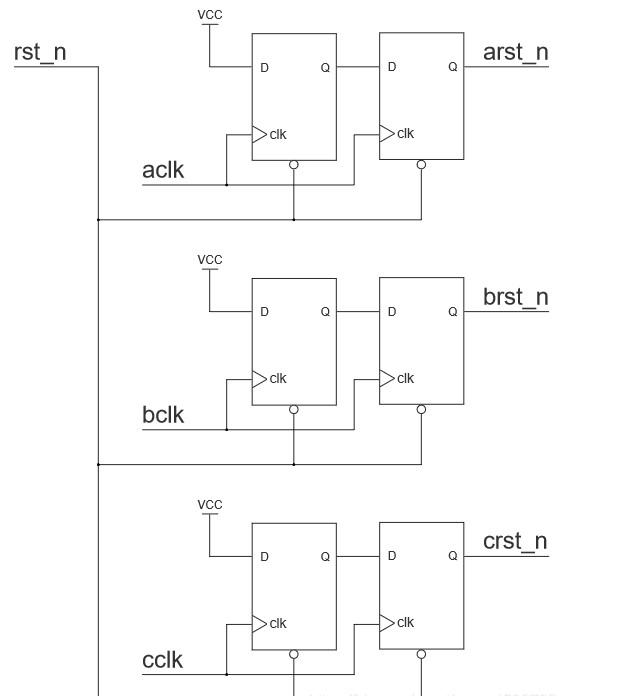

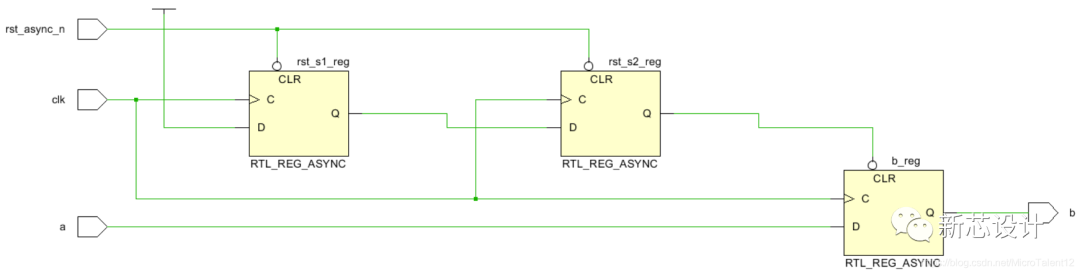

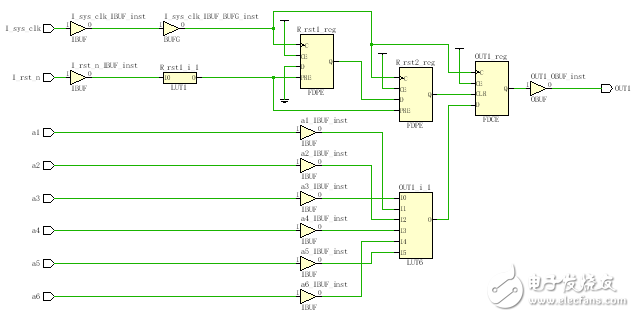

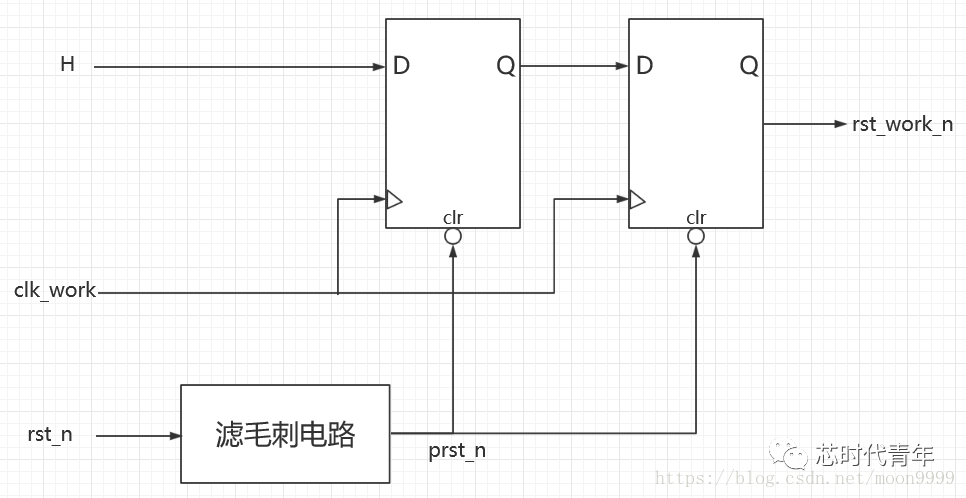

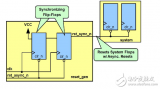

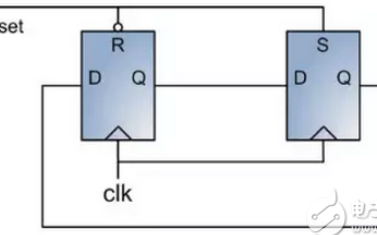

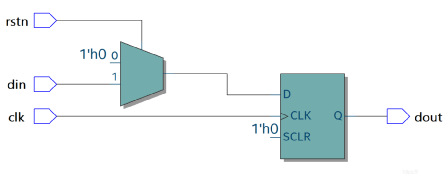

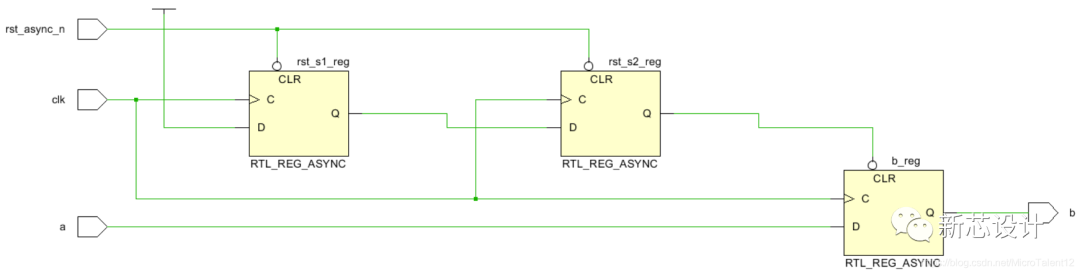

對于從FPGA外部進來的信號,我們通常采用“異步復位同步釋放的策略”,具體電路如下圖所示。

2023-07-20 09:04:21 1219

1219

在SOC設計中,復位電路是一個關鍵部分,它確保了芯片中各個模塊在初始化和運行時能夠處于一致的狀態。

2023-08-27 14:47:16 981

981 復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

2023-09-13 16:26:49 888

888

復位消抖之后的下一件事,[異步復位]()同步撤離。這句話什么意思呢?

2023-12-04 13:57:39 1221

1221

信號上沒有上拉電阻,容易受到干擾而產生毛刺,這對異步復位是相當有害的。其次,我在FPGA內部對復位的處理過于簡單。 今天在網上看了一些資料,很多是關于同步和異步復位的優缺點比較。由于我在FPGA內部用

2011-11-04 14:26:17

需要注意以下幾個要點:●盡可能使用FPGA的專用復位引腳。(特權同學,版權所有)●上電復位時間的長短需要做好考量。(特權同學,版權所有)●確保系統正常運行過程中復位信號不會誤動作。(特權同學,版權所有) Xilinx FPGA入門連載

2019-04-12 06:35:31

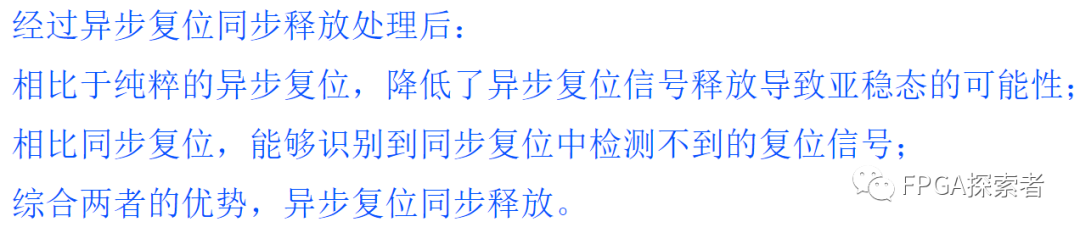

和removal時序檢查;異步復位同步撤離(推薦使用) 優點:能避免純異步或純同步復位的潛在問題。它是FPGA設計中最受歡迎的復位,Altera建議使用這種復位方法。這種復位在使用前需要同步到各個使用時

2014-03-20 21:57:25

。在這里提出一個區域化復位的方案,如圖1所示。外部的異步復位信號被二級寄存器同步化之后,復制不同的復位寄存器連到不同的模塊來作為復位控制。如果單個模塊的復位扇出太大的話,還可以在模塊內部復制復位寄存器

2019-05-17 08:00:00

復位的目的復位的基本目的是使器件進入到可以穩定工作的確定狀態,這避免了器件在上電后進入到隨機狀態導致跑飛了。在實際設計過程中,設計者必須選擇最適合于設計本身的復位方式。耳熟能詳的是同步復位和異步復位

2020-01-08 06:00:00

下面對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用

2021-06-30 07:00:00

可能就應盡量在設計項目中采用全局時鐘。 CPLD/FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。 在許多應用中只將異步信號同步化還是

2012-03-05 14:29:00

%的同步時序電路,有利于時序分析。1)設計相對簡單。2)因為大多數目標器件庫的dff都有異步復位端口,因此采用異步復位可以節省資源。3)異步復位信號識別方便,而且可以很方便的使用FPGA的全局復位端口

2011-11-14 16:03:09

在網上了解到fpga的同步復位和異步復位都會存在不足,因此有人提出異步復位,同步釋放的方法來消除兩者的不足。對此也提出一些疑問,還請大家能指導一下:1、同步復位,同步復位的缺點包括需要復位信號的寬度

2014-04-16 22:17:53

異步復位,同步釋放的理解目錄目錄同步復位和異步復位異步復位 同步復位 那么同步復位和異步復位到底孰優孰劣呢?異步復位、同步釋放問題1 問題2 問題3 問題4 問題5參考資料同步復位和異步復位異步復位

2022-01-17 07:01:53

[table][tr][td] 無論同步還是異步復位,在對觸發器時序進行分析的時候,都要考慮復位端與時鐘的相位關系。對于同步復位,復位信號可以理解為一個普通的數據信號,它只有在時鐘的跳變沿才會其作用

2018-07-03 02:49:26

本帖最后由 hxing 于 2016-5-7 14:47 編輯

最近看到一篇關于 同步復位和異步復位的比較 的帖子,感覺講的很清晰,遂轉載了無論同步還是異步復位,在對觸發器時序進行分析的時候

2016-05-05 23:11:23

復位中的同步復位和異步復位問題:恢復時間是指異步復位信號釋放和時鐘上升沿的最小距離,在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個異步控制

2022-01-17 06:08:11

。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何其它輸入引腳類似,對 FPGA 來說往往是異步的。設計人員可以使用這個信號在 FPGA 內部對自己的設計進行異步或者同步復位。常見的復位方式有三種1、硬件開關:復位信號接一個撥碼開關或按鍵,.

2021-11-11 06:06:08

fpga 的 異步復位同步釋放代碼如下module asy_rst(clk,rst_n,asy_rst);input clk;input rst_n;output asy_rst;reg

2013-05-28 13:02:44

沒有被時鐘采到,則可能會導致不能有效復位。那么有沒有什么好辦法呢?當然有啦,下面就要介紹在實際設計中常用的復位方案,即同步確立,異步釋放方案:這種方案確立時是瞬間同時對所有寄存器復位的,而釋放時則要

2012-12-05 17:09:26

FPGA 異步reset 問題:⑴ 閱讀下面文章,寫出關鍵點,并給出自己的理解;⑵ 查看下面代碼,結合文章,指出代碼所表達的涵義。文章: 代碼:1. 文章主要講復位信號最好用同步復位,否則

2012-03-14 15:10:21

本帖最后由 何立立 于 2015-6-7 20:59 編輯

最近遇到FPGA復位信號的問題困擾很久,查了相關資料:FPGA設計是基于大量flip-flop或者寄存器的同步系統設計,所以所有這些

2015-06-07 20:39:43

復位還是應該使用異步復位。實際上,無論是同步復位還是異步復位都有各自的優缺點。在這里夢翼師兄和大家一起學習另外一種復位信號的處理方式-異步復位同步釋放。 基本概念FPGA設計中常見的復位方式有同步復位

2019-12-04 10:18:49

今天給大俠帶來如何區分同步復位和異步復位?,話不多說,上貨。

如何區分同步復位和異步復位?可以理解為同步復位是作用于狀態,然后通過狀態來驅動電路復位的嗎(這樣理解的話,復位鍵作為激勵拉高到響應

2023-05-22 17:33:12

問:如何區分同步復位和異步復位?可以理解為同步復位是作用于狀態,然后通過狀態來驅動電路復位的嗎(這樣理解的話,復位鍵作為激勵拉高到響應拉高,是不是最少要2拍啊)?以上問題可以理解為:1. 何時采用

2018-04-24 13:23:59

` ?大家好,談到同步復位和異步復位,那咱們就不得不來聊一聊復位這個詞了。在數字邏輯電路設計中,電路通過復位來啟動,復位猶如數字電路的“起搏器”。那在設計中,主要會出現以下三種類型的,一是無復位

2018-01-30 11:01:58

請問異步復位和同步復位是否可以共存?有什么影響?

2014-10-08 17:50:43

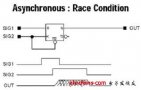

異步復位相比同步復位: 1. 通常情況下(已知復位信號與時鐘的關系),最大的缺點在于異步復位導致設計變成了異步時序電路,如果復位信號出現毛刺,將會導致觸發器的誤動作,影響

2012-04-20 14:41:48 2694

2694

前兩天和師兄討論了一下design rule其中提到了同步異步復位的比較這個常見問題,據說也是IC公司經常問到的一面試題。

2017-02-11 05:56:11 1809

1809 在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 876

876

顧名思義,同步復位就是指復位信號只有在時鐘上升沿到來時,才能有效。否則,無法完成對系統的復位工作。

2017-02-11 12:40:11 7563

7563

引腳類似,對 FPGA 來說往往是異步的。設計人員可以使用這個信號在 FPGA 內部對自己的設計進行異步或者同步復位。

2017-11-22 17:03:45 5125

5125

異步復位原理:異步復位只要有復位信號系統馬上復位,因此異步復位抗干擾能力差,有些噪聲也能使系統復位,因此有時候顯得不夠穩定,要想設計一個好的復位最好使用異步復位同步釋放。

2017-11-30 08:45:46 94797

94797

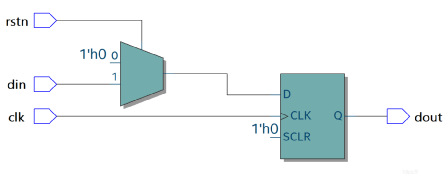

是指復位信號是異步有效的,即復位的發生與clk無關。后半句“同步釋放”是指復位信號的撤除也與clk無關,但是復位信號是在下一個clk來到后起的作用(釋放)。

2017-11-30 08:58:14 23613

23613

在帶有復位端的D觸發器中,當reset信號“復位”有效時,它可以直接驅動最后一級的與非門,令Q端“異步”置位為“1”or“0”。這就是異步復位。當這個復位信號release時,Q的輸出由前一級的內部輸出決定。

2017-11-30 09:15:37 10572

10572

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1989

1989 大家好,談到同步復位和異步復位,那咱們就不得不來聊一聊復位這個詞了。在數字邏輯電路設計中,電路通過復位來啟動,復位猶如數字電路的起搏器。那在設計中,主要會出現以下三種類型的,一是無復位:天生就強壯

2018-05-17 09:30:28 12544

12544

問:如何區分同步復位和異步復位?可以理解為同步復位是作用于狀態,然后通過狀態來驅動電路復位的嗎(這樣理解的話,復位鍵作為激勵拉高到響應拉高,是不是最少要2拍啊)? 以上問題可以理解為:1. 何時采用

2018-06-11 15:15:11 6394

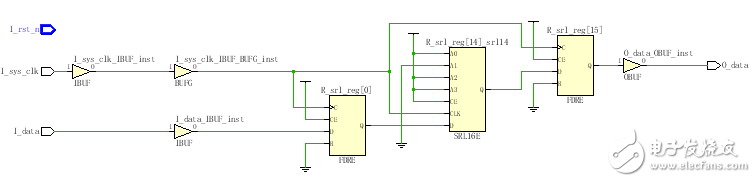

6394 在實際設計中,由于外部阻容復位時間短,可能無法使FPGA內部復位到理想的狀態,所以今天介紹一下網上流行的復位邏輯。

2018-08-07 09:17:18 10969

10969 FPGA的可靠復位是保證系統能夠正常工作的必要條件,本文對FPGA設計中常用的復位設計方法進行了分類、分析和比較,并針對各種復位方式的特點,提出了如何提高復位設計可靠性的方法。

2018-08-08 15:14:23 10154

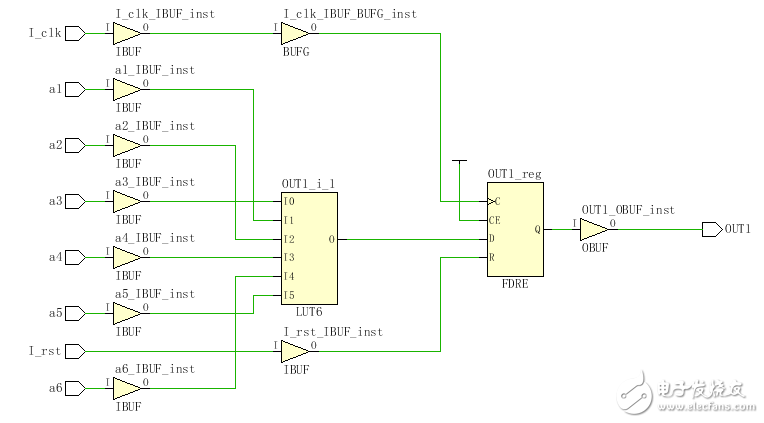

10154 通常情況下,復位信號的異步釋放,沒有辦法保證所有的觸發器都能在同一時間內釋放。觸發器在A時刻接收到復位信號釋放是最穩定的,在下一個時鐘沿來臨被激活,但是如果在C時刻接收到復位信號釋放無法被激活,在B時刻收到復位信號釋放,則會引起亞穩態。

2018-11-19 10:34:01 9401

9401

異步復位是不受時鐘影響的,在一個芯片系統初始化(或者說上電)的時候需要這么一個全局的信號來對整個芯片進行整體的復位,到一個初始的確定狀態。

2019-01-04 08:59:20 6296

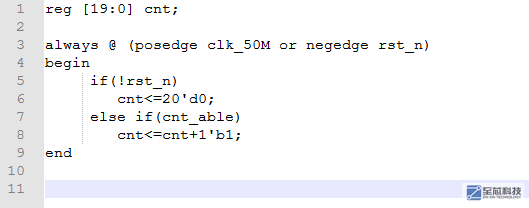

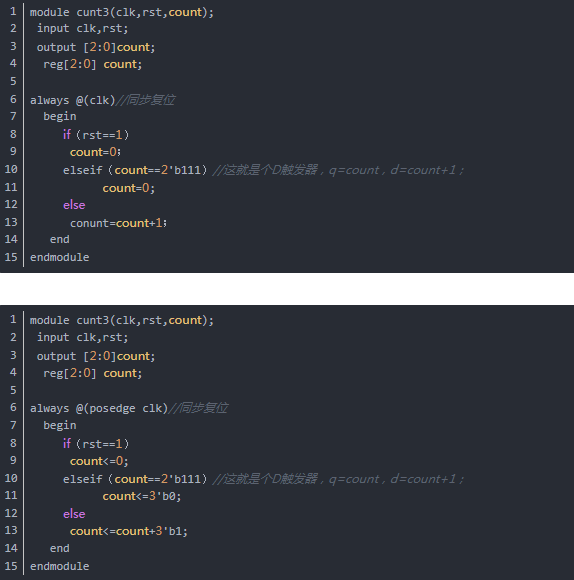

6296 分析:首先,我們可以看到有哪些信號。復位rst 、計數器3位的、時鐘信號。(用到2路選擇器。復位和不復位)

其次,怎樣實現,一個時鐘過來,記一次數就是加一次,保存(用到D觸發器),滿之后為0;

2019-02-01 07:08:00 2354

2354

xilinx推薦盡量不復位,利用上電初始化,如果使用過程中需要復位,采用同步高復位。

2019-02-14 14:29:49 5419

5419 異步復位同步釋放是指復位信號是異步有效的,即復位的發生與clk無關。后半句“同步釋放”是指復位信號的撤除也與clk無關,但是復位信號是在下一個clk來到后起的作用(釋放)。

2019-11-20 07:06:00 3647

3647 首選我們來聊聊時序邏輯中最基礎的部分D觸發器的同步異步,同步復位即復位信號隨系統時鐘的邊沿觸發起作用,異步復位即復位信號不隨系統時鐘的邊沿觸發起作用,置數同理,rst_n表示低電平復位,我們都知道

2019-07-26 10:17:16 24507

24507

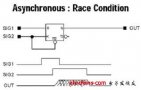

同步復位和異步復位都是狀態機的常用復位機制,圖1中的復位電路結合了各自的優點。同步復位具有時鐘和復位信號之間同步的優點,這可以防止時鐘和復位信號之間發生競爭條件。但是,同步復位不允許狀態機工作在直流時鐘,因為在發生時鐘事件之前不會發生復位。與此同時,未初始化的I/O端口可能會遇到嚴重的信號爭用。

2019-08-12 15:20:41 6901

6901

復位信號的有效時長必須大于時鐘周期,才能真正被系統識別并完成復位任務。同時還要考慮,諸如:clk skew,組合 邏輯路徑延時,復位延時等因素。

2019-08-21 17:51:49 1745

1745 復位信號設計的原則是盡量不包含不需要的復位信號,如果需要,考慮使用局部復位和同步復位。

2019-10-27 10:09:53 1735

1735

先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 2456

2456

FPGA開發中,一種最常用的復位技術就是“異步復位同步釋放”,這個技術比較難以理解,很多資料對其說得并不透徹,沒有講到本質,但是它又很重要,所以對它必須理解,這里給出我的看法。

2020-08-18 13:56:00 1114

1114

同步復位:顧名思義,同步復位就是指復位信號只有在時鐘上升沿到來時,才能有效。否則,無法完成對系統的復位工作。用Verilog描述如下:異步復位:它是指無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。用Verilog描述如下:

2020-09-14 08:00:00 0

0 1、什么是同步邏輯和異步邏輯,同步電路和異步電路的區別是什么? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 電路設計可分類為同步電路和異步電路設計。同步電路利用

2020-11-09 14:58:34 9142

9142 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1. 異步復位: 優點:⑴大多數

2020-10-30 12:17:55 323

323 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-12-22 12:54:00 13

13 針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2021-04-27 18:12:10 4196

4196

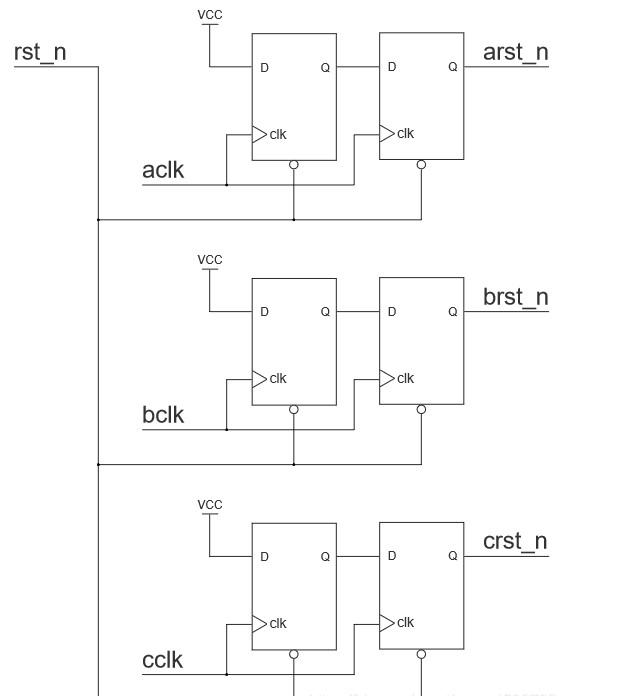

1 多時鐘域的異步復位同步釋放 當外部輸入的復位信號只有一個,但是時鐘域有多個時,使用每個時鐘搭建自己的復位同步器即可,如下所示。 verilog代碼如下: module CLOCK_RESET

2021-05-08 09:59:07 2207

2207

基于FPGA的小波濾波抑制復位噪聲方法

2021-07-01 14:42:09 24

24 。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何其它輸入引腳類似,對 FPGA 來說往往是異步的。設計人員可以使用這個信號在 FPGA 內部對自己的設計進行異步或者同步復位。常見的復位方式有三種1、硬件開關:復位信號接一個撥碼開關或按鍵,.

2021-11-06 09:20:57 20

20 復位中的同步復位和異步復位問題:恢復時間是指異步復位信號釋放和時鐘上升沿的最小距離,在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個異步控制

2022-01-17 12:25:49 0

0 異步復位,同步釋放的理解目錄目錄 同步復位和異步復位 異步復位 同步復位 那么同步復位和異步復位到底孰優孰劣呢? 異步復位、同步釋放 問題1 問題2 問題3 問題4 問題5 參考資料同步

2022-01-17 12:53:57 4

4 首先回想一下,在平常的設計中我們是不是經常采用同步復位或者異步復位的寫法,這一寫法似乎都已經形成了肌肉記憶----每次我們寫always塊的時候總是會對所有的寄存器寫一個復位賦初值的語句。

2022-02-19 19:10:32 2092

2092 可預置同步4位二進制計數器;異步復位-74LVC161

2023-02-15 19:23:09 0

0 可預置同步4位二進制計數器;異步復位-74HC161_Q100

2023-02-16 21:10:00 1

1 可預置同步4位二進制計數器;異步復位-74HC161

2023-02-16 21:10:17 2

2 可預置同步BCD十進制計數器;異步復位-74HC160

2023-02-20 20:05:50 10

10 有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-03-13 10:29:49 1585

1585 為確保系統上電后有一個明確、穩定的初始狀態,或系統運行狀態紊亂時可以恢復到正常的初始狀態,數字系統設計中一定要有復位電路的設計。復位電路異常可能會導致整個系統的功能異常,所以在一定程度上來講,復位電路的重要性也不亞于時鐘電路。

2023-03-28 13:54:33 5534

5534

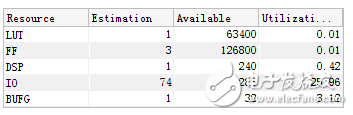

FPGA設計中幾乎不可避免地會用到復位信號,無論是同步復位還是異步復位。我們需要清楚的是復位信號對時序收斂、資源利用率以及布線擁塞都有很大的影響。

2023-03-30 09:55:34 806

806 。 下面將討論FPGA/CPLD的復位電路設計。 2、分類及不同復位設計的影響 根據電路設計,復位可分為異步復位和同步復位。 對于異步復位,電路對復位信號是電平敏感的,如果復位信號受到干擾,如出現短暫的脈沖跳變,電路就會部分或全部被

2023-04-06 16:45:02 782

782 本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。在FPGA和ASIC設計中,對于復位這個問題可以算是老生常談了,但是也是最容易忽略的點。本文結合FPGA的相關示例,再談一談復位。

2023-05-12 16:37:18 3347

3347

SoC設計中通常會有“全局”同步復位,這將影響到整個設計中的大多數的時序設計模塊,并在同一時鐘沿同步釋放復位。

2023-05-18 09:55:33 145

145

因此復位功能是很重要的一個功能。數字電路的復位通常可分為:同步復位與異步復位。

2023-05-19 09:05:52 747

747

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。

2023-05-22 14:21:08 577

577

本文將探討在? FPGA ?設計中添加復位輸入的一些后果。 本文將回顧使用復位輸入對給定功能進行編碼的一些基本注意事項。設計人員可能會忽略使用復位輸入的后果,但不正確的復位策略很容易造成重罰。復位

2023-05-25 00:30:01 483

483 有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-05-25 15:50:45 2110

2110

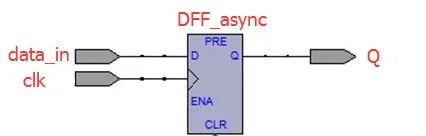

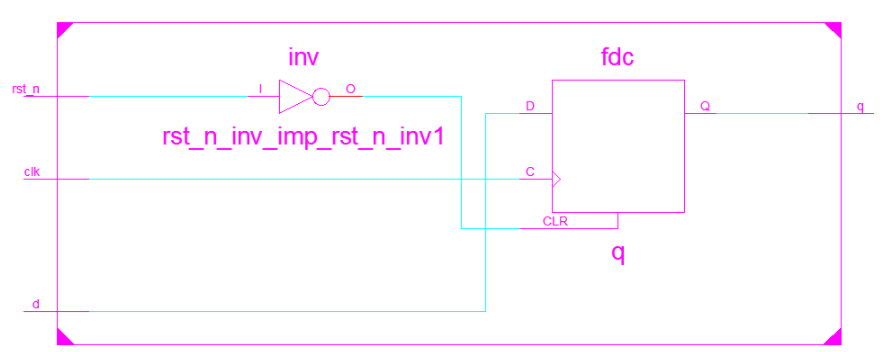

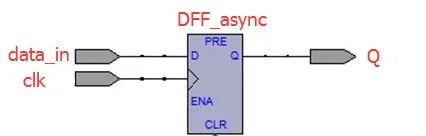

異步復位觸發器則是在設計觸發器的時候加入了一個復位引腳,也就是說**復位邏輯集成在觸發器里面**。(一般情況下)低電平的復位信號到達觸發器的復位端時,觸發器進入復位狀態,直到復位信號撤離。帶異步復位的觸發器電路圖和RTL代碼如下所示:

2023-05-25 15:57:17 567

567

盡量少使用復位,特別是少用全局復位,能不用復位就不用,一定要用復位的使用局部復位;

2023-06-21 09:55:33 1337

1337

對于復位信號的處理,為了方便我們習慣上采用全局復位,博主在很長一段時間內都是將復位信號作為一個I/O口,通過撥碼開關硬件復位。

2023-06-21 10:39:25 651

651

?本文主要是提供了 ASIC 設計中關于復位技術相關的概念和設計。

2023-06-21 11:55:15 4791

4791

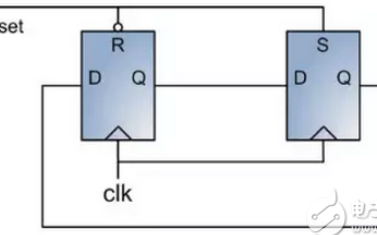

使用 2 個帶異步復位的寄存器,D端輸入邏輯 1(VCC)。

2023-06-26 16:39:17 884

884

能不復位盡量不用復位,如何判斷呢?如果某個模塊只需要上電的時候復位一次,工作中不需要再有復位操作,那么這個模塊可以不用復位,用上電初始化所有寄存器默認值

2023-06-28 14:44:46 526

526

請簡述同步復位與異步復位的區別,說明兩種復位方式的優缺點,并解釋“異步復位,同步釋放”。

2023-08-14 11:49:35 3418

3418 異步復位同步釋放:rst_synchronizer.v

2023-08-21 09:27:51 516

516

點擊上方 藍字 關注我們 系統的復位對于系統穩定工作至關重要,最佳的復位方式為:異步復位,同步釋放。以下是轉載博客,原文標題及鏈接如下: 復位最佳方式:異步復位,同步釋放 異步復位; 異步

2023-09-09 14:15:01 282

282

同步復位和異步復位到底孰優孰劣呢? 同步復位和異步復位是兩種不同的復位方式,它們各自有優勢和劣勢,下面將詳細介紹這兩種復位方式。 同步復位是指在時鐘的邊沿(上升沿或下降沿)發生時對系統進行復位。這種

2024-01-16 16:25:52 202

202

電子發燒友App

電子發燒友App

評論