本文以標準的I2C 總線協議為基礎,提出了一種基于FPGA的I2C SLAVE 模式總線的設計方案。方案主要介紹了SLAVE 模式的特點。給出了設計的原理框圖和modelsim 下的行為仿真時序

2014-02-26 11:39:13 12337

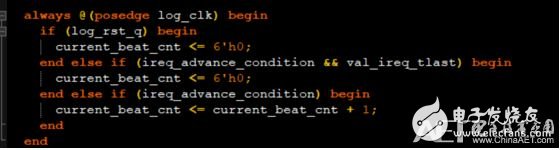

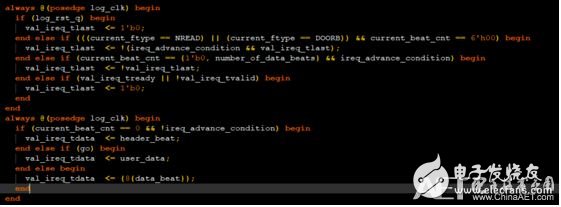

12337 等于b0000(非緩沖和非緩存)。 5) 不支持互斥性操作。 Zynq中AXI-Stream功能 AXI-Stream協議作為一個標準接口,用于連接數據交換元

2020-09-27 11:33:02 8051

8051

,是面向地址映射的接口,允許最大256輪的數據突發傳輸; (B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元。 (C)AXI4-Stream:(F

2020-12-04 12:22:44 6179

6179

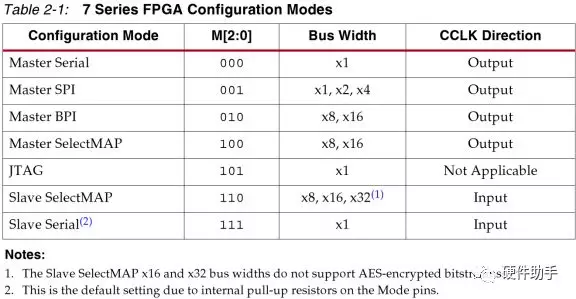

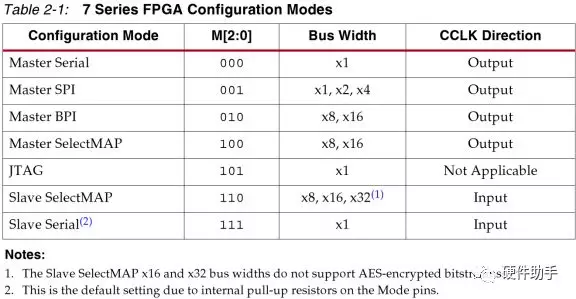

本文主要介紹Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21577

21577

一、AXI DMA介紹 本篇博文講述AXI DMA的一些使用總結,硬件IP子系統搭建與SDK C代碼封裝參考米聯客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數據傳輸,需要利用PS的HP

2020-12-31 09:52:02 7166

7166

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

2023-11-23 16:03:45 580

580

和Stream 接口支持64bit,128bit和256bit的數據AXI4 Master和Slave接口可配置成AXI3接口配置:通過PCIE和(或)AXI4-Lite Slave接口可操作橋配置空間

2016-03-11 10:57:58

AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據突發傳輸規模

2021-01-08 16:52:32

和輔助數據包不會通過AXI4-Stream上的視頻協議傳輸。Table 1-1 和Table 1-2 中列出AXI4S接口視頻IP需要的所有信號。Table 1-1 顯示了輸入(從)側連接器的接口信號名稱

2022-11-14 15:15:13

個恒定的6個32位字,所以必須注意幀數據或控制數據的緩沖區填滿的條件。防止無序狀況。“我還說在AXI4-Stream接口中“數據是以數據包的形式傳輸而不是連續流”。最大9Kb“幀”大小是否也適用于通過AXI4-Stream接口發送的最大“數據包大小”?問候。

2020-05-25 09:37:36

Controller 的輸出(讀取通道)連接到 AXI Stream FIFO ,最后處理器通過 AXI4-Lite 接口讀取數據。下面顯示了設計中的輸入路徑,其中包含由 XADC 生成的信號和一個

2022-11-04 11:03:18

https://gist.github.com/promach/251cbb3c9c9af401bf712dc4ccb76fb3為何這個 AXI 代碼 不通過 AXI Protocol

2020-02-28 13:44:01

。 AXI4-Stream:(For high-speed streamingdata.)面向高速流數據傳輸;去掉了地址項,允許無限制的數據突發傳輸規模。 Stream的理解,可以想象一下

2022-10-14 15:31:40

機數據本次傳輸有效;(8) TUSER信號 :用戶定義信號,寬度為128bit。對于AXI4-Stream總線命名而言,除了總線時鐘和總線復位,其他的信號線都是以T字母開頭,后面跟上一個有意義的單詞

2022-04-08 10:45:31

我正在使用AXI流FIFO將數據流式傳輸到Rx端,最終也將通過AXI總線從處理器讀回。當我嘗試讀取“base_address + 0x1C”時,系統掛起......以前有人遇到過這種情況嗎?在閱讀

2019-04-24 12:54:04

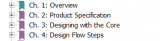

保障先后順序(后接受數據的slave端口可能先返回讀數據)。為此,Axi4ReadOnlyDecoder設計時采用了如下原則:對于每個通道,均支持readIssuingCapability,但如果當前

2022-08-04 14:28:56

大家好。當我在zynq-7000中使用axi quad spi ip core作為從設備時,我遇到了一個問題。我將slave axi quad spi ip core連接到另一個在主模式下配置

2020-04-17 10:13:04

STREAM DEV BOARD

2023-03-29 19:42:39

有一天,我能夠在Questasim中檢索XILINX_AXI_BFM許可證,第二天它失敗并且從那時起失敗了。許可證服務器已重置但仍然失敗...有任何想法嗎?#BFM Xilinx

2018-11-29 16:10:10

AXI4-Streamslave接口上TDATA信號的寬度(以字節為單位)。 AXI4-Stream主接口TDATA寬度是此值乘以從屬接口數參數。此參數是一個整數,可以在0到(512 /從站接口數)之間變化。設置為0以省略

2020-08-20 14:36:50

你好,大家好。我正在使用EMI14.4和xc6v315t。我正在嘗試模擬IP CORE.It的axi4-stream interconnect.I配置ip為6siand 4mi。但是當我用ismI模擬它時發現s_tready很低,有什么問題?

2020-06-18 15:08:59

今天有空來學習一下xilinx的axi_iic ip。下面的鏈接是xilinx官網關于axi_iic的數據手冊,大家點一下就可以看了pg090-axi-iic pdf數據手冊先給我們這個ip的頂層

2022-01-18 07:00:13

我對AXI互連有疑問,1.我的AXI4 Masterwith數據寬度為32位。我有64位數據寬度的AXI3從器件。互連如何工作?2.如果我有64位的PL AXI3 Master,我想連接到PS

2019-04-01 10:10:35

,通過data信號,來傳輸數據,data信號的位寬,也是固定的,為16bit。1、下行接口信號下行接口信號如下表所示,接口協議是基于AXI-stream協議。2、上行接口信號上行接口信號如下表所示

2022-04-07 10:42:34

地址通道中,主機(master)是發送方,而從機(slave)是接收方;在讀數據通道中,主機是接收方,從機是發送方。3、AXI協議傳輸事務的結構了解完通道握手的依賴關系,我們再看看傳輸事務的結構。首先

2022-04-08 09:34:43

英飛凌CYT4BF8CES的SPI通信的SDL中,Slave模式的High level如何修改發送的數據?目前只有初始化buffer能夠成功發送,中間如果修改buffer會進中斷并且報bus error。

2024-02-01 07:59:57

in the reference design consist of AXI4, AXI4-Lite, andAXI4-Stream interfaces as described in the AMBA AXI4

2012-01-26 18:57:03

你好:我用IIC demo的時候,例程中master發送數據slave去接收,但是沒有master接收數據的接口I2c_HLD_LPI2C_Transfer_S32K344:C

2023-03-31 08:48:12

DSP28335的MCBSP配置為spi的slave模式,接收不到數據。哪位有相似的例程能給發一份嗎?郵箱853744449@qq.com謝謝

2013-09-12 18:31:14

、新的RadixTree數據結構來支持更高效的內存使用和消息讀取、甚至是類似于Kafka的Consumer Group功能。今天我們重點關注怎么在實際業務場景下去使用Redis Stream。Redis

2018-06-26 17:15:29

SPI SLAVE模式可以用DMA方式接收數據嗎?

2017-09-14 15:49:55

我現在使用pynq z2板在 SPI 標準模式下傳輸數據,在程式碼中板子設置為”master”,但是我的項目需要在“slave”下使用z2板,我瀏覽了PG153 AXI Quad SPI

2022-09-30 12:57:28

In to AXI4-Stream IP核開發文檔為產品資料“6-開發參考資料\Xilinx官方參考文檔\”目錄下的《pg043_v_vid_in_axi4s.pdf》。本案例使用IP核采集一路攝像頭視頻

2021-05-24 11:12:40

嗨,我已經創建了一個帶有IP-Core的硬件設計。但它不能正常工作。對于我提到的調試問題,我創建了一個IP-Core,然后通過AXI Stream。所以我可以檢查我的IP-Core是否不起作用

2020-04-14 09:25:10

memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;AXI4-Lite:(For simple

2018-01-08 15:44:39

。

●AXI4_Stream:面向高速流數據傳輸,去掉了地址項,允許無限制的數據突發傳輸規模。

三種總線的組成如下所示,其中AXI與AXI_Lite有相同的組成部分:

(2)AXI接口

接口是一種連接標準,又常常被稱之為物理

2023-11-03 10:51:39

請問,cyw20719B2 SPI 接口slave模式下,在執行wiced_hal_pspi_slave_rx_data()函數的同時,SPI的FIFO還能正確接收數據嗎?

wiced_hal_pspi_slave_rx_data()函數在執行時,是否需要master暫停數據發送?

謝謝。

2024-03-01 11:34:55

) AXI協議(又稱AXI4.0),包括3種接口標準:AXI4、AXI-Stream、AXI-lite。AXI4:適用于要求數據高速傳輸的場合。AXI-Stream:如FIFO,數據傳輸不需要地址,而是

2016-12-16 11:00:37

、AXI4-Stream:用于高速數據流傳輸,非存儲映射接口。在這里我們首先解釋一下存儲映射(Meamory Map)這一概念。如果一個協議是存儲映射的,那么主機所發出的會話(無論讀或寫)就會標明一個地址。這個地址對應

2020-10-22 15:16:34

原子公眾號,獲取最新資料第十八章PS通過VDMA驅動LCD顯示實驗AXI VDMA是Xilinx專門針對視頻應用提供的一種高帶寬的解決方案,旨在實現AXI4-Stream視頻接口和AXI4接口之間的高

2020-09-04 11:15:28

RAM,編程也很方便,開發難度較低。代價就是資源占用過多,需要額外的讀地址線、寫地址線、讀數據線、寫數據線、寫應答線這些信號線。 AXI4-Stream: 這是一種連續流接口,不需要地址線(很像

2021-01-07 17:11:26

配置v_axi4s_vid_out(簡短:vout)參數VBG_MASTER_SLAVE = 1(主)vout的初始化標志總是向上,沒有達到鎖定狀態!但是有一些我無法解決的異常情況,我希望Xilinx

2019-07-15 09:47:54

使用SpinalHDL lib中所提供的Event:Event對應一個payload為NoData的Stream信號,而NoData顧名思義,其實現為一個空的Bundle:》Example這里我們以Axi4

2022-06-27 16:07:04

想知道,如果我啟用AXI4Stream,我可以從AXI流端口(m_axis_tdata)獲取輸出采樣數據嗎?或者它仍然只能從DRP端口獲取。配置如下圖所示。問候穆罕默德·

2020-05-20 14:53:11

[]合成了內存),輸出端口合成為ap_fifo,這意味著,由于AXi4Lite不支持fifo結構,因此只能使用AXI4Stream接口/總線從輸出端口result []讀取數據。我也是這個嵌入式總線和接口

2019-02-28 13:47:30

vip中memoty的數據全部讀出,并存入txfifo。4、 txfifo上的axi-stream master接口將txfifo內的數據以axi-stream的形式傳給axi stream vip

2022-10-09 16:08:45

IP接口板接口 SPI CustomIP配置 AXI接口選項 - >啟用XIP模式:是 - > ID_Width:4 - > SPI閃存地址位(XIP模式):32 SPI選項

2020-06-09 09:42:44

大家好,我正在兩個時鐘域之間穿過AXI4-Stream,并嘗試使用AXI4-Stream時鐘轉換器核心,使用tkeep端口但是在合成時它被Vivado 2015.2在實例化時刪除了!這是綜合警告

2020-05-08 08:56:14

我有SP605& ML506 Xilnx開發板。我想從FPGA驅動CH7301芯片。我正在尋找一些帖子或應用筆記,可以幫助我把這兩件事放在一起。我一直在關注核心AXI4-Stream到視頻

2020-03-20 09:04:51

數據從BRAM / DDR傳輸到自定義axi slave時,問題就出現了。我進行了測試以驗證這一點:我嘗試使用AXI CDMA從DDRto自定義從站發送4個字節的數據,并且它正常工作。但是當我增加要傳輸

2020-08-12 10:37:46

大家好。我目前正在使用GTH收發器實現更復雜的設計,這些收發器工作在2.8 GHz(5.6GB),我想知道我是否可以使用AXI4流以某種方式從收發器中提取輸入數據。有沒有辦法將數據寫入內存并

2019-05-05 13:14:10

現在我正在使用Xilinx的AXI視頻處理內核進行小型設計。現在我面對一個奇怪的問題。我的設計很簡單。我使用Xilinx的三個內核:1.測試模式發生器(TPG)2。視頻定時控制(VTC

2019-03-08 10:00:05

1、?構建自定義AXI4-Stream FIR濾波器 AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程

2022-11-07 16:07:43

數據)。為此,Axi4WriteOnlyDecoder設計時采用了如下原則:1、對于每個通道,均支持writeIssuingCapability,但如果當前指令地址譯碼命中的slave端口和上次不一樣

2022-08-03 14:27:09

,ar)共用一組信號的接口(arw,w,b,r)。關于總線互聯的設計凡是設計中用到Axi4總線的設計總離不開總線互聯。在Xilinx FPGA使用中,VIvado針對Axi4總線提供了豐富的IP,對于

2022-08-02 14:28:46

嗨,我已經通過以太網MAC IP作為“LogiCORE IP 10千兆以太網MAC v13.1”U.G. PG072。由于我對AXI沒有太多了解,因此我幾乎沒有查詢讀取AXI4-Stream接口

2020-04-28 10:00:42

大家好。我遇到了xilinx視頻內核的問題,并試圖解決這個問題好幾周但都失敗了。有人能給我一些關于AXI4-Stream到Video核心的技巧嗎?我試圖在我的項目中實現Video Scaler核心

2019-11-08 09:53:46

我們可以使用AXI-Stream Broadcaster作為AXI開關嗎?如果可能,我們需要控制切換哪個信號?我想開發小型應用程序,它涉及廣播AXI流數據并將AXI流數據切換到特定的從站。在這個應用程序中,我們只有一個主站和8個從站。我們想在從站之間切換流數據。提前致謝。

2020-05-07 09:42:16

嗨,我正在研究Spartan 6的設計。數據來自PCIe IP核,頻率為62.5MHz,通過AXI4-Stream FIFO同步到100 MHz系統時鐘。這是一個示例波形;m_axis_tvalid

2019-08-12 07:29:20

Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口: 所以要把標準的VESA信號 轉為

2017-02-08 08:36:19 531

531

基于AXI4Stream總線協議,在Xilinx公司提供的FPGA上實現了一個具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實時圖像采集與顯示功能的視頻系統。AXI4Stream總線協議由ARM公司

2017-11-17 08:58:01 4189

4189 IP核的全稱是: AXI4-STREAM FIFO 設置注意事項:一定要選擇異步時鐘,也就是雙時鐘,如下: 關于其他配置: TLAST 一般要選擇的,作為邊界界定。其他可以不選。深度不必太深,因為只起到穿越時鐘區域的作用。

2018-03-26 14:40:00 4916

4916

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

2018-11-20 06:38:00 3561

3561 自定義sobel濾波IP核 IP接口遵守AXI Stream協議

2019-08-06 06:04:00 3573

3573 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

M_AXI接口對數據進行讀取操作,此時設計一個基于AXI-Slave接口的IP進行數據傳輸操作就非常的方便。 封裝的形式并不復雜,只是略微繁瑣,接下來一步一步演示如何封裝AXI_SLAVE接口IP

2020-10-30 12:32:37 3953

3953

DMA的總結 ZYNQ中不同應用的DMA 幾個常用的 AXI 接口 IP 的功能(上面已經提到): AXI-DMA:實現從 PS 內存到 PL 高速傳輸高速通道 AXI-HP----AXI-Stream

2020-10-09 18:05:57 6391

6391

AXI-Lite或AXI4轉接。PS與PL之間的物理接口有9個,包括4個AXI-GP接口和4個AXI-HP接口、1個AXI-ACP接口。 Xilinx提供的從AXI到AXI-Stream轉換的IP核有:AXI-DMA,AXI-Datam

2020-11-02 11:27:51 3880

3880

AXI-Stream代碼詳解 AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據

2020-11-05 17:40:36 2826

2826

在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 12802

12802 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 XI4-Stream跟AXI4的區別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時。由于AXI4-Stream協議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,

2022-06-23 10:08:47 1781

1781 本文主要介紹關于AXI4-Stream Video 協議和AXI_VDMA的IP核相關內容。為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 6846

6846 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數據流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 使用Vivado生成AXI VIP(AXI Verification IP)來對自己設計的AXI接口模塊進行全方位的驗證(如使用VIP的Master、Passthrough、Slave三種模式對自己寫的AXI

2022-10-08 16:07:11 3846

3846 Xilinx vivado下通常的視頻流設計,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556 大家好!今日分享一些關于Video In to AXI4-Stream IP 核的知識。在具體學習IP核的過程中,我也將分享一些關于如何看xilinx英文文檔的技巧。

2023-05-18 14:55:16 966

966

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

AXI4協議是一個點對點的主從接口協議,數據可以同時在主機(Master)和從機(Slave)之間**雙向** **傳輸** ,且數據傳輸大小可以不同。

2023-06-21 15:26:43 1388

1388

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

?AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下AXI VIP當作master時如何使用。

2023-07-27 09:16:13 792

792

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 2357

2357

LogiCORE IP AXI4-Stream FIFO內核允許以內存映射方式訪問一個AXI4-Stream接口。該內核可用于與AXI4-Stream IP接口,類似于LogiCORE IP AXI以太網內核,而無需使用完整的DMA解決方案。

2023-09-25 10:55:33 497

497

Xilinx 從 Spartan-6 和 Virtex-6 器件開始采用高級可擴展接口 (AXI) 協議作為知識產權 (IP) 內核。Xilinx 繼續將 AXI 協議用于針對 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

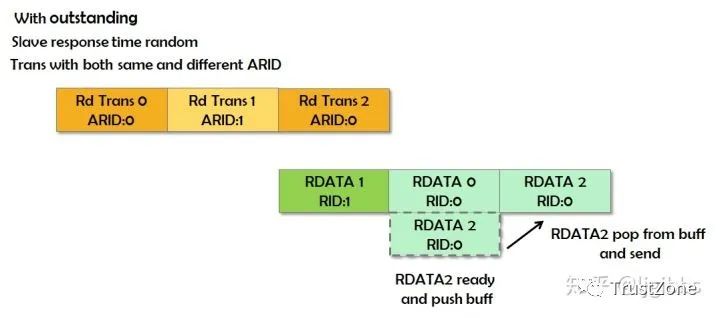

AXI的控制和數據通道分離,可以帶來很多好處。地址和控制信息相對數據的相位獨立,可以先發地址,然后再是數據,這樣自然而然的支持顯著操作,也就是outstanding 操作。 Master訪問

2023-10-31 16:53:09 432

432

電子發燒友App

電子發燒友App

評論