大家好,我已閱讀任何與TrustZone相關(guān)的內(nèi)容,但我無法弄清楚這兩個世界是如何相互溝通的。我所能找到的只是TrustZone API規(guī)范中的內(nèi)容:客戶端和服務(wù)可以通過兩種機(jī)制進(jìn)行通信:結(jié)構(gòu)化

2019-03-20 08:58:16

讀txt文件將16進(jìn)制字符轉(zhuǎn)化為ASCII,寫入txt文件,可是只能轉(zhuǎn)換6個字符,這個問題怎么解決?

2016-12-21 14:08:51

原型驗(yàn)證過程中的ASIC到FPGA的代碼是怎樣進(jìn)行轉(zhuǎn)換的?

2021-05-08 09:16:18

進(jìn)行重新編程。 2、開發(fā)流程區(qū)別: FPGA開發(fā)是利用HDL和quartus、vivado等EDA工具,重新配置(configure)芯片的功能,而ASIC通常都具有較少的可重配置能力。 ASIC

2020-12-01 17:41:49

ASIC技術(shù)過時的報道是不成熟的。新的ASIC產(chǎn)品的數(shù)目可能有大幅度下降,但其銷售額仍然相當(dāng)高,尤其是在亞太區(qū)。此外,采用混合式方法,如結(jié)構(gòu)化ASIC,也為該技術(shù)注入了新的活力。同時,FPGA(和其他可編程邏輯器件)也在發(fā)揮作用,贏得了重要的大眾市場,并從低端應(yīng)用不斷向上發(fā)展。

2019-07-19 06:24:30

設(shè)計過程中,往往要用到 FPGA 進(jìn)行原型驗(yàn)證。FPGA 驗(yàn)證是進(jìn)行 ASIC 設(shè)計的重要環(huán)節(jié),其后,還需要引入 ASIC 版本源碼,插入 IO PAD,DFT,功耗估計和進(jìn)行其它后端流程。完成

2020-09-25 11:34:41

、系統(tǒng)集成和系統(tǒng)仿真驗(yàn)證、綜合、STA(靜態(tài)時序分析)、形式驗(yàn)證。插一句,在ASIC 設(shè)計過程中,往往要用到FPGA 進(jìn)行原型驗(yàn)證。FPGA 驗(yàn)證是進(jìn)行ASIC 設(shè)計的重要環(huán)節(jié),其后,還需要引入ASIC

2017-09-02 22:24:53

YoloV3模型的pytorch權(quán)重文件轉(zhuǎn)化為onxx然后使用圖形化界面進(jìn)行轉(zhuǎn)化,只要安裝了rknn模塊就會有圖形化界面python3 -m rknn.bin.visualization量化成功生成成功原作者:雨淺聽風(fēng)吟

2022-05-09 16:36:55

一般繪制的都是schdoc,即電路原理圖,將其轉(zhuǎn)化為 pcbdoc的詳細(xì)步驟有哪些?謝謝主!!1

2011-03-11 09:38:38

將四字節(jié)16進(jìn)制數(shù)轉(zhuǎn)化為浮點(diǎn)數(shù)近期機(jī)緣湊巧幫了朋友一個忙,在Modbus協(xié)議下,將采集到的十六進(jìn)數(shù)轉(zhuǎn)化為浮點(diǎn)數(shù),有幾種解決方法,分享給需要的朋友,令其少走一些彎路。眾所周知,Modbus通信協(xié)議

2018-12-01 06:13:07

熱源、EMI干擾源等方面的問題給出相關(guān)的參考建議。可以和其他哪些網(wǎng)絡(luò)共用管線,特別是在有電力電纜分布的地方,EMI問題應(yīng)特別加以注意。 5.走線圖 在結(jié)構(gòu)化布線系統(tǒng)進(jìn)行安裝以前必須準(zhǔn)備一份完整的電纜

2016-05-19 13:46:23

。數(shù)據(jù)線纜中緊緊絞在一起的線對起到毛細(xì)管作用,能將水吸入線纜內(nèi)一定長度,破壞了其電氣性能。受這種方式影響的線纜幾乎都不得不更換掉。 四、預(yù)防勝于補(bǔ)救 更換一個受潮的結(jié)構(gòu)化布線系統(tǒng)將耗費(fèi)大量時間,昂貴且

2016-05-15 10:55:10

微型計算機(jī)控制技術(shù)_第五章第5章 常用應(yīng)用程序設(shè)計 本章以51單片機(jī)為基礎(chǔ),主要介紹結(jié)構(gòu)化匯編語言的監(jiān)控程序設(shè)計思想和實(shí)時測控系統(tǒng)中最常用的數(shù)字濾波技術(shù)、標(biāo)度變換、插值算法以及報警程序設(shè)計等。 程序

2021-09-10 06:50:34

結(jié)構(gòu)化程序設(shè)計和面向?qū)ο蟪绦蛟O(shè)計,在接下來很長的一段時間里,我將陸續(xù)分享項(xiàng)目實(shí)戰(zhàn)經(jīng)驗(yàn)。從電源、單片機(jī)、晶體管、驅(qū)動電路、顯示電路、有線通訊、無線通信、傳感器、原理圖設(shè)計、PCB設(shè)計、軟件設(shè)計、上位機(jī)等,給新手綜合學(xué)習(xí)的平臺,給老司機(jī)交流的平臺。所有文章來源于項(xiàng)目實(shí)戰(zhàn),屬于原創(chuàng)。

2021-07-14 06:35:13

結(jié)構(gòu)化設(shè)計分為哪幾部分?結(jié)構(gòu)化設(shè)計的要求有哪些?結(jié)構(gòu)化設(shè)計主要包括哪些部分?

2021-12-23 06:15:51

一張簡單的方法,系統(tǒng)的編輯器和調(diào)試器的功能是建立在高級編程語言的基礎(chǔ)上(如Visual C++)具體來說CoDeSys就是一個編程工具,支持IEC61131-3標(biāo)準(zhǔn)協(xié)議,用于工業(yè)PLC控制。CodeSys有六種編程語言(IL,ST,FBD,LD,CFC,SFC),而其中ST為結(jié)構(gòu)化文本。...

2021-07-02 07:34:28

Deeplearningai 結(jié)構(gòu)化機(jī)器學(xué)習(xí)項(xiàng)目 Week2 6-10

2020-05-18 15:12:43

單位之前的項(xiàng)目一直用原理圖做開發(fā),現(xiàn)在覺得不宜進(jìn)行大型開發(fā),想把之前的工程里的文件全部轉(zhuǎn)化為verilog代碼,即將原有的.sch文件轉(zhuǎn)化為.v文件,ISE有這種自動轉(zhuǎn)化的功能嗎?還是有別的方法?

2017-08-10 16:42:49

, TSV以及Apache ORC文件以外,MaxCompute同時開發(fā)了非結(jié)構(gòu)化Java SDK來方便用戶對數(shù)據(jù)進(jìn)行解析和處理。 通過這樣的方法,擴(kuò)展整個非結(jié)構(gòu)化數(shù)據(jù)處理的生態(tài),對接視頻,圖像,音頻

2018-05-15 12:21:06

的文本文件,可以用結(jié)構(gòu)化查詢的方式去分析非結(jié)構(gòu)化的數(shù)據(jù)。本文對使用MaxCompute分析OSS文本數(shù)據(jù)的實(shí)踐過程中遇到的一些問題和優(yōu)化經(jīng)驗(yàn)進(jìn)行了總結(jié)。作為前提,讀者需要詳細(xì)了解MaxCompute

2018-06-20 15:01:09

放在Flash芯片中,通過上電加載到FPGA中,對其進(jìn)行初始化。也可在線對其編程,實(shí)現(xiàn)系統(tǒng)在線重構(gòu),這一特性可以構(gòu)建一個根據(jù)計算任務(wù)不同而實(shí)時定制的CPU,這是當(dāng)今研究的熱門領(lǐng)域。

2012-02-27 17:46:03

labview將一張圖片轉(zhuǎn)化為2D數(shù)組怎么弄啊

2015-08-04 15:27:14

在使用pictureBox顯示網(wǎng)絡(luò)攝像頭的情況下,如何將視頻內(nèi)容轉(zhuǎn)化為labview可識別的image圖像,網(wǎng)上看到有2種方法。網(wǎng)址如下https://forums.ni.com/t5

2020-09-19 12:47:31

labview如何將正弦輸出信號轉(zhuǎn)化為0-5V的高低電平信號輸出?

2019-07-26 14:13:32

labview怎么將采集的灰度值轉(zhuǎn)化為灰度圖?

2018-03-14 18:57:29

請教各位,matlab如何將mat數(shù)據(jù)轉(zhuǎn)化為analyze數(shù)據(jù),謝謝

2012-12-18 11:41:01

根據(jù)結(jié)構(gòu)化道路環(huán)境的特點(diǎn)提出了一種將邊沿檢測和道路環(huán)境知識相結(jié)合的機(jī)器視覺算法 , 并結(jié)合基于行為響應(yīng)的路徑規(guī)劃方法和智能預(yù)瞄控制方法 , 實(shí)現(xiàn)了一套基本的機(jī)器人視覺導(dǎo)航系統(tǒng) . 在自主機(jī)器人實(shí)驗(yàn)

2023-09-25 07:23:39

。

ASIC用于設(shè)計規(guī)模大、復(fù)雜度高的芯片,或者是成熟度高、產(chǎn)量比較大的產(chǎn)品。

FPGA還特別適合初學(xué)者學(xué)習(xí)和參加比賽。現(xiàn)在很多大學(xué)的電子類專業(yè),都在使用FPGA進(jìn)行教學(xué)。

從商業(yè)化的角度來看,FPGA

2024-01-23 19:08:55

信號分布的處理,你們有什么建議可以提供給客戶?如果你的客戶準(zhǔn)備移植到另外一個FPGA、ASIC和結(jié)構(gòu)化ASIC之間進(jìn)行抉擇?結(jié)構(gòu)化ASIC或ASIC,你會建議你的客戶如何做?問:目前FPGA應(yīng)用工

2012-02-27 15:18:09

現(xiàn)已在PC端將圖片轉(zhuǎn)化為bin文件了,按照構(gòu)架我應(yīng)該把bin文件寫到FLASH里面,請問是通過FPGA芯片把bin文件寫到FLASH里面嗎

2020-02-18 16:38:46

如何將十六進(jìn)制數(shù)據(jù)轉(zhuǎn)化為JPEG格式的數(shù)據(jù)??

2016-01-12 14:14:52

我的設(shè)計完全在Verilog中,并且已經(jīng)使用Spartan FPGA進(jìn)行了測試。我將源代碼提供給ASIC工廠,以實(shí)現(xiàn)作為ASIC使用他們(我認(rèn)為)的概要工具。我的問題是,有沒有辦法使用任何

2019-07-25 13:44:31

如何使用STM32串口中斷服務(wù)函數(shù)進(jìn)行接收并進(jìn)行轉(zhuǎn)化為int型?

2021-12-07 08:03:30

如何使用arm匯編指令去實(shí)現(xiàn)一種結(jié)構(gòu)化編程呢?有哪位大神可以解答一下嗎

2022-11-09 15:18:11

ASIC驗(yàn)證能夠采用的主要技術(shù)是什么?如何利用現(xiàn)成FPGA開發(fā)板進(jìn)行ASIC原型開發(fā)?

2021-05-08 07:51:04

用Verilog怎樣將小數(shù)(例如0.2,-3.4之類的)轉(zhuǎn)化為單精度浮點(diǎn)數(shù)?

2023-10-18 06:48:53

如何用labview程序將二維圖片轉(zhuǎn)化為比特序列?

2018-05-16 11:13:27

如果想要將CMOS電平脈沖信號通過光纖進(jìn)行傳遞,最后再轉(zhuǎn)化為cmos脈沖信號,有什么方法?求各位指點(diǎn)

2020-06-17 20:48:04

較慢的CPU,將NN的FPGA實(shí)現(xiàn)與GPU / NPU和ASIC的實(shí)現(xiàn)進(jìn)行一下對比。事實(shí)證明,FPGA的獨(dú)特優(yōu)勢在于其可重新配置能力。這也解釋了為什么目前很多學(xué)術(shù)資源研究如何將FPGA高效地用于NN

2023-02-08 15:26:46

對與性能比較低的51單片機(jī),結(jié)構(gòu)化編程性能提升多少

2023-10-26 06:21:44

怎么將Protel格式文件轉(zhuǎn)化為Allergro文件

2014-08-05 13:35:29

怎么實(shí)現(xiàn)基于結(jié)構(gòu)化方法的無線傳感器網(wǎng)絡(luò)設(shè)計?

2021-05-31 06:34:16

整數(shù)轉(zhuǎn)化為字符

2016-04-07 15:20:55

除了matlab軟件自帶的,請問還有什么比較好方法讓matlab仿真圖轉(zhuǎn)化為DSP程序,網(wǎng)上不好查找,聽說研究這個的大神比較少,求幫忙,謝謝!!!!!!!!

2017-08-30 15:30:20

實(shí)驗(yàn)名稱:基于電場誘導(dǎo)的白光LED結(jié)構(gòu)化涂層制備及其應(yīng)用研究 研究方向:電場誘導(dǎo)結(jié)構(gòu)制備工藝試驗(yàn)研究 實(shí)驗(yàn)內(nèi)容: 本文主要圍繞:平面電極和機(jī)構(gòu)化電極兩種電場誘導(dǎo)工藝進(jìn)行試驗(yàn)研究,在平面電極

2022-03-29 15:44:41

LABVIWE中如何將科學(xué)計數(shù)法1.3e5,1.6e7,2.7e3,.......,nen轉(zhuǎn)化為數(shù)字?轉(zhuǎn)化的數(shù)字是分開獨(dú)立的數(shù)字。求大俠指點(diǎn),謝謝!

2011-12-28 22:40:32

FPGA和結(jié)構(gòu)化ASIC的優(yōu)勢是什么一個SPI4.2到ASI控制器的功能包括哪些?

2021-04-08 06:26:05

如何借助SC Express減少結(jié)構(gòu)化測試次數(shù)?

2021-05-11 06:46:56

各位大神,請問有什么傳感器可以將聲音信號轉(zhuǎn)化為數(shù)字信號?!急。

2019-07-08 23:28:16

在過去10年間,全世界的設(shè)計人員都討論過使用ASIC或者FPGA來實(shí)現(xiàn)數(shù)字電子設(shè)計的好處。通常這些討論將完全定制IC的性能優(yōu)勢和低功耗與FPGA的靈活性和低NRE成本進(jìn)行比較。設(shè)計隊(duì)伍應(yīng)當(dāng)在ASIC

2019-07-15 07:00:39

。EasyGo FPGA Solver 的優(yōu)點(diǎn)在于,能夠將Simulink的圖形化模型利用解算器軟件轉(zhuǎn)化成FPGA執(zhí)行的代碼,而不需要進(jìn)行FPGA的編譯

2022-05-19 09:21:43

ISSP結(jié)構(gòu)化ASIC解決方案

結(jié)構(gòu)化專用集成電路(structured ASIC)對設(shè)計工程師而言還是一個新名詞,然而目前已經(jīng)有多家公司正計劃涉足這一領(lǐng)域。快速硅

2009-12-27 13:32:40 1174

1174

FPGA原型驗(yàn)證和其他驗(yàn)證方法是不同的,任何一種其他驗(yàn)證方法都是ASIC驗(yàn)證中的一個環(huán)節(jié),而FPGA驗(yàn)證卻是一個過程。由于FPGA與ASIC在結(jié)構(gòu)、性能上各不相同,ASIC是基于標(biāo)準(zhǔn)單元庫,FPGA用的

2010-09-10 17:22:26 989

989 對ASIC設(shè)計進(jìn)行FPGA原型驗(yàn)證時,由于物理結(jié)構(gòu)不同,ASIC的代碼必須進(jìn)行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計流程中

2011-03-25 15:16:20 108

108 由于與深亞微米標(biāo)準(zhǔn)單元ASIC相關(guān)的非重復(fù)性工程費(fèi)用(NRE)越來越大,設(shè)計周期又很長,因此利用結(jié)構(gòu)化ASIC進(jìn)行定制IC設(shè)計的吸引力正變得越來越大。結(jié)構(gòu)化ASIC能以極具競爭力的單位成

2012-05-02 10:39:19 1655

1655

設(shè)計、程序設(shè)計之前,必須先確定軟件總體結(jié)構(gòu)。軟件總體結(jié)構(gòu)設(shè)計的方法主要有結(jié)構(gòu)化設(shè)計、面向數(shù)據(jù)結(jié)構(gòu)的設(shè)計和面向?qū)ο蟮脑O(shè)計,其中結(jié)構(gòu)化設(shè)計方法是應(yīng)用最廣泛的一種,它是建立良好程序結(jié)構(gòu)的方法,提出了衡量模塊質(zhì)量的標(biāo)準(zhǔn)是高

2017-10-19 14:38:54 0

0 ASIC 和 FPGA 具有不同的價值主張,選擇其中之一之前,一定要對其進(jìn)行仔細(xì)評估。2種技術(shù)的比較信息非常豐富。這里介紹了ASIC和FPGA的優(yōu)勢與劣勢。

2017-11-25 09:24:44 4374

4374 針對傳統(tǒng)文件結(jié)構(gòu)化相似性比較法中采用基本塊( BB) -對一映射而造成的巨大時空消耗及基本塊比較結(jié)果的絕對化問題,提出一種基于劃分思想的文件結(jié)構(gòu)化相似性比較方法。該方法首先對用于基本塊比較的小素數(shù)

2018-01-02 14:04:44 0

0 從非結(jié)構(gòu)化商品描述文本中抽取結(jié)構(gòu)化屬性信息,對于電子商務(wù)實(shí)現(xiàn)商品的對比與推薦及用戶需求預(yù)測等功能具有重要意義.現(xiàn)有結(jié)構(gòu)化方法大多采用監(jiān)督或半監(jiān)督的分類方法抽取屬性值與屬性名,通過文法分析器分析屬性

2018-01-02 15:58:42 0

0 與其他技術(shù)一樣,有關(guān)ASIC技術(shù)過時的報道是不成熟的。新的ASIC產(chǎn)品的數(shù)目可能有大幅度下降,但其銷售額仍然相當(dāng)高,尤其是在亞太區(qū)。此外,采用混合式方法,如結(jié)構(gòu)化ASIC,也為該技術(shù)注入了新的活力。同時,FPGA(和其他可編程邏輯器件)也在發(fā)揮作用,贏得了重要的大眾市場,并從低端應(yīng)用不斷向上發(fā)展。

2018-04-18 13:28:00 12141

12141

東方網(wǎng)力“天眼”結(jié)構(gòu)化一體機(jī)可以實(shí)現(xiàn)實(shí)時視頻流結(jié)構(gòu)化分析,并基于結(jié)構(gòu)化分析結(jié)果進(jìn)行告警、檢索和挖掘等功能,還可以針對離線視頻文件上傳并結(jié)構(gòu)化分析,基于分析結(jié)果進(jìn)行大數(shù)據(jù)分析、檢索等。所以,該一體機(jī)也可單機(jī)部署應(yīng)用。單機(jī)應(yīng)用模式架構(gòu)涉及的設(shè)備主要包括結(jié)構(gòu)化一體機(jī)、IPC或NVR等。

2018-08-14 17:34:33 5096

5096 采用fpga原型技術(shù)驗(yàn)證asic設(shè)計,首先需要把asic設(shè)計轉(zhuǎn)化為fpga設(shè)計。但asic是基于標(biāo)準(zhǔn)單元庫,fpga則是基于查找表,asic和fpga物理結(jié)構(gòu)上的不同,決定了asic代碼需要一定

2019-07-23 08:07:00 1923

1923

一旦僅用于膠合邏輯,FPGA已經(jīng)發(fā)展到可以在單個器件上構(gòu)建片上系統(tǒng)(SoC)設(shè)計的程度。門和功能的數(shù)量急劇增加,以與傳統(tǒng)上僅通過ASIC設(shè)備提供的功能相競爭。本文介紹了FPGA設(shè)計方法優(yōu)于ASIC的一些優(yōu)勢,包括早期上市,輕松過渡到結(jié)構(gòu)化ASIC,以及降低NRE成本。

2019-09-14 12:28:00 2308

2308 即便不考慮各個監(jiān)控系統(tǒng)之間的信息關(guān)聯(lián),光瀏覽這些視頻就需要花費(fèi)大量的人力物力。解決這一問題的核心技術(shù)即視頻結(jié)構(gòu)化描述技術(shù),將海量視頻或圖片的非結(jié)構(gòu)化數(shù)據(jù)提取并轉(zhuǎn)化為結(jié)構(gòu)化信息描述。

2020-03-20 10:20:50 2986

2986 視頻結(jié)構(gòu)化技術(shù)是一種把視頻畫面聲音、轉(zhuǎn)化為人和機(jī)器可以理解的信息的技術(shù),目前主要應(yīng)用于安防、交通領(lǐng)域,可以檢測車流、人流,甚至鎖定某個人,某輛車。

2020-04-03 10:39:11 790

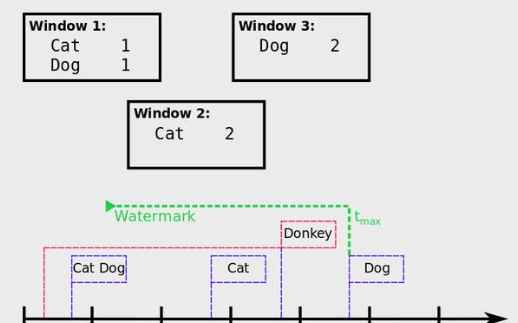

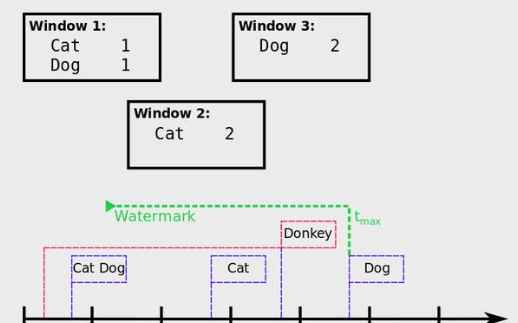

790 對于流處理引擎來說,處理延遲到達(dá)的事件是至關(guān)重要的功能。 解決這個問題的方法是加水位線的概念。 從Spark 2.1開始,結(jié)構(gòu)化流API就支持它。

2020-05-03 17:28:00 2321

2321

系統(tǒng),是首個結(jié)構(gòu)化eASIC產(chǎn)品系列。英特爾? eASIC N5X通過FPGA中的嵌入式硬件處理器幫助客戶將定制邏輯與設(shè)計遷移到結(jié)構(gòu)化ASIC中,帶來了更低的單位成本,更快的性能和更低的功耗等好處。

2020-11-18 11:26:35 1661

1661 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA模塊化設(shè)計與AlteraHardCopy結(jié)構(gòu)化ASIC。

2021-01-20 17:03:51 6

6 結(jié)構(gòu)化LDPC碼可進(jìn)行相應(yīng)擴(kuò)展通過對編譯碼算法,優(yōu)化編譯碼結(jié)構(gòu)進(jìn)行調(diào)整,降低了編譯碼囂硬件實(shí)現(xiàn)中的關(guān)鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實(shí)現(xiàn)了一個碼長10 240,碼率1/2的非正則結(jié)構(gòu)化LDPC碼編碼器和譯碼器。實(shí)現(xiàn)結(jié)果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 ,其位置分布可以構(gòu)成軌道場景特有的結(jié)構(gòu)化特征,因此設(shè)定了結(jié)構(gòu)化檢測區(qū)域,將一幅圖像中扣件刂日標(biāo)的檢測轉(zhuǎn)化為一整塊具有固定結(jié)構(gòu)的大目標(biāo)區(qū)域檢測,將扣件小目標(biāo)的檢測問題轉(zhuǎn)化為結(jié)構(gòu)化區(qū)域的定位問題,可加快網(wǎng)絡(luò)的訓(xùn)練收斂速度,

2021-04-07 14:00:12 3

3 一種自適應(yīng)網(wǎng)頁結(jié)構(gòu)化信息提取方法介紹說明。

2021-05-08 10:58:07 2

2 FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法(哪些專業(yè)適合嵌入式開發(fā))-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進(jìn)行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 21

21 FPGA在常規(guī)運(yùn)算時不能進(jìn)行浮點(diǎn)運(yùn)算,只能進(jìn)行定點(diǎn)整型運(yùn)算,在處理數(shù)據(jù)的小數(shù)乘加運(yùn)算和除法運(yùn)算時FPGA一般是無能為力的,其中一種常用的處理方法就是數(shù)據(jù)進(jìn)行浮點(diǎn)到定點(diǎn)的轉(zhuǎn)換。

2022-10-13 16:23:50 3752

3752 FPGA和ASIC作為數(shù)字電路的常見實(shí)現(xiàn)方式,其聯(lián)系和區(qū)別備受關(guān)注。本文將從FPGA和ASIC的基本概念入手,深入研究它們的區(qū)別與聯(lián)系,以幫助讀者更好地理解兩者的應(yīng)用場景和選擇方法。

2023-08-14 16:38:51 1583

1583 電源是一種將其它形式的能轉(zhuǎn)化為電能的裝置。 這些其它形式的能包括我們已知的所有能量形式,例如化學(xué)能、機(jī)械能、太陽能等。 電源通過將這些其它形式的能轉(zhuǎn)化為電能,為電子設(shè)備或電路提供所需的電能。 電源

2023-09-14 16:10:53 1905

1905 隨著汽車技術(shù)的飛速發(fā)展,汽車功能的復(fù)雜性對處理芯片的算力及IO端口數(shù)量提出了更高的要求。作為一家正在進(jìn)行IPO排隊(duì)的公司,深圳市科通技術(shù)股份有限公司(以下簡稱:科通技術(shù))積極應(yīng)對市場挑戰(zhàn),針對新一代汽車輔助駕駛的需求,研發(fā)了一系列基于FPGA的應(yīng)用設(shè)計結(jié)構(gòu)化技術(shù)。

2024-02-02 09:34:18 183

183

電子發(fā)燒友App

電子發(fā)燒友App

評論