大家好,歡迎Vivado的一個快速演示,它是xilinx新的設計套件,應用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 感謝你對Vivado HLS也就是XILINX’s 高層次綜合解決方案有興趣,這個解決方案綜合c,c++和系統c代碼成Verilog和VHDL RTL結構。

2012-04-25 08:59:37 2582

2582 在生產力方面進行了兩大改進。Vivado設計套件2013.1版本新增了一款以IP為中心的設計環境,用以加速系統集成;而其提供的一套完整數據庫,則可加速C/C++系統級設計和高層次綜合(HLS)。

2013-04-08 15:08:54 902

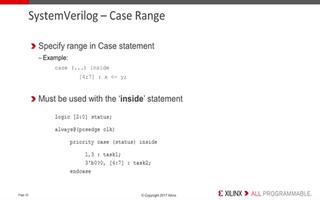

902 作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

3153 關于Zynq的Vivado 2013.1發行說明說:“需要及早訪問Vivado IP集成商”。這是什么意思?它是否真的支持Zynq開箱即用?提前致謝。以上來自于谷歌翻譯以下為原文Vivado

2018-12-04 11:00:58

我在兩臺64位Windows機器上安裝了2013.1,并且兩者都崩潰了。 Vivado 2013.1窗口在崩潰之前會短暫出現。如果我從命令行運行,我會看到:****** Vivado v2013.1

2018-11-27 14:30:08

將Vivado HLS建立的加速器功能集成到Vivado IP集成器中。賽靈思Smarter Vision方案在計算機視覺領域的應用立即觀看視頻回答問卷 參與抽獎觀看視頻并參與問卷調查的聽眾,將參加

2013-12-30 16:09:34

參考:UG973 (v2021.1)圖:賽靈思全新 Vivado? ML 版Vivado 2021.1這個新版本的新增加的一些特:1、在IP這個層面的功能的增強,主要體現在新增加了一個BD...

2021-07-20 07:06:23

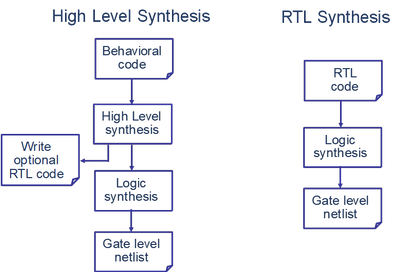

HLS高階綜合(highlevelsynthesis)在被廣泛使用之前,作為商業技術其實已經存在了20多年。設計團隊對于這項技術可以說呈現出兩極化的態度:要么堅信它是先進技術之翹楚,要么對其持謹慎

2021-07-06 08:00:00

。ROHM與安富利公司共同開發賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評估套件Mini-Module Plus 用的電源模塊。安富利公司已經開發出多款賽靈思

2018-12-04 10:02:08

自適應和智能計算的全球領先企業賽靈思公司(Xilinx, Inc.,(NASDAQ:XLNX))今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,從而進一步

2020-11-02 08:34:50

`賽靈思FPGA原理圖例子之s3astarter 賽靈思一向是FPGA領域里的領先者,運用FPGA需要深入的理解它的工作原理,小編親子整理了s3astarter 的經典fpga原理圖分享給電子工程師們。賽靈思FPGA原理圖例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

賽靈思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP數字影院投影儀產品,均采用了賽靈思Virtex?-5 FPGA系列產品。

2019-08-19 07:12:03

每一版本都提供了完整的FPGA設計流程,并且專門針對特定的用戶群體(工程師)和特定領域的設計方法及設計環境要求進行了優化。那大家知道賽靈思ISE? 設計套件11.1版對FPGA有什么優化作用嗎?

2019-07-30 06:52:50

賽靈思Verilog(FPGACPLD)設計小技巧

2012-08-19 22:52:02

賽靈思Virtex-6 HXT FPGA ML630評估套件采用SiTime電子發燒友振具體型號為:SIT9102AI-243N25E200.0000,而目前針對這一型號sitime推出了抖動更低

2014-11-17 15:07:35

賽靈思Zynq-7000可擴展處理平臺(EPP)將雙ARM Cortex-A9 MPCore處理器系統與可編程邏輯和硬IP外設緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

可擴展的處理平臺- 是系統集成、軟件可編程性的靈活性與FPGA 硬件加速的完美結合,支持客戶打造定制和優化的系統。全球第一個支持高層次綜合設計方法的可編程邏輯企業- 其 AutoESL? 高層次綜合

2012-03-22 15:17:12

賽靈思有哪幾種ISE設計套件配置版本 ?

2021-04-30 06:30:50

賽靈思的FPGA用什么開發工具編程,有沒有大佬分享一下安裝包

2018-05-24 17:51:38

賽靈思(XILINX)全新7系列FPGA詳述

2012-08-14 12:20:22

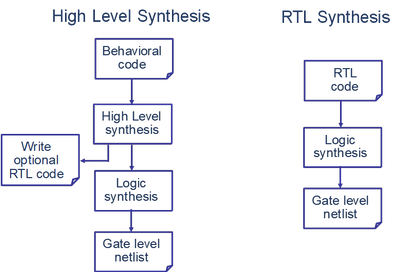

雖然淺顯易懂,但是它將基于CPU的架構的軟件程序與在高層次綜合這項技術上行為描述語言做出了明顯的區分。賽靈思的HLS官方手冊中,對文中提到了端口協議,優化指令,數據類型等都有非常詳細的解釋。本系列以后

2021-01-06 17:52:14

高層次綜合技術原理淺析

2021-02-01 06:04:00

1、HLS最全知識庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD Xilinx而言

2022-09-07 15:21:54

不會使用的軟件和系統工程師們, 現在可以再次把FPGA 開發提到日程上來了, 因為賽靈思在解決“易用性”問題上已經邁出了幾大步,其中包括: 賽靈思 2012 年就發布了 Vivado 設計套件集成環境

2018-08-10 09:16:48

使用的軟件和系統工程師們, 現在可以再次把FPGA 開發提到日程上來了, 因為賽靈思在解決“易用性”問題上已經邁出了幾大步,其中包括:賽靈思 2012 年就發布了 Vivado 設計套件集成環境,大大

2018-08-13 09:31:45

FPGA是用altera多還是賽靈思的多呢,我買的開發板是altera的,但是很多人推薦說學習賽靈思的好

2016-01-09 21:27:25

28nm 架構發布,具有時鐘門控技術、部分重配置技術支持針對目標設計平臺推出ISE11 設計套件領域專用方法賽靈思重要里程碑事件2009年4月2009年10月2010年3月2010年2月2010年5月ISE12設計套件

2012-08-12 12:22:46

賽靈思公司(Xilinx)最新推出的ISE 12軟件設計套件,實現了具有更高設計生產力的功耗和成本的突破性優化。ISE 設計套件首次利用“智能”時鐘門控技術,將動態功耗降低多達 30%。

2019-11-08 08:27:56

賽靈思公司(Xilinx)最新推出的ISE 12軟件設計套件,實現了具有更高設計生產力的功耗和成本的突破性優化。ISE 設計套件首次利用“智能”時鐘門控技術,將動態功耗降低多達 30%。

2019-08-20 08:33:19

Licensing文檔。不存在此類功能。功能:SysGen_TDPLicense路徑:C:/。Xilinx \ Xilinx名為.lic; C:\賽靈思\ 13.1 \ ISE_DS \ ISE

2019-09-06 08:23:25

目錄第1章:高層次生產力設計方法指南第2章:系統設計第3章:shell開發第4章:基于C語言的IP開發第5章:系統集成

2017-12-13 09:50:31

10日發布什么消息? 賽靈思今天宣布推出20nm All Programmable UltraScale?產品系列,并配套提供產品技術文檔和Vivado?設計套件支持。繼2013年11月首款20nm

2013-12-17 11:18:00

` 本帖最后由 MGJOY 于 2017-4-10 15:07 編輯

本周三,4月12日,賽靈思FPGA技術及應用線上公開課。歡迎大家觀看、學習交流~分享主題【賽靈思FPGA人工智能領域技術及應用】嵌入式視覺領域技術和解決方案機器學習方面的技術和解決方案ADAS/自動駕駛方面的應用`

2017-04-10 15:06:16

能做賽靈思方案的,請聯系

2019-01-21 19:31:40

的規劃者。”個人資料顯示,Victor Peng于2008年加入賽靈思,在公司產品線和服務方面引領了行業領先的戰略和技術轉型,實現了從28nm,20nm到16nm連續三代核心產品的領導地位,并在集成

2018-03-23 14:31:40

、應用、后端支持.pdf直播簡介:為了解決FPGA的可編程性問題,實現從算法到RTL設計的快速編譯,我們引入了基于MLIR(多級別中間表示)的高層次綜合框架ScaleHLS,對算法的高層次描述進行多級

2022-11-27 12:43:17

,盡然無法獲取設備分配的IP。而使用Android手機分享的移動熱點盡然可以獲取得到IP,實現正常上網功能。藍牙模塊功能正常投影屏幕打算將芯靈思A83T平板的屏幕投影在WIndows10 筆記本上,能

2017-04-30 17:46:23

Altera和賽靈思20年來都在FPGA這個窄眾市場激烈的競爭者,然而Peter Larson基于對兩個公司現金流折現法的研究表明,賽靈思是目前FPGA市場的絕對領先者。

2019-09-02 06:04:21

今年年初,賽靈思率先在FPGA領域提出目標設計平臺概念,旨在通過選用開放的標準、通用的開發流程以及類似的設計環境,減少通用工作對設計人員時間的占用,確保他們能集中精力從事創新性的開發工作。

2019-08-13 07:27:15

賽靈思 MATLAB & Simulink Add-on插件是將 ModelComposer 和 System Generator forDSP完美結合的統一工具。

2021-01-28 06:33:40

1、使用Vitis HLS創建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD

2022-09-09 16:45:27

哪位大神能提供款賽靈思的捕捉頻率高于400m,LVDS引腳數有130個,初學者請多多指教

2015-08-07 08:58:08

、ACTEL、ALTERA 等IC品牌。(熱線:***,QQ:879821252 同步微信)《《高價收購Xilinx帶板芯片,淘汰廢舊Xilinx帶板芯片高價回收 ,呆滯電子集成電路賽靈思芯片大量收購!《《退

2021-12-17 10:02:19

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

怎么利用賽靈思FGPA實現降采樣FIR濾波器?這種濾波器在軟件無線電與數據采集類應用中都很常見。

2019-08-15 08:21:22

剛開始學賽靈思的FPGA,求他的ISE軟件下載地址,我在網上沒搜到。謝謝了

2012-08-02 09:52:12

電子發燒友網訊:由賽靈思(xilinx)公司和華強PCB網贊助,電子發燒友網主辦的玩轉FPGA,賽靈思設計大賽已經圓滿結束。本活動旨在建立一個FPGA技能展示和技術交流平臺,鼓勵廣大參賽者發揮

2012-09-06 11:52:48

今后也會推出更多的設計大賽服務于廣大的電子工程師及電子愛好者。 附:玩轉FPGA,賽靈思FPGA設計大賽活動頁面 玩轉FPGA,賽靈思FPGA設計大賽參賽作品展示區 大賽官方QQ

2012-09-06 11:54:16

經歷過和牛人一起進行FPGA設計比賽的激烈競爭嗎?你感受過FPGA原廠開發板和fpga行業泰斗直接帶來的強烈震撼嗎? 沒經歷過沒關系,電子發燒友網主辦,賽靈思贊助的“賽靈思FPGA方案開發設計大賽”已經為

2012-04-23 09:31:16

最基本的OpenCV I/O功能都需要加速。為什么需要高層次綜合? 賽靈思推出的Vivado HLS是一款軟件編譯器,旨在將C、C++或SystemC編寫的算法轉變為針對用戶定義時鐘頻率和賽靈思產品

2014-04-21 15:49:33

你好,我有一塊ZC-702板,并使用套件附帶的節點鎖定licese安裝了Vivado。我看到Vivado設計版15.2包含系統生成器。我成功安裝了Vivado。但是,我無法選擇( check)安裝

2018-12-17 11:49:00

詳解賽靈思All Programmable Smarter Vision解決方案

2021-06-02 06:56:12

絲印查不到系列型號,引腳數量也對不上賽靈思所有型號規格,賽靈思也沒有韓國產地

2023-02-24 17:01:32

高端功能提供了平衡優化的配置。更多內容,請點擊以下鏈接下載:全新賽靈思(Xilinx)FPGA 7系列芯片精彩剖析。rar

2012-09-06 16:24:35

) 的靈活可編程 VESADisplayPort v.1.1a 解決方案。該 IP 可隨時提供給賽靈思的客戶,但在用戶展開設計之前,建議先了解與該標準的部分關鍵功能有關的其它背景信息,如olicy Maker

2012-03-01 11:10:18

高價回收賽靈思系列IC長期回收賽靈思系列IC,高價求購賽靈思系列IC。深圳帝歐長期回收ic電子料,帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com。帝歐回收

2021-04-06 18:07:50

)FPGA設計大賽圓滿結束。本活動的獎品由賽靈思和華強PCB合力提供,在此電子發燒友網小編代表電子發燒友網感謝賽靈思公司和華強PCB網的鼎力支持。接下來,我們就一起來見見咱們獲獎者的獎品的強大陣容吧

2012-09-06 14:33:50

利用Mentor高層次綜合技術快速實現復雜DSP算法摘要:為了滿足產品上市時間和功能豐富性的要求,越來越多的先進設計公司開始提高設計的抽象層次進行復雜的D

2010-04-29 14:01:59 34

34 在高層次對系統進行功耗佑算和功耗優化是soc設計的關健技術本文首先給出soc設計的特點和流程,然后綜述目前高層次功耗估算和功耗優化的常用方法和技術,重點論述寄存器傳輸級和

2011-12-27 16:42:38 46

46 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 高層次綜合設計最常見的的使用就是為CPU創建一個加速器,將在CPU中執行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

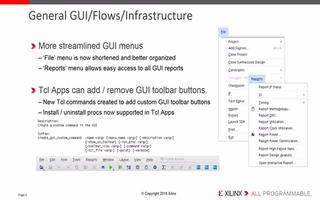

HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE? IP 子系統以及完整的 Vivado 實現工具套件,使主流用戶能夠方便地采用生產力最高、最

2017-02-08 19:35:06 386

386 高層次綜合 (HLS)的增強功能,可實現更大型 IP 構建模塊及相關模塊的復用,從而有助于加快集成和驗證速度,進

2017-02-09 01:15:42 225

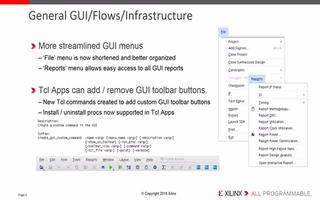

225 Vivado?? 設計套件快速入門視頻輔導資料為您提高生產力提供了實時的特定功能和流程培訓。新主題包括: . ?? 使用 ?System Generator for DSP? 和 ?IP

2017-02-09 02:22:12 256

256 ? 無縫集成在其設計中的工作。該 ?IP? 集成工具支持針對所有 ?Xilinx? 器件提供,其中包括最新 ?UltraScale? 器件系列,可充分滿足 ?Vivado? 設計套件工具 ?2014.4? 以及更高版本的要求。 了解更多 ??

2017-02-09 08:12:36 319

319

,有助于應對這種挑戰。 我們使用 Vivado? Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號

2017-11-16 20:05:41 1918

1918

理由一:突破器件密度極限:在單個器件中更快速集成更多功能;理由二:Vivado以可預測的結果提供穩健可靠的性能和低功耗;理由三:Vivado設計套件提供了無與倫比的運行時間和存儲器利用率;理由四:使用Vivado高層次綜合生成基于C語言的IP。

2017-11-22 08:15:19 1421

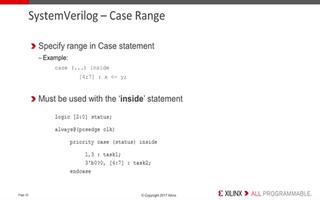

1421 Vivado HLS配合C語言等高級語言能幫助您在FPGA上快速實現算法。 高層次綜合(HLS)是指自動綜合最初用C、C++或SystemC語言描述的數字設計。工程師之所以對高層次綜合如此感興趣,不僅是因為它能讓工程師在較高的抽象層面上工作,而且還因為它能方便地生成多種設計解決方案。

2019-10-06 10:44:00 1178

1178

我們使用 Vivado ?Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號保真度的影響、造成的時延及其實現成本。我們發現賽靈思的 Vivado HLS 平臺能夠高效評估和實現所選壓縮算法。

2018-07-24 09:30:00 1901

1901

、HL 設計版本和 HL WebPACK 版本。所有 HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE IP

2018-08-17 11:43:00 2677

2677 All Programmable SoC 的生產力帶來重大突破。伴隨此款最新版Vivado 設計套件推出的還包括其內含的 Vivado 高層次綜合(HLS)和IP集成器的增強功能,以及最新性能監控

2018-09-06 16:07:00 1466

1466 達25%,性能提升5%。此外,2014.1版本還在Vivado HLS(高層次綜合)中新增了OpenCL內核硬件加速功能。

2018-09-13 16:59:00 1199

1199 本視頻重點向您介紹了Vivado設計套件2017.3版本中的增強功能,包括操作系統和器件支持,高級增強功能,加速集成,實施和驗證的各種升級和改進。歡迎收看本視頻,了解更多有關

Vivado設計套件的新功能。

2018-11-21 06:15:00 3374

3374

本視頻重點介紹了Vivado設計套件2018.1版本中的新增功能,包括對操作系統以及器件的支持情況,還有高層次增強功能,以及各種功能改進以加速設計集成,實現和驗證的過程。

2018-11-20 06:28:00 2254

2254

12月23日,據杭州市人力資源和社會保障局消息,阿里巴巴蔣凡被認定為蔣凡被認定為高層次人才,消息曝光后引發網友熱議。

2020-12-30 11:12:34 1969

1969 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述

2021-01-14 09:27:28 1848

1848 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2022-02-08 17:26:42 7041

7041

本文介紹如何在 vivado 開發教程(一) 創建新工程 的基礎上, 使用IP集成器, 創建塊設計。

2022-02-08 10:47:39 2090

2090

說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2021-01-28 09:11:08 3

3 1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-06 09:20:58 6

6 01 演講題目 ? 開源硬件系列02期: 從PyTorch到RTL - 基于MLIR的高層次綜合技術 02 演講時間 ? 2022年11月27日 上午?10:00 03 內容簡介 ? 為了解

2022-11-24 08:15:03 1379

1379 英特爾? NUC 8 支持更高層次的設計

2022-12-29 10:02:52 619

619

電子發燒友網站提供《UltraFast高層次生產力設計方法指南.pdf》資料免費下載

2023-09-15 10:41:47 0

0 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0

電子發燒友App

電子發燒友App

評論