人工神經網絡在智能控制、模式識別、圖像處理等領域中應用廣泛。在進行神經網絡的應用研究時,人們可以將神經網絡模型或算法在通用的計算機上軟件編程實現,但很多時間浪費在分析指令、讀出寫入數據等,其實現效率并不高。軟件實現的缺點是并行程度較低,因此利用軟件實現神經網絡的方法無法滿足某些對數據實時處理要求較高的場合(如工業控制等領域)。

目前實現大規模、實時性要求高的神經網絡,傳統的軟件算法實現方法顯示出其難以滿足速度等要求的不足。此外,在構建神經網絡時必然需要考慮硬件實現問題。由于神經網絡具有并行計算的特點和功能,可以有效發掘算法本身的并行特性,提出高效的硬件電路結構,從而完成神經網絡的硬件實現。

脈沖耦合神經網絡(Pulse Coupled Neural Network,PCNN)是新一代的神經網絡,在研究貓等哺乳動物的視覺神經元時,根據其脈沖同步發放的工作原理所提出的。目前,P CNN理論仍在發展中,由于其獨特的并行性能,在圖像分割與平滑、邊緣檢測與細化、決策與優化等領域應用廣泛。當前的研究重點在于模型的優化和軟件的實現,而相關的硬件實現在國內并不多見,PCNN并行結構的特性為硬件實現提供了可能。

1 PCNN的基本原理

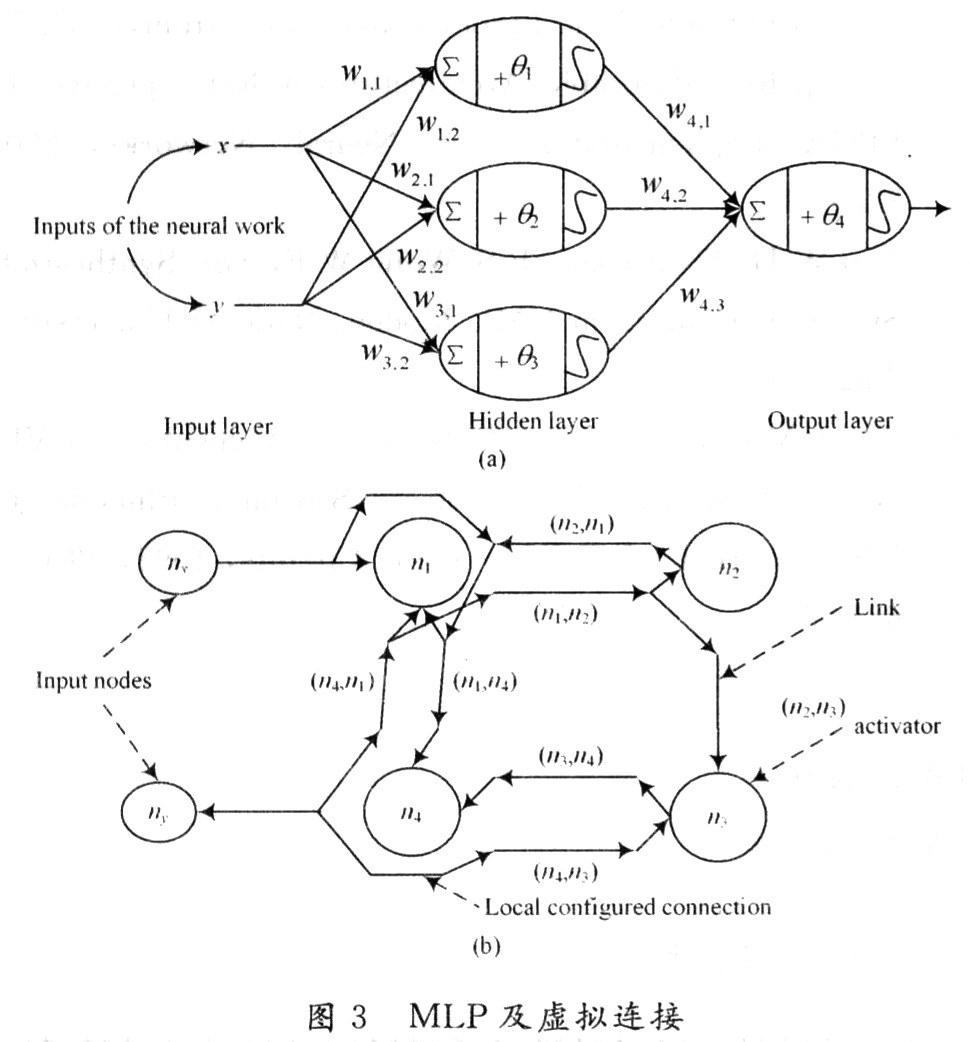

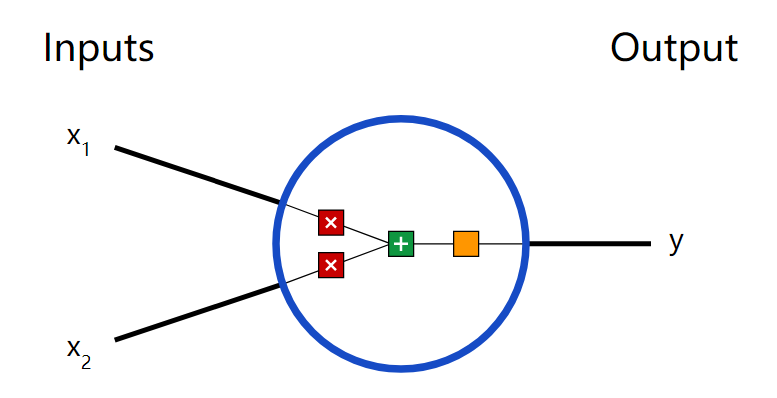

脈沖耦合神經網絡是一種單層模式的兩維神經網絡,它的基本單元是脈沖耦合網絡的神經元。圖1為PCNN的單個神經元模型框圖,它由輸入部分、連接調制部分、脈沖發生器部分3部分構成。

輸入部分即接收域,其接收信號來源有兩部分:鄰近神經元產生的信號和外部的輸入激勵。這兩部分信號通過兩個不同的路徑進行傳遞,其中一個路徑傳遞反饋輸入信號,其包含外部輸入激勵,該路徑即為F路徑;另一個路徑傳遞連接輸入信號,其包含來自鄰近神經元產生的信號,該路徑即為L路徑。

連接調制部分完成上述兩個路徑信號的耦合,經過一定的信號處理,產生神經元的內部活動項。該信號處理需要首先通過一個正的單位偏置和L路徑的連接輸入信號的累加,然后與F路徑的反饋輸入信號完成相乘調制。該神經元的內部活動項即為信號經調制得到的乘積結果。

脈沖發生器和閾值大小變化的比較器構成PCNN單個神經元的脈沖發生部分。如果達到脈沖發放條件,則該脈沖發生器起作用,發出一個頻率恒定不變的脈沖,此時神經元處于點火狀態。

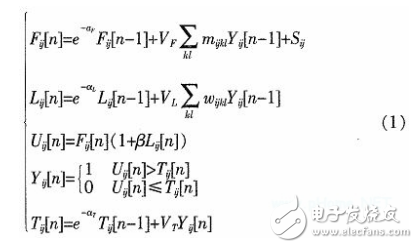

根據圖1模型,每個神經元按照公式(1)完成迭代運算,實現上述PCNN的功能。

式(1)中,Fij[n]是某個神經元的第n次反饋輸入信號;αF與αL表示迭代時間常數;Sij表示外部輸入常數,在圖像處理時即為像素矩陣中像素的灰度值;Lij[n]是神經元的線性輸入項;wijkl與mijkl表示突觸間聯接權值系數;Uij[n]是神經元的內部活動項;Tij[n]是Uij[n]是否激發生成脈沖的動態閾值;β是神經元突觸間的連接強度系數;Yij[n]為PCNN的脈沖輸出項。由于信號Lij[n]比信號Fij[n]變化快,經過相乘調制的信號Uij[n]就等同于把一個快速變化的信號加在一個近似不變的信號上。

如果某個神經元點火,即發出一個脈沖信號,那么由于內部活動項大于當前的門限閾值,下一次迭代運算后閾值將通過其時間常數αT和幅度系數VT突然變大。而此時迭代后的閾值Tij[n]遠大于Uij[n],因此神經元將被抑制,脈沖信號停止輸出,即處于未點火狀態。在這一狀態下,周圍神經元不斷點火,產生響應的脈沖信號,通過L路徑的輸入提高內部活動項,與此同時閾值經指數運算不斷較小。在某一次迭代時,當前閾值將再次小于Uij[n],此時神經元將被激活,脈沖信號開始輸出,即神經元再次被點火。如此周而復始,不用神經元在點火和為點火狀態進行切換,從而實現脈沖同步激發。

2 系統硬件實現

2.1 PCNN模型的改進

對于上述PCNN模型結構,在圖像處理等應用中仍存在一定的局限性:

1)PCNN涉及到的參數較多,增加了數學運算的難度,實現算法比較困難;

2)網絡參數確定較為困難。

此外,為了易于FPGA實現。把標準的PCNN進行一定的簡化和改進。將反饋輸入只當做對應象素的灰度值強度,所以F路徑的連接權值矩陣M為零。改進后的第一個優點是減少了迭代的時間,而迭代的質量仍與標準PCNN模型接近,第二個優點是節約了FPGA資源的利用。改進模型的數學表達式與標準模型相似,只是饋送域不同。饋送域表達式為:

Fij[n]=Sij (2)

2.2 小數的定點表示方法

由于Vetilog無法直接定義小數類型,所以采用小數的定點表示法表示小數。考慮到灰度值為8位二進制數據,故小數的表示形式為《8.8》,即整數位數和小數位數都為8位,整數的表示形式為《8.0》,即整數位數為8位,小數位數為0位。由于并沒有存儲小數的位置信息,所以需要根據先前的約定對最后的結果進行截取。如式(3)所示,最后的運算結果為24位,低8位為小數部分,而利用Verilog的位操作運算截取中間8位即為更新后的灰度值。

《8.8》*《8.0》+《8.8》*《8.0》=《16.8》 (3)

2.3 PCNN參數選擇

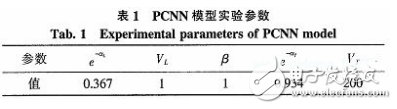

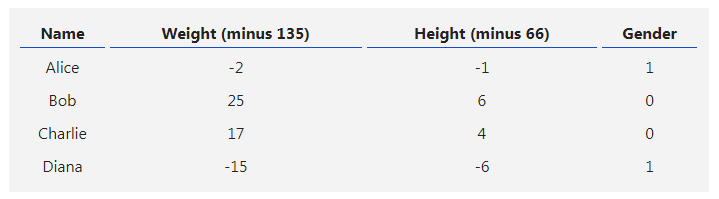

利用2.1節介紹的PCNN改進模型,描述單個神經元的PCNN算法。表1為本設計方案PCNN模型參數的經驗設定,其閾值衰減設為每次運算后閾值的約0.9倍。為使算法利于硬件實現,實驗中將設定神經元連接強度β=1,連接域增益VL=1。

其連接域鄰域矩陣為:

2.4 系統整體設計框圖

在進行圖像處理時,需要把神經元與像素一一對應,神經網絡的大小取決于圖像的大小。如果需要處理的圖像體積較大,那么硬件資源將被大量占用,繼而需要更高規格的FPGA芯片來實現。本文介紹一個簡單的PCNN硬件系統,可以處理3×3、8位的灰度圖像。

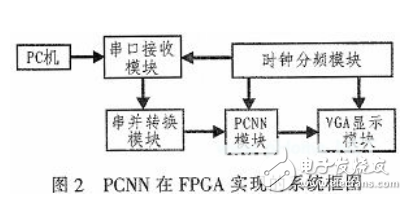

PCNN在FPGA實現的系統框圖如圖2所示。系統分為5個主要的功能模塊:時鐘分頻模塊、串口接收模塊、串并轉換模塊、PCNN模塊和VGA顯示模塊。圖中除PC機部分都在FPGA上實現。PC機包含上位機串口通信軟件,常見的有VB串口通信助手、串口大師等,可實現串口的調試、測試、監控和過濾等功能。

系統需要完成的工作分為三大部分:圖像的輸入、圖像的處理和圖像的顯示輸出。系統詳細的工作過程描述如下:PC機通過串口軟件(如串口大師)發送圖像數據,串口接收模塊接收圖像數據并通過模塊內部的FIFO存儲數據;串并轉換模塊將串口接收模塊存儲的圖像數據并行輸出給PCNN模塊,等待處理;PCNN模塊接收到圖像數據后,開始進行迭代,并輸出給VGA顯示模塊;VGA顯示模塊負責顯示圖像經PCNN模塊處理后的二值序列,以觀察PCNN的處理效果。由于本實驗采用的FPGA實驗平臺提供的時鐘頻率為50 MHz,而串口接收模塊、PCNN模塊和VGA顯示模塊需要特定的時鐘頻率才能工作,所以必須設計時鐘分頻模塊以產生滿足要求的時鐘頻率。

3 系統仿真

由于考慮邊緣神經元的特殊情況,設計了3種略有差異的神經元,即周圍神經元輸入分別為2、3和4的神經元。這里僅選取4輸入的PCNN神經元進行仿真,神經元的閾值為200以驗證神經元功能的正確性。通過選取了4個典型的圖像灰度值S輸入,分別為4、100、200和250,經仿真驗證了單個神經元的正確性。

利用單個PCNN神經元,構建了包含9個PCNN神經元PCNN模塊,能處理3×3大小的圖像,通過網絡迭代,得到理想的圖像。通過串口輸入數據:181、187、140、120、120、4、46、83、120,對PCNN模塊進行了仿真。為了便于觀察,選取其中3個神經元的時序仿真結果,如圖3所示。由圖3知,PCNN輸出呈現0和1的不斷變化,且能看出3個神經元中由于耦合效應產生了不同的結果。圖3中S1~S3為9個像素灰度值的3個輸入,Y1~Y3為圖像經PCNN處理后3個二值序列值。

4 系統驗證與分析

本實驗以Altera Cyclone II開發平臺為驗證環境,選用Cyclone系列中的EP2C35F672芯片。利用串口軟件發送網像數據,FPGA經PCNN處理后將二值結果顯示在VGA顯示器上。PCNN模塊的時鐘輸入頻率為100MHz,VGA顯示模塊的時鐘輸入頻率為25 MHz。對于波特率,考慮到已經完成的串口接收模塊,選取波特率115 200 bps,以匹配串口接收模塊

的采樣頻率。數據位有8位,無檢驗位,包含1位停止位,傳輸數據以16進制的形式進行發送。

為了便于觀察,考慮到顯示器的刷新頻率和人眼的視覺暫留,將PCNN網絡的迭代處理頻率設定為1 Hz,即顯示器每1秒顯示一次迭代效果圖。圖4為顯示器前40次的顯示效果。圖中九宮格代表要處理的3×3輸出圖像,一個方格代表一個像素點。九宮格中灰色方框神經元點火,即輸出為“1”。黑色方框代表神經元未點火,即輸出為“0”。

據實驗平臺的測試結果,與除去VGA模塊的硬件模塊ModelSim仿真結果進行了對比。圖5為除去VGA模塊的硬件模塊的功能仿真圖。圖中高電平代表“1”,低電平代表“0”。

果完全符合,這也驗證了PCNN網絡硬件實現的正確性。此外,由圖4和圖5看出,神經元1、2、3、4、5、8、9在幾次迭代后輸出始終為“1”,這是由于神經元的內部活動項始終大于閾值。而由于神經元6和7的圖像輸入值較小,內部活動項部分和閾值部分不斷變化,使得在周圍神經元的作用下,呈現周期性的“0”和“1”輸出。

5 結論

本文根據脈沖耦合神經網絡具有并行計算的特點,提出了一種基于FPGA的神經網絡硬件實現方案。利用Verilog硬件描述語言完成了系統模塊的設計,構建的PCNN神經網絡

在FPGA開發平臺上進行了驗證。通過處理簡單的3x3圖像,并觀察VGA顯示結果,完成了PCNN的FPGA實現,達到了設計要求,圖像處理實時性較好。下一步將研究構建更復雜的PCNN網絡結構,以處理更大的圖像數據。

電子發燒友App

電子發燒友App

評論