的波形驗證,存儲器的加入會使設(shè)計的資源變大,初步驗證時需使用比預(yù)計的容量大的器件。在程序的初步驗證之后,就可以在預(yù)定的器件中進(jìn)行編譯配置,然后進(jìn)行進(jìn)一步的調(diào)試。程序設(shè)計如圖2所示,程序設(shè)計大致分為四個模塊

2018-12-18 09:51:38

)是兩種不同的硬件實現(xiàn)方式。

FPGA是一種可編程邏輯器件,其內(nèi)部資源可以根據(jù)需要進(jìn)行配置和重新配置。這些資源包括但不限于:

邏輯單元(Logic Cells):這些是FPGA的核心計算資源,可以實現(xiàn)各種

2024-02-22 09:52:22

。而FPGA的編程信息需存放在外部存儲器上,使用方法復(fù)雜。⑥CPLD的速度比FPGA快,并且具有較大的時間可預(yù)測性。這是由于FPGA是門級編程,并且CLB之間采用分布式互聯(lián),而CPLD是邏輯塊級編程

2012-10-26 08:10:36

memory)和UFM塊(user flash memory),其實altera的這款CPLD器件和FPGA器件一樣是基于SRAM的,只是其內(nèi)部嵌入了一塊用于存儲配置數(shù)據(jù)流的flash存儲器,即

2015-01-27 11:43:10

在線調(diào)試方式大都是通過FPGA器件引出的JTAG接口,同時使用了一些FPGA片內(nèi)固有的邏輯、存儲器或布線資源就能夠?qū)崿F(xiàn)的。這些調(diào)試功能通常也只需要隨著用戶設(shè)計所生產(chǎn)的配置文件一同下載到目標(biāo)FPGA器件中

2015-09-02 18:39:49

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個單元簡介如下: 1.

2016-10-08 14:43:50

的FPGACyclone III LS器件具有200K邏輯單元、8 Mbits嵌入式存儲器以及396個嵌入式乘法器,是高性能處理、低功耗應(yīng)用的理想選擇,包括:●汽車●消費類●顯示●工業(yè)●視頻和圖像處理●無線具有

2019-04-15 02:21:50

設(shè)計和驗證工程師當(dāng)今面臨的最大挑戰(zhàn)之一是時間和資源制約。隨著FPGA在速度、密度和復(fù)雜性方面的增加,為完成一個完整時序驗證,不僅對人力也對計算機(jī)處理器和存儲器提出了更多更高的要求。另外,對設(shè)計和驗證

2019-07-16 08:10:25

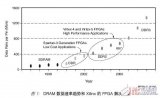

各位大神好,我想用FPGA讀寫DRAM存儲器,求大神指點哪位大佬有代碼分析一份更是感激不盡,好人一生平安。

2018-01-14 15:31:32

的邏輯是通過向內(nèi)部靜態(tài)存儲單元加載編程數(shù)據(jù)來實現(xiàn)的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實現(xiàn)的功能,FPGA允許無限次的編程。圖

2023-02-23 15:24:55

存儲器重映射。1、存儲區(qū)域功能規(guī)劃:在這 4GB 的地址空間中,ARM 已經(jīng)粗線條的平均分成了 8 個塊,每塊 512MB,每個塊也都規(guī)定了用途,具體分類見表格 5-1。每個塊的大小都有 512MB

2021-08-20 06:29:52

, 每塊區(qū)域的大小是 512MB(1)Block0 內(nèi)部區(qū)域功能劃分Block0 主要用于設(shè)計片內(nèi)的 FLASH,0x0000 0000-0x0007FFFF:取決于 BOOT 引腳,為 FLASH、系統(tǒng)存儲器、 SRAM 的別名。0x08000000-0x0807FFFF:片內(nèi) FLASH,我們編寫.

2022-01-20 08:21:34

擦除,擦除后又可重新寫入新的程序。 4、可電改寫只讀存儲器(EEPROM): EEPROM可用電的方法寫入和清除其內(nèi)容,其編程電壓和清除電壓均與微機(jī)CPU的5V工作電壓相同,不需另加電壓。它既有

2017-12-21 17:10:53

,擦除后又可重新寫入新的程序。 4、可電改寫只讀存儲器(EEPROM): EEPROM可用電的方法寫入和清除其內(nèi)容,其編程電壓和清除電壓均與微機(jī)CPU的5V工作電壓相同,不需另加電壓。它既有

2017-10-24 14:31:49

區(qū)域,這3個塊可用于擴(kuò)展外部存儲器,比如 SRAM,NORFLASH 和 NANDFLASH 等Block2 這片區(qū)域是用來設(shè)計片上外設(shè)的片上外設(shè)區(qū)分為四條總線,根據(jù)外設(shè)速度的不同,不同總線掛載著

2021-01-14 17:37:08

存儲器的理解存儲器是由簡單的電子器件例如PMOS管、NMOS管進(jìn)行組合形成邏輯上的與非或門,之后在此基礎(chǔ)上,形成組合邏輯用于存儲信息,例如R-S鎖存器和門控D鎖存器,進(jìn)而進(jìn)一步組合復(fù)雜化,形成我們

2021-12-10 06:54:11

一種存儲器的編碼方法,應(yīng)用于包含存儲器的裝置,存儲器中包含第一存儲體、第二存儲體和第三存儲體,包括:獲取存儲器的帶寬信息;依據(jù)帶寬信息選取編碼操作的操作時機(jī);在到達(dá)操作時機(jī)時,檢測針對第一存儲體

2019-11-15 15:44:06

~D0直到最后一個塊擦除(4K)A9HA15~A8A7~A0--芯片擦除(32K)AEH----讀器件IDAFH偽字節(jié)偽字節(jié)(M7~M0)(ID7~ID0)4 功能模塊設(shè)計4.1 鐵電(FRAM)存儲器

2019-06-12 05:00:08

利用芯片內(nèi)的存儲器,因此我們要知道存儲器的地址,即物理地址,所以虛擬地址和物理地址之間必然存在一定的轉(zhuǎn)換關(guān)系,這就是映射。把虛擬地址按照某種規(guī)則轉(zhuǎn)換成物理地址的方法就為存儲器映射。物理地址表示了被訪問

2014-03-24 11:57:18

庫的慢-慢工藝點對塊進(jìn)行合成,以200 MHz的目標(biāo)速度確認(rèn)時序特性。

接口存儲器端口上的信號符合RAM編譯器為TSMC CL013G工藝技術(shù)生產(chǎn)的單端口同步存儲器組件所要求的時序要求

2023-08-21 06:55:33

/數(shù)據(jù)RAM,即可以作為程序存儲器也可以作為數(shù)據(jù)存儲器。如果用戶程序代碼大,則可以自由使用的數(shù)據(jù)RAM就少。也就是說如果單純使用CY7C68013A片內(nèi)的資源,那么程序最大16KB,數(shù)據(jù)存儲器就為0了

2015-06-21 00:51:54

Cyclone? IV 器件具有嵌入式存儲器結(jié)構(gòu),滿足了 Altera? Cyclone IV 器件設(shè)計對片上存儲器的需求。嵌入式存儲器結(jié)構(gòu)由一列列 M9K 存儲器模塊組成,通過對這些 M9K 存儲器模塊進(jìn)行配置,可以實現(xiàn)各種存儲器功能,例如:RAM、移位寄存器、 ROM 以及FIFO 緩沖器。

2017-11-13 12:09:48

本章節(jié)介紹了 Cyclone? IV 器件的存儲器接口管腳的支持以及外部存儲器接口的特性。除了大量供應(yīng)的片上存儲器,Cyclone IV 器件可以很容易地與各種外部存儲器件建立連接,其中包括

2017-11-14 10:12:11

提供足夠的帶寬。視頻處理設(shè)計說明我們的目標(biāo)視頻處理設(shè)計將同時處理四個視頻源,將視頻數(shù)據(jù)轉(zhuǎn)換和壓縮為一種可以通過PCI Express接口傳輸?shù)?b class="flag-6" style="color: red">存儲器hub的格式。系統(tǒng)的主要功能塊如圖1所示。圖1

2019-05-24 05:00:34

通過多內(nèi)核共享存儲器控制器 (MSMC) 連接的內(nèi)部和外部存儲器組成。MSMC 允許CorePac動態(tài)地分享程序和數(shù)據(jù)的內(nèi)外部存儲器。圖 1 - KeyStone 器件方框圖

2011-08-13 15:45:42

存儲器單元發(fā)生異常,數(shù)據(jù)也可以復(fù)原。另外,作為擦除的單位,即一塊 16 頁(轉(zhuǎn)變?yōu)閿?shù)據(jù)大小就是 512 字節(jié)×16=8K)最好與主機(jī)端的文件管理單位一致。當(dāng)讀者看到特點⑥,即和普通存儲器器件特點相同的最后

2018-04-11 10:11:54

從三個層面認(rèn)識SRAM存儲器

2021-01-05 07:09:10

第一部分、章節(jié)目錄3.2.1.STM32的存儲器映像13.2.2.STM32的存儲器映像23.2.3.STM32的位帶操作詳解3.2.4.STM32的啟動模式3.2.5.STM32的電源管理系統(tǒng)

2021-12-30 08:11:20

中。一個字里的最低地址字節(jié)被認(rèn)為是該字的最低有效字節(jié),而最高地址字節(jié)是最高有效字節(jié)。可訪問的存儲器空間被分成8個主要塊,每個塊為512MB。其他所有沒有分配給片上存儲器和外設(shè)的存儲器空間都是保留的地址空間。1. FLASHFlash主存儲區(qū)從0x0800 0000地址開始,不同系列器件有不同大小,這里

2021-08-02 06:06:32

的FLASH分成兩部分:主存儲塊、信息塊。 主存儲塊用于存儲程序,我們寫的程序一般存儲在這里。 信息塊又分成兩部分:系統(tǒng)存儲器、選項字節(jié)。系統(tǒng)存儲器存儲用于存放在系統(tǒng)存儲器自舉模式下的啟動程序

2015-11-23 17:03:47

怎樣去操作STM32的片內(nèi)FLASH呢?STM32片內(nèi)FLASH的主存儲塊有哪些功能?

2021-11-02 08:14:48

【朱老師課程總結(jié) 侵刪】第一部分、章節(jié)目錄3.2.1.STM32的存儲器映像3.2.2.STM32的位帶操作詳解3.2.3.STM32的啟動模式3.2.4.STM32的電源管理系統(tǒng)3.2.5.復(fù)位

2021-08-20 06:06:01

項目名稱:基于FPGA的數(shù)字電路實驗驗證平臺應(yīng)用領(lǐng)域:高校的數(shù)字電路實驗課程中實驗結(jié)果驗證與分析參賽計劃:一、設(shè)計思路:在高校的數(shù)字電路課程中,要通過在FPGA器件上通過設(shè)計一些簡單的時序或者組合

2021-05-12 18:13:29

嵌入式塊 RAM(BRAM)大多數(shù) FPGA 都具有內(nèi)嵌的塊RAM,這大大拓展了FPGA 的應(yīng)用范圍和靈活性。塊RAM 可被配置為單端口RAM、雙端口RAM、內(nèi)容地址存儲器(CAM)以及FIFO 等

2012-03-08 11:03:49

和模型生成783.18.3 計數(shù)器中操作符實現(xiàn)和模型生成793.18.4 比較器中操作符實現(xiàn)和模型生成803.18.5 編碼器和解碼器中操作符實現(xiàn)和模型生成803.19 存儲器實現(xiàn)803.19.1 塊

2012-04-24 09:18:46

這個是譯碼法來選擇片外的存儲器,用三根線可以選擇8個8KB的片外存儲器(8*8=64KB),但是要是把64KB的存儲地址分配給4KB的存儲器,為什么需要4根高位地址線,求專家詳解

2018-12-18 14:38:17

寄存器。我明白他們的角色是什么。但數(shù)據(jù)表僅為存儲器的輸出端口提供了這些選項。為什么塊存儲器沒有Din(輸入)的原始輸出寄存器或核心輸出寄存器?

2020-05-25 07:51:03

半導(dǎo)體存儲器是指通過對半導(dǎo)體電路加以電氣控制,使其具備數(shù)據(jù)存儲保持功能的半導(dǎo)體電路裝置。與磁盤和光盤裝置等相比,具有數(shù)據(jù)讀寫快存儲密度高耗電量少耐震等特點。關(guān)閉電源后存儲內(nèi)容會丟失的存儲器稱作易失

2019-04-21 22:57:08

本文檔適用于STM32F1系列微控制器。介紹了外部EEPROM和嵌入式Flash存儲器之間的不同,描述了使用STM32F10x片內(nèi)的Flash存儲器實現(xiàn)軟件模擬EEPROM的方法。

2022-12-01 06:16:17

使用的特定FPGA器件決定,如Cyclone II系列有低至15KB存儲量的器件,Stratix III系列卻有高到2MB存儲量的器件。因為多數(shù)片內(nèi)存儲器都是易失性的,它在斷電后丟失數(shù)據(jù)。然而,某些片

2016-10-10 17:08:22

使用的Cyclone IV系列FPGA器件內(nèi)嵌豐富的M9K存儲器,M9K存儲器支持以下特性。● 每個M9K存儲塊有8192 bits的存儲量。● 每個端口擁有獨立的讀使能和寫使能信號。● 可變的端口配置

2016-10-12 17:18:25

復(fù)雜可編程邏輯器件—FPGA技術(shù)在近幾年的電子設(shè)計中應(yīng)用越來越廣泛。FPGA具有的硬件邏輯可編程性、大容量、高速、內(nèi)嵌存儲陣列等特點使其特別適合于高速數(shù)據(jù)采集、復(fù)雜控制邏輯、精確時序邏輯等場合的應(yīng)用。而應(yīng)用FPGA中的存儲功能目前還是一個較新的技術(shù)。

2019-10-12 07:32:24

,以保證在源時鐘和用于捕捉數(shù)據(jù)的時鐘間具有固定的相移或延時。該方法的一個明顯缺點是延時是固定的單一值,且在整個設(shè)計周期是預(yù)先設(shè)定好的。但在實際系統(tǒng)中,由到不同存儲器器件的不同布線、FPGA間的變異以及

2019-04-29 07:00:06

提供足夠的帶寬。視頻處理設(shè)計說明我們的目標(biāo)視頻處理設(shè)計將同時處理四個視頻源,將視頻數(shù)據(jù)轉(zhuǎn)換和壓縮為一種可以通過PCI Express接口傳輸?shù)?b class="flag-6" style="color: red">存儲器hub的格式。系統(tǒng)的主要功能塊如圖1所示。圖1

2019-05-27 05:00:02

數(shù)據(jù)通過處理器由存儲器讀寫到存儲器的設(shè)計方法,并在cyclone EP1C120240C8的FPGA上進(jìn)行了結(jié)果驗證,因此,用戶可根據(jù)實際需要采用此方法將外設(shè)接入Avalon總線,并構(gòu)建SOPC系統(tǒng)。

2018-12-07 10:27:46

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

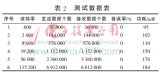

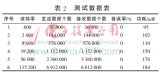

作者:王烈洋 黃小虎 占連樣 珠海歐比特控制工程股份有限公司隨著電子技術(shù)的飛速發(fā)展, 存儲器的種類日益繁多,每一種存儲器都有其獨有的操作時序,為了提高存儲器芯片的測試效率,一種多功能存儲器芯片

2019-07-26 06:53:39

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

Flash類型與技術(shù)特點有哪些?如何去選擇uClinux的塊驅(qū)動器?如何去設(shè)計Flash存儲器?

2021-04-27 06:20:01

/383681#M3607我要將數(shù)據(jù)矩陣存儲在fpga而不是LUT的塊存儲器中作為內(nèi)存!因為基于我編寫的代碼中的上述鏈接,它使用LUT作為內(nèi)存而不是fpga的塊內(nèi)存。所以它的容量很低.....我需要更多的空間來存儲像素數(shù)據(jù)。能否指導(dǎo)我如何在塊存儲器中寫入和讀取矩陣?謝謝

2019-11-07 07:30:54

本文介紹了一種0.13微米CMOS T藝下FPGA中嵌入式存儲器模塊的設(shè)計與實現(xiàn)。

2021-04-09 06:02:09

。然而,現(xiàn)在新一代中檔的FPGA提供這些塊、高速FPGA架構(gòu)、時鐘管理資源和需要實現(xiàn)下一代DDR3控制器的I/O結(jié)構(gòu)。那么,究竟怎么做,才能用中檔FPGA實現(xiàn)高速DDR3存儲器控制器呢?

2019-08-09 07:42:01

如何用低成本FPGA解決高速存儲器接口挑戰(zhàn)?

2021-04-29 06:59:22

隨著集成電路制造工藝水平的提高,半導(dǎo)體芯片上可以集成更多的功能,為了讓產(chǎn)品有別于競爭對手的產(chǎn)品特性,在ASIC上集成存儲器可以降低成本和功耗、改善性能、增加系統(tǒng)級芯片的可靠性。隨著對嵌入式存儲器需求的持續(xù)增長,其復(fù)雜性、密度和速度也日益增加,從而需要提出一種專用存儲器設(shè)計方法。

2019-11-01 07:01:17

領(lǐng)導(dǎo)的存儲器研究小組提出了一種通過增強功能層薄膜中的局域電場來控制導(dǎo)電細(xì)絲的生長位置和方向的方法。通過控制導(dǎo)電細(xì)絲的生長過程,從本質(zhì)上減小導(dǎo)電細(xì)絲生長的隨機(jī)性,從而減小ReRAM器件轉(zhuǎn)變參數(shù)離散性

2010-12-29 15:13:32

包括單粒子翻轉(zhuǎn)(SEU)、單粒子閂鎖(SEL)和單粒子燒毀(SEB)等三種類型,其中以SEU最為常見。在各種輻射效應(yīng)當(dāng)中,存儲器對SEU最為敏感,所以,對存儲器的抗輻射設(shè)計首先要考慮的就是抗SEU設(shè)計。

2019-08-22 07:09:17

是很簡單的器件,僅限于完成單一任務(wù),即收集指紋數(shù)據(jù),然后主芯片中運行的軟件利用這些指紋數(shù)據(jù)驗證用戶身份。 軟件執(zhí)行的功能包括:識別指紋特征、建立安全的生物識別資源(指紋模板)、存儲指紋模板,以及對最新建

2018-11-08 15:28:54

地址0開始讀取SPI Flash存儲器陣列,直到讀完所需的配置位數(shù)。如果從存儲器件讀取到有效比特流,則發(fā)DONE信號,以指示FPGA配置成功。圖1為SPI配置方式的時序。 圖2是AT45DB161D

2020-05-02 07:00:00

存儲器可分為哪幾類?存儲器有哪些特點?存儲器有哪些功能?

2021-10-20 06:46:21

為什么要開發(fā)和測試存儲器件?怎樣去測試存儲器的基本功能?如何去擴(kuò)展存儲器的測試能力?

2021-04-15 06:44:19

數(shù)據(jù)存儲器 FLASH程序存儲器 FLASH數(shù)據(jù)存儲器 片內(nèi)RAM數(shù)據(jù)存儲器16M字節(jié)外部數(shù)據(jù)存儲器各有什么區(qū)別?特點?小弟看到這段 很暈。ADuC812的用戶數(shù)據(jù)存儲器包含三部分,片內(nèi)640字節(jié)的FLASH數(shù)據(jù)存儲器、256字節(jié)的RAM以及片外可擴(kuò)展到16M字節(jié)的數(shù)據(jù)存儲器。求助高手。解釋一下不同。

2011-11-29 09:50:46

單片機(jī)中數(shù)據(jù)存儲器片內(nèi)的地址是00--7FH,程序存儲器的片內(nèi)地址是0000H--0FFFH,請問這兩部分是不是有重疊?請具體詳解!~{:1:}

2013-01-15 09:01:22

虛擬存儲器具有哪些功能呢?虛擬存儲器的特征有哪些呢?

2021-12-23 09:04:39

PIC24設(shè)備,它不能像某些PIC32那樣跳轉(zhuǎn)到數(shù)據(jù)存儲器(RAM)開始從那里執(zhí)行。具有擴(kuò)展程序存儲器接口,所以我們可以把功能代碼轉(zhuǎn)移到擴(kuò)展存儲器,然后跳轉(zhuǎn)到PC,這個選項在PIC24設(shè)備中不可用。然而

2020-03-09 08:46:16

針對基于SRAM工藝的器件的下載配置問題,本文介紹采用AT89S2051單片機(jī)配合串行E2PROM存儲器,實現(xiàn)CPLD/FPGA器件的被動串行(PS)模式的下載配置。

2021-04-13 06:25:40

非易失性存儲器平衡方法

2021-01-07 07:26:13

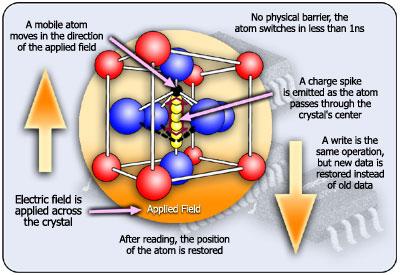

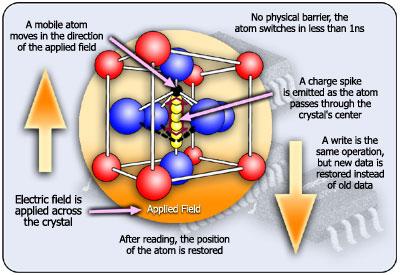

鐵電存儲器FRAM詳解:

鐵電存儲器(FRAM)產(chǎn)品將ROM的非易失性數(shù)據(jù)存儲特性和RAM的無限次讀寫、高速讀寫

2008-01-30 09:13:50 4172

4172

本文介紹了FPGA外部存儲器的設(shè)計方法,可以有效地解決雷達(dá)實時信號處理過程中海量數(shù)據(jù)的存儲問題,同時也可以充分利用FPGA去控制SDRAM和FLASH,不僅保證了資源的充分利用,也可以

2011-08-18 11:46:45 7309

7309

基于FPGA的高速固態(tài)存儲器優(yōu)化設(shè)計_楊玉華

2017-01-13 21:40:36 1

1 基于MSP430功能模塊詳解系列之——FLASH存儲器

2017-10-12 15:27:35 11

11 應(yīng)用于宇航領(lǐng)域的新型元器件必須經(jīng)過嚴(yán)格的性能功能的驗證,傳統(tǒng)的驗證平臺是針對特定的待驗證器件設(shè)計的,不同的器件需要設(shè)計不同的驗證平臺,使得驗證工作周期長、成本高、可移植性差。本文介紹基于FPGA

2017-11-17 03:00:45 1027

1027

Xilinx FPGA 提供可簡化接口設(shè)計的 I/O 模塊和邏輯資源。盡管如此,這些 I/O 模塊以及額外的邏輯仍需設(shè)計人員在源 RTL 代碼中配置、驗證、執(zhí)行,并正確連接到系統(tǒng)的其余部分,然后仔細(xì)

2017-11-24 16:21:46 876

876 FPGA設(shè)計和驗證工程師當(dāng)今面臨的最大挑戰(zhàn)之一是時間和資源制約。隨著FPGA在速度、密度和復(fù)雜性方面的增加,完成一個完整時序驗證對人力和計算機(jī)處理器、存儲器提出了更多更高的要求。 隨著FPGA器件

2019-10-06 17:57:00 953

953

FPGA 設(shè)計人員在滿足關(guān)鍵時序余量的同時力爭實現(xiàn)更高性能,在這種情況下,存儲器接口的設(shè)計是一個一向構(gòu)成艱難而耗時的挑戰(zhàn)。Xilinx FPGA 提供 I/O 模塊和邏輯資源,從而使接口設(shè)計變得

2018-08-11 11:04:00 2983

2983

高溫存儲器的詳解及推薦 存儲器根據(jù)不同的分類條件具有多種分類方式: 用途的不同可以分為內(nèi)存(主存儲器)和外存(輔助存儲器) 存儲介質(zhì)的不同可分為磁表面存儲器和半導(dǎo)體存儲器 存儲方式的不同可分為順序

2020-03-16 15:15:44 1447

1447 高溫存儲器的詳解及推薦 存儲器根據(jù)不同的分類條件具有多種分類方式: 用途的不同可以分為內(nèi)存(主存儲器)和外存(輔助存儲器) 存儲介質(zhì)的不同可分為磁表面存儲器和半導(dǎo)體存儲器 存儲方式的不同可分為順序

2020-03-23 11:41:21 941

941 基于FPGA塊存儲器的多位反轉(zhuǎn)容錯

2021-06-19 14:16:57 19

19 FPGA各存儲器之間的關(guān)系(嵌入式開發(fā)工作怎么樣)-該文檔為FPGA各存儲器之間的關(guān)系總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 16:35:09 6

6 FPGA中嵌入式塊存儲器的設(shè)計(嵌入式開發(fā)平臺)-該文檔為FPGA中嵌入式塊存儲器的設(shè)計總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 10:14:40 6

6

電子發(fā)燒友App

電子發(fā)燒友App

評論