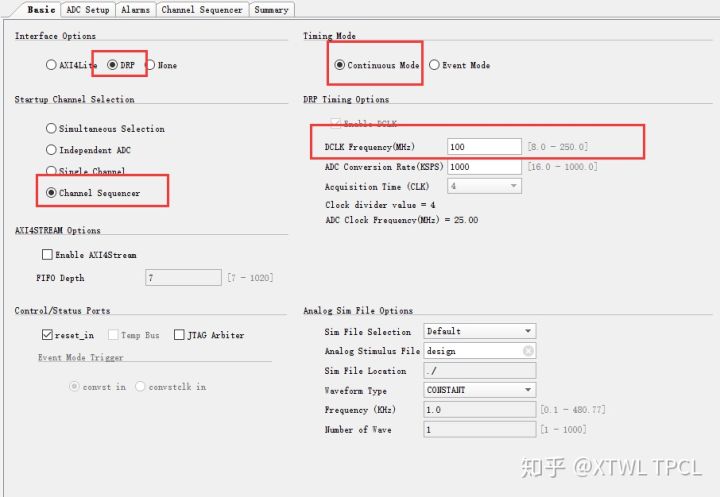

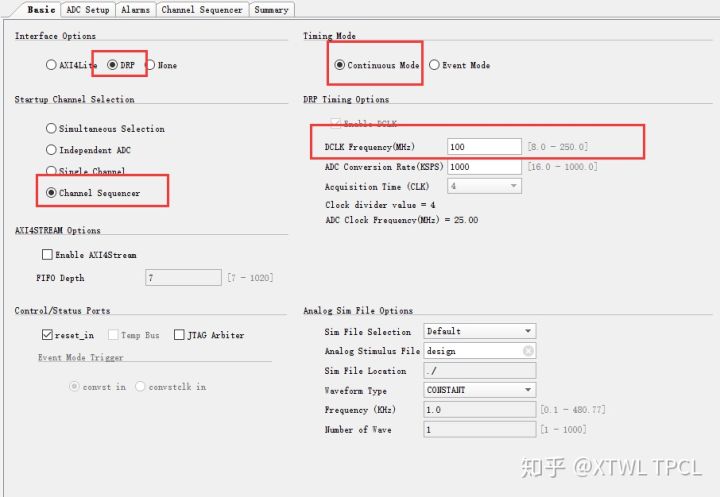

Xilinx 7系列FPGA全系內(nèi)置了一個ADC,稱呼為XADC。 這個XADC,內(nèi)部是兩個1mbps的ADC,可以采集模擬信號轉(zhuǎn)為數(shù)字信號送給FPGA內(nèi)部使用。 XADC內(nèi)部可以直接獲取芯片結(jié)溫和

2021-01-01 10:58:00 4216

4216

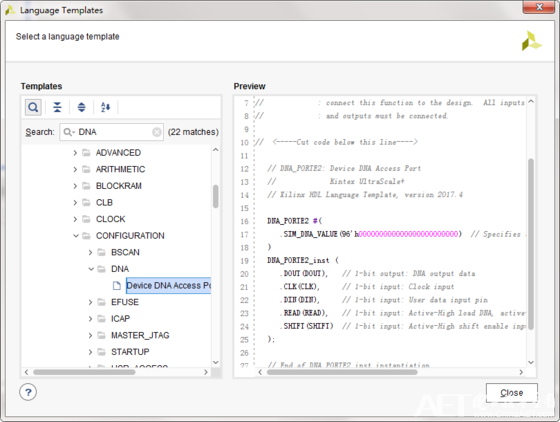

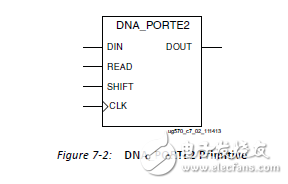

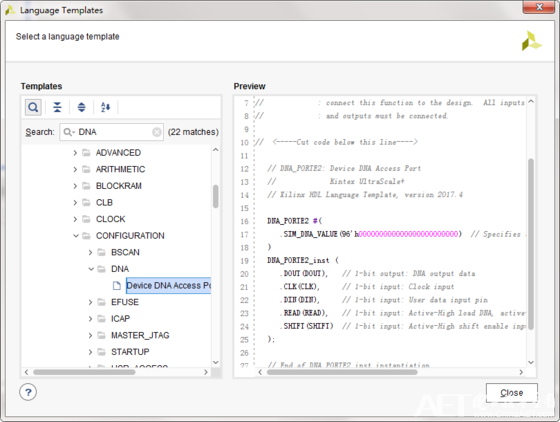

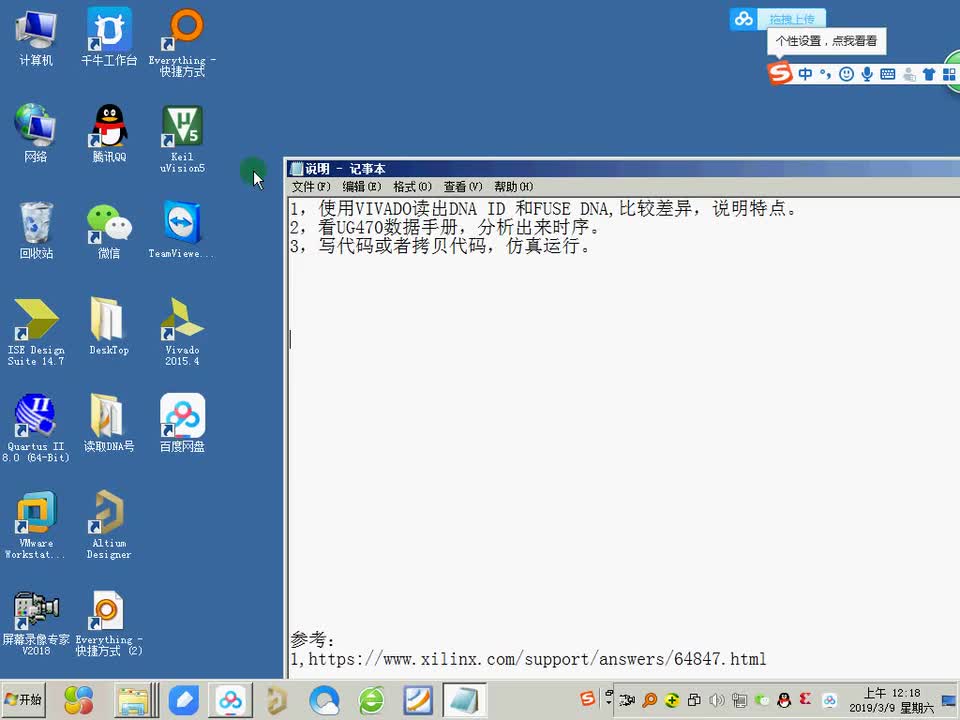

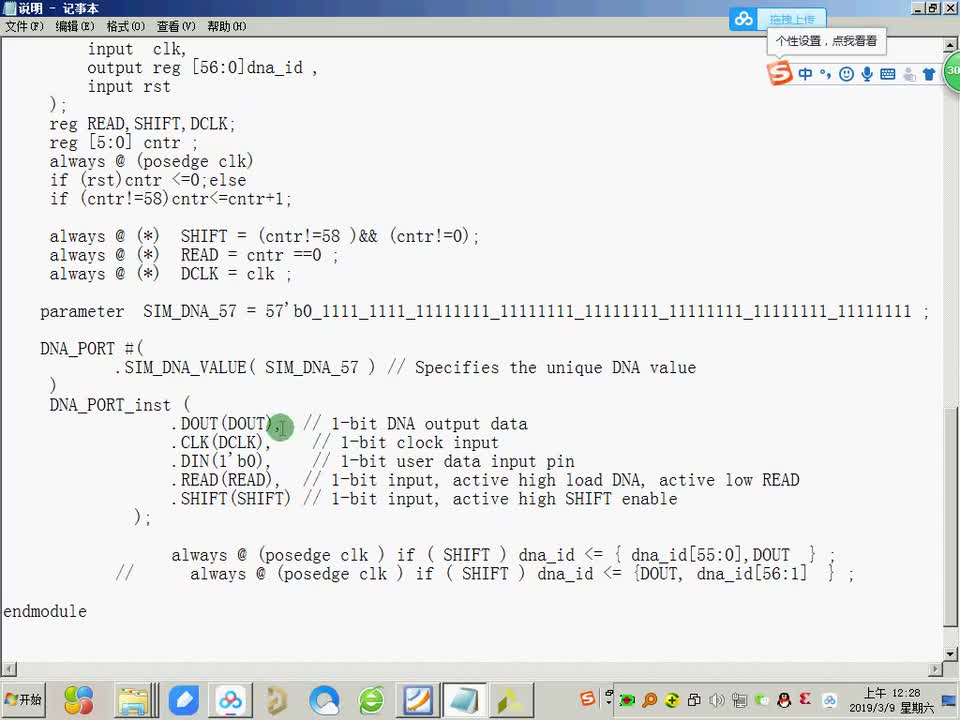

作者:Evening Xilinx每一個FPGA都有一個獨特的ID,也就是Device DNA,這個ID相當(dāng)于我們的身份證,在FPGA芯片生產(chǎn)的時候就已經(jīng)寫死在芯片的eFuse寄存器中,具有不可修改

2021-01-02 09:44:00 4187

4187

中找到。”但我真的找不到這個模板!我也很喜歡使用項目導(dǎo)航器來實現(xiàn)設(shè)計。但我無法找到一個選項生成HDL模板或在IP核生成器中沒有DNA或DNA_Port。感謝幫助

2020-06-12 07:53:26

如果采用dna加密,讀取每塊fpga的id,在允許的范圍內(nèi)就輸出使能信號驅(qū)動算法模塊,就是在開發(fā)時將客戶提供的id預(yù)先存入ram,重新綜合成ngc文件給用戶。這種方法有幾個問題想請教各位

2012-05-02 17:54:53

請教大家,我打算使用這個方案,FPGA使用控制器硬核,外面掛兩個16位DDR,這兩個DDR的的差分時鐘、地址線、控制線等共用,只有數(shù)據(jù)線使用各自的。希望做到兩片同時訪問,一次把32位數(shù)據(jù)分成兩個16

2016-04-26 13:41:00

FPGA系統(tǒng)設(shè)計中,如果用兩個FPGA工作,應(yīng)該如何設(shè)計兩片之間的通信?從片的配置和時鐘輸入與主片有何不同?一個做主片用于數(shù)據(jù)處理和控制,一個做從片用于IO擴展。硬件和軟件上應(yīng)該如何設(shè)計兩片之間

2023-05-08 17:18:25

.................................................92.1 理解綜合兩個過程 ...................................................82 綜合工具與代碼風(fēng)格

2012-08-11 11:43:17

請教大家一個問題,板子上有兩個FPGA,想用一個PROM配置,將PROM和兩個FPGA用邊界掃描下載方式連起來可以嗎? 就是下圖這種模式,可不可以再多串一個FPGA呢?

2014-03-24 15:53:09

的JTAG Chain和Debug Core,因此本文提出一種比較方便的調(diào)試方法來同時使用這兩個core:ILA通過analyzer查看,VIO通過TCL控制。使用步驟:使用CoreGEN生成VIO

2012-03-08 15:29:11

本本將從常見的XILINX FPGA和Altera 兩家FPGA的電源供電作如下介紹:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

和Bottom各一個單端管腳。圖1給出了K325T芯片用戶Bank IO原理圖舉例。圖1、K325T芯片用戶Bank IO原理圖在圖中,我們可以看到紅色圈住的兩個單端信號,綠色線條圈住的_CC時鐘管腳不用作時鐘

2021-05-28 09:23:25

和Bottom各一個單端管腳。圖1給出了K325T芯片用戶Bank IO原理圖舉例。圖1、K325T芯片用戶Bank IO原理圖在圖中,我們可以看到紅色圈住的兩個單端信號,綠色線條圈住的_CC時鐘管腳不用作時鐘

2021-07-08 08:00:00

各位大神,請問Xilinx FPGA中的DCI是如何使用的?我知道是把每個Bank的VRP、VRN管腳分別下拉、上拉,除此之外,在HDL代碼和約束中應(yīng)該如何寫呢?查了半天資料沒有查到,所以來論壇問問。@LQVSHQ

2017-08-20 20:51:57

`Xilinx FPGA無痛入門,海量教程免費下載 無私的特權(quán)同學(xué)為您送上85個課時的文檔教程,35個經(jīng)典例程,百度網(wǎng)盤可以免費下載:http://pan.baidu.com/s/1jGjAhEm

2015-07-22 11:49:20

兩個文件都可以加載。但 是,當(dāng)用戶在ISE中調(diào)用了EDK(比如使用microblaze或者powerpc),ISE生成.bin文件并不會把用戶的.elf文件初始化到 FPGA內(nèi)部的數(shù)據(jù)和程序存儲器中

2016-05-22 23:38:23

frame就會被分開,在配置時無法尋址。 各個模塊實現(xiàn)在各自的區(qū)域中,那么各模塊間的通信是怎樣實現(xiàn)的那?在FPGA內(nèi)信號的傳遞是通過布線資源實現(xiàn)的,兩個模塊A、B要實現(xiàn)通信既是將A的信號 線與相映的B

2015-09-22 23:36:50

是怎樣實現(xiàn)的那?在FPGA內(nèi)信號的傳遞是通過布線資源實現(xiàn)的,兩個模塊A、B要實現(xiàn)通信既是將A的信號 線與相映的B的信號線相連,由于ise的自動布線無法指定某條信號線布在哪里,所以相鄰兩個模塊的信號線不能

2015-08-20 22:57:10

描述PMP10555 參考設(shè)計提供為移動無線基站應(yīng)用中的 Xilinx? Ultrascale? 16nm 系列 FPGA/SoC 供電所需的所有電源軌。此設(shè)計對內(nèi)核及兩個多輸出降壓型穩(wěn)壓器 IC

2018-11-19 14:58:25

你好,我是與

FPGA有關(guān)的初學(xué)者,但我對以下內(nèi)容感興趣:

Xilinx Virtex-7

FPGA VC707評估套件我注意到PCIe插座是x8,但我的PC主板只有x16?

兩個插座兼容嗎?問候,魯?shù)婪?/div>

2020-03-17 10:00:32

`描述PMP10555 參考設(shè)計提供為移動無線基站應(yīng)用中的 Xilinx? Ultrascale? 16nm 系列 FPGA/SoC 供電所需的所有電源軌。此設(shè)計對內(nèi)核及兩個多輸出降壓型穩(wěn)壓器 IC

2015-05-11 10:46:35

哪位大神比較熟悉Xilinx的FPGA,本人新手一枚,想學(xué)習(xí)FPGA,希望能告知一些Xilinx的FPGA快速入門資料獲取方法。謝謝!!!

2014-03-11 01:05:57

,編譯即可生成如上兩個文件,均是先加載.nky然后加載.bit(要妥善保留.nky文件)。完成以上步驟加密設(shè)計完成。該方法需要注意如下:1.下載流程首先燒寫.nky然后燒寫.bit文件2.不支持動態(tài)配置

2013-01-01 20:44:47

設(shè)置需要以下設(shè)備:兩臺運行Windows?操作系統(tǒng)的標(biāo)準(zhǔn)臺式機/筆記本電腦兩個Xilinx? VC707開發(fā)套件兩個AD9625 FMC電路板,AD-FMCADC2-EBZTektronix HFS

2018-09-03 14:48:59

\AD 10\Library\Xilinx目錄下仍然只有Xilinx Spartan-3AN.IntLib一個集成庫,Altera/Lattice也是如此,如何獲取并安裝其他期間的集成庫啊?謝謝了,有經(jīng)驗的大大請不吝賜教

2012-01-15 10:16:41

的忘了。。。。。。。。。小魚裝個逼給大家小小科普一下這個DNA號是啥東西?Xilinx公司的FPGA芯片都有自己獨一的Device DNA號,這個是一個二進制序列,而且每個芯片的都是唯一的。用戶可以

2016-06-06 23:44:45

嗨,我需要在我的設(shè)計中使用兩個BRAM來實現(xiàn)兩個FIFO。我知道在spartan6上最大BRAM內(nèi)存可以是9或18 K,所以我使用64x32bit和512x8bit BRAM,它們一起小于9k。但是

2019-08-05 08:45:37

寫了兩個FPGA程序,是兩個模塊,如何將這兩個模塊連接到一起進行編譯仿真。應(yīng)該如何操作。

2013-06-06 13:40:07

你好。我在我的設(shè)計中使用了兩個FPGA(Spartan 3)。在這種情況下,我可以使用單個Config PROM將我的位文件加載到FPGA。如果是,我應(yīng)該如何連接FPGA和PROM,以便相應(yīng)的配置

2018-09-28 11:36:13

你好,我目前正在研究一個項目,我需要在兩個替代設(shè)計選項之間做出決定,我必須考慮可靠性分析。(我不需要擔(dān)心我的設(shè)計中的軟錯誤效應(yīng))根據(jù)我的研究,我發(fā)現(xiàn)FIT值是FPGA可靠性的基本標(biāo)準(zhǔn)。在第一個設(shè)計中

2020-03-12 11:16:18

基于FPGA產(chǎn)生兩個控制脈沖(周期,脈寬,占空比,時序關(guān)系可調(diào)),用控制脈沖來控制兩臺工業(yè)相機。本人不是很懂,求大神指點。。。

2016-05-30 21:59:54

都可以幫助獲取上述兩個電源板的信息?謝謝! 以上來自于谷歌翻譯 以下為原文I have an HP 6624A system power supply SN 2621A and need a

2019-07-08 11:26:13

;elsif clock_falling_edge 去抖輸入 - 使用最后讀取值萬一但實施失敗我還修改了我的時鐘pll配置,我創(chuàng)建了兩個時鐘輸出,180度相移第一個時鐘上升沿讀取輸入線,第二個時鐘去抖動輸入

2019-08-05 06:25:54

我有一臺Kintex 7 XC7K325T卡。關(guān)于memroy資源的官方用戶指南說明我的卡有445個36-Kb BlockRAM塊。來自同一指南:“Xilinx?7系列FPGA中的Block RAM

2019-03-05 12:28:54

。我想創(chuàng)建一個sim_tb_top.v來實例化設(shè)計的兩半(即為不同的FPGA上的每個模塊創(chuàng)建兩個xdc文件)并編譯并模擬設(shè)??計的sim_tb_top.v。我將如何進行此操作?我應(yīng)該創(chuàng)建兩個項目并在每個

2020-03-17 08:55:38

你好,我打算建立通信以在兩個處理器之間讀寫。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9處理器,另一方面是FPGA(ZC7020)。我在FPGA端沒有任何PCIe硬端口。因此

2020-04-16 09:04:30

我需要知道上面的xilinx產(chǎn)品是否只包含兩個RS232和一個FPGA(XC3S700A-FG484)和小板上的FLASH PROM(超過4 MB)如果有這樣的東西,請告訴我如何獲得它,謝謝

2019-09-20 10:33:01

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產(chǎn)品介紹使用Xilinx的FPGA、SoC和ACAP進行設(shè)計和開發(fā)

2021-01-22 06:38:47

接口,所以我想問一些問題,如果兩個FPGA我選擇雙工通信,我可以只使用一根光纖(FPGA_2在與FPGA_3通信時從FPGA_1接收數(shù)據(jù))嗎?或者在一對LC接口中有兩個單工,一個接收發(fā)送(但是Map一直出錯)?

2019-08-07 10:09:05

大家好,如果兩個FPGA連接在單個JTAG鏈中。那么DONE和INIT引腳的推薦連接是什么。兩個FPGA的INIT引腳(也是DONE引腳)是應(yīng)該連接在一起還是應(yīng)該分開?Xilinx是否為此推薦了任何

2019-01-10 11:00:55

1.工藝節(jié)點 首先不管選擇什么廠家的產(chǎn)品,都建議在其主流產(chǎn)品中選擇合適的芯片。 以上是目前 Xilinx 主流的也是常用的幾個 FPGA 產(chǎn)品系列,這里不談傳說中的后兩個系列

2020-12-23 17:21:03

為什么屬性節(jié)點中只能獲取buttom(紅色游標(biāo))的位置,而沒有top(黃色游標(biāo))的位置,請問游標(biāo)位置是用cursor.posx、cursor.posy這兩個屬性獲取嗎?或者說我獲取游標(biāo)位置的方法不對,請熟悉的朋友指點指點,我再此先行謝過

2014-06-06 22:24:27

你好,任何人:我現(xiàn)在用兩塊Kintex超大規(guī)模FPGA開發(fā)單板。我應(yīng)該如何為兩個FPGA供電?1)單一解決方案,一個DCDC穩(wěn)壓器供電兩個FPGA的相同電源軌(如VCCINT)。2)單獨解決方案

2019-04-03 15:26:53

本帖最后由 eehome 于 2013-1-5 10:09 編輯

共8章,很全面包括altera和xilinx,兩個公司的FPGA和相關(guān)軟件都涉及到,軟件操作,語法點,編碼風(fēng)格,還有專門一章

2012-12-06 16:10:55

您好Xilinx社區(qū),我想用兩個時鐘驅(qū)動我的系統(tǒng)。一個時鐘用于多個組件,與主時鐘一起運行并由IBUFGDS生成。另一個應(yīng)該驅(qū)動IBUFDS_GTE2原語,因為實現(xiàn)了PCI Express。我有兩個

2018-11-09 11:41:50

我有一個用于過時的Xilinx FPGA的加載文件。是否有機會將其轉(zhuǎn)換為Xilinx新FPGA的文件?例如斯巴達。以上來自于谷歌翻譯以下為原文I have a loading fille fora

2019-02-13 07:53:44

你好,教授們:我有兩個相同的FPGA,它們是240t我已經(jīng)知道測量FPGA的阻抗是一件危險的事情,但我把它們放在同一塊電路板上。我測量了每塊板的阻抗,發(fā)現(xiàn)數(shù)據(jù)不同。我測量的數(shù)據(jù)如下:VCCINT

2020-06-17 11:25:59

我正在設(shè)計一個帶有兩個配置為串行菊花鏈的Spartan 6-LX9的電路板,我想知道一個XCF04S可用于存儲兩個FPGA的配置。以上來自于谷歌翻譯以下為原文I am designing a

2019-07-30 07:43:32

1中的TXOUTCLK信號之間的相位偏移都會發(fā)生變化。因此,我無法找到一種方法來在兩個FPGA上的TXOUTCLK之間獲得一致的相位偏移,這在FPGA被重新編程時會持續(xù)存在。我希望有一些方法可以實現(xiàn)

2020-08-28 06:22:25

MAMF-011069集成雙開關(guān) - LNA 模塊MAMF-011069 是一款雙通道模塊,包含兩個 2 級低噪聲放大器和兩個高功率開關(guān),采用 5 毫米 32 引腳 QFN 封裝。該模塊的工作頻率為

2023-01-06 11:31:24

十分鐘學(xué)會Xilinx FPGA 設(shè)計

Xilinx FPGA設(shè)計基礎(chǔ)系統(tǒng)地介紹了Xilinx公司FPGA的結(jié)構(gòu)特點和相關(guān)開發(fā)軟件的使用方法,詳細(xì)描述了VHDL語言的語法和設(shè)計方法,并深入討

2010-03-15 15:09:08 177

177 Synopsys和Xilinx合作出版業(yè)界首本基于FPGA的SoC設(shè)計原型方法手冊。

2011-03-21 10:26:23 810

810 本書系統(tǒng)地論述了Xilinx FPGA開發(fā)方法、開發(fā)工具、實際案例及開發(fā)技巧,內(nèi)容涵蓋Xilinx器件概述、Verilog HDL開發(fā)基礎(chǔ)與進階、Xilinx FPGA電路原理與系統(tǒng)設(shè)計

2012-07-31 16:20:42 11268

11268

本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 Xilinx FPGA設(shè)計進階(提高篇)

有需要的下來看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發(fā)環(huán)境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發(fā)環(huán)境

2016-01-18 15:30:32 45

45 Xilinx所有的FPGA器件都有Device DNA,這是一個57bit的二進制序列,在器件生產(chǎn)的時候燒死到芯片里面,每個芯片都是唯一的。這個序列,用戶可以通過JTAG或者verilog(VHD)應(yīng)用程序直接讀出。怎么使用這個DNA,因應(yīng)用不同可能千差萬別。

2019-10-12 17:55:00 1168

1168 文檔內(nèi)容包含基于Xilinx FPGA的開發(fā)板代碼及原路圖,供網(wǎng)友參考。

2017-09-01 11:09:24 20

20 Xilinx FPGA的Maxim參考設(shè)計

2017-10-31 09:59:24 23

23 FPGA本身是有專門的時鐘cell的,以xilinx FPGA為例,就是primitive庫中的BUFG。

2018-12-22 15:33:59 1588

1588 在此Xilinx研究實驗室演示中,解釋了單源SYCL C ++示例以及生成在Xilinx FPGA上運行的硬件實現(xiàn)的方法。

2018-11-20 06:30:00 2918

2918 Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 3322

3322 本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

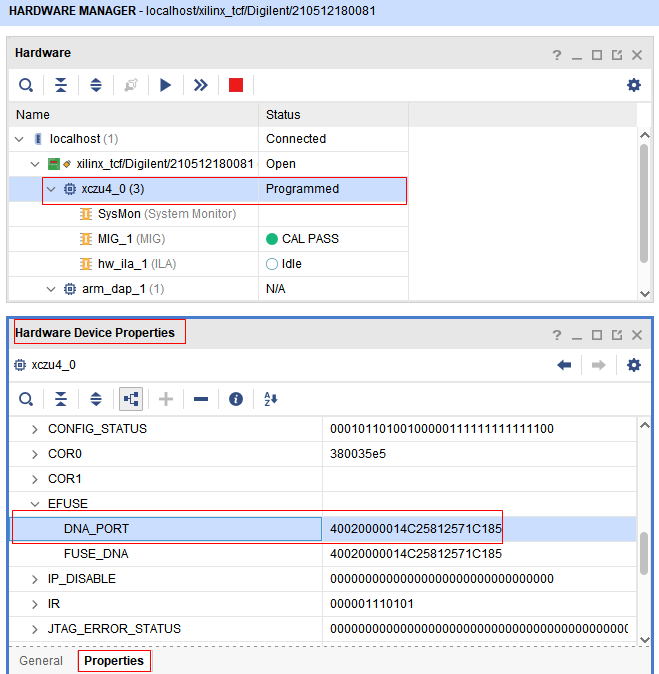

5120 在FPGA芯片生產(chǎn)的時候就已經(jīng)寫死在芯片的eFuse寄存器中,具有不可修改的屬性,因為使用的是熔斷技術(shù)。

2020-03-29 16:46:00 4387

4387 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個工藝級別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點 4.7系列

2020-11-13 18:03:30 14065

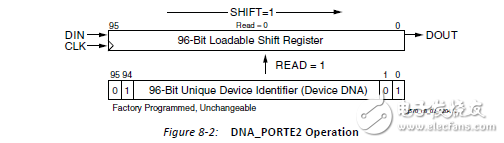

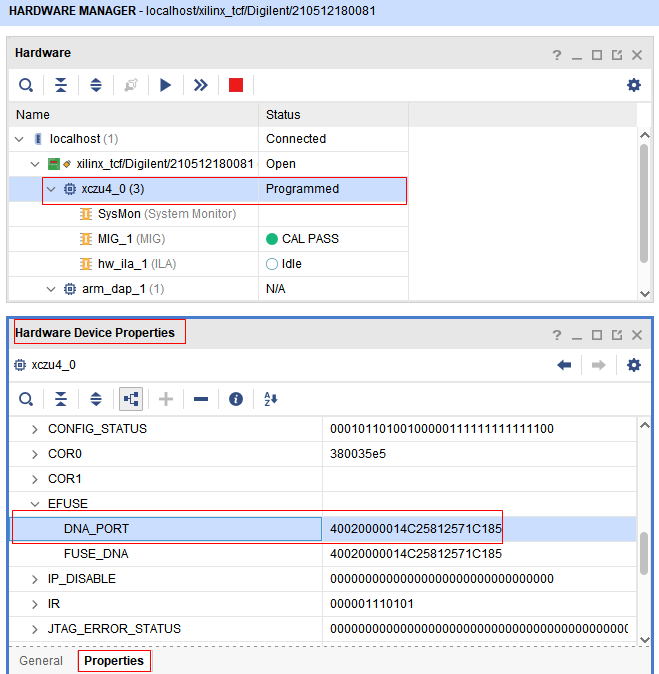

14065 Xilinx 用兩個 96 位獨特器件標(biāo)識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統(tǒng) (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2022-02-08 14:19:49 1149

1149

Xilinx 用兩個 96 位獨特器件標(biāo)識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統(tǒng) (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2021-01-23 06:32:33 10

10 Xilinx-7系列FPGA主要包括:Spartan?-7、Artix?-7、Kintex?-7、Virtex?-7。其性能、密度、價格也隨著系列的不同而提升。和前幾代FPGA產(chǎn)品不同的是,7系列

2021-01-30 06:00:11 16

16 AD5933 pmod Xilinx FPGA參考設(shè)計

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA參考設(shè)計

2021-04-22 13:35:23 11

11 AD5628 pmod Xilinx FPGA參考設(shè)計

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA參考設(shè)計

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA參考設(shè)計

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA參考設(shè)計

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA參考設(shè)計

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA參考設(shè)計

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA參考設(shè)計

2021-05-24 10:29:20 17

17 Xilinx FPGA開發(fā)實用教程資料包免費下載。

2022-04-18 09:43:46 24

24 Xilinx FPGA pcb設(shè)計

2023-05-29 09:11:36 0

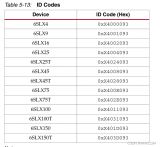

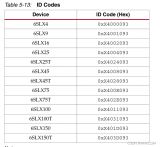

0 ,這樣就可以通過讀取IDCODE,來進行自動區(qū)分不同的硬件,分別進行不同的處理方式。本文介紹Xilinx所有FPGA芯片型號IDCODE的獲取方法,一共4種方式,總有一種適合你,這些方法同樣適用于別的廠家的FPGA/MCU,比如Intel,Lattice,Microchip等等。

2023-07-03 13:01:31 1583

1583

電子發(fā)燒友網(wǎng)站提供《面向Xilinx FPGA和SoC的超快設(shè)計方法指南.pdf》資料免費下載

2023-09-14 10:02:31 1

1 電子發(fā)燒友網(wǎng)站提供《Xilinx FPGA和SoC的超高速設(shè)計方法指南.pdf》資料免費下載

2023-09-14 09:41:06 0

0 Xilinx是一家專業(yè)的可編程邏輯器件(PLD)廠商,其產(chǎn)品包括FPGA、CPLD、SOC等。Xilinx的FPGA產(chǎn)品線有多個系列,其中7系列和Ultrascale系列是比較常見的兩種。那么,這兩個系列有什么區(qū)別呢?

2023-09-15 14:44:54 1776

1776

每一片芯片內(nèi)部存有一個設(shè)備標(biāo)識符,xilinx把它叫做DNA,這個DNA是不可更改的,永久存在芯片里面的。

2024-01-03 09:19:03 641

641

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應(yīng)用領(lǐng)域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評論