FPGA入門:第一個(gè)工程實(shí)例之功能仿真概述 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2015-03-01 19:40:23

的說(shuō)就是給待驗(yàn)證的設(shè)計(jì)添加激勵(lì),同時(shí)觀察它的輸出響應(yīng)是否符合設(shè)計(jì)要求。如圖5.27所示,測(cè)試平臺(tái)就是要模擬一個(gè)和待驗(yàn)證設(shè)計(jì)接口的各種外圍設(shè)備。圖5.27 設(shè)計(jì)與驗(yàn)證仿真測(cè)試是FPGA設(shè)計(jì)流程中必不可少

2015-03-03 14:12:09

FPGA入門:第一個(gè)工程實(shí)例之功能仿真運(yùn)行 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2015-03-06 11:56:37

FPGA入門:第一個(gè)工程實(shí)例之功能仿真平臺(tái)搭建 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com

2015-03-04 11:15:55

FPGA入門:第一個(gè)工程實(shí)例之功能概述 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2015-02-26 12:02:16

FPGA入門:第一個(gè)工程實(shí)例之工程創(chuàng)建 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2015-02-12 11:14:55

FPGA入門:第一個(gè)工程實(shí)例之設(shè)計(jì)輸入 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2015-02-28 10:41:14

FPGA入門:第一個(gè)工程實(shí)例之功能仿真概述本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2019-02-13 06:35:24

FPGA應(yīng)用開發(fā)入門與典型實(shí)例

2017-04-21 12:47:01

系統(tǒng)的設(shè)計(jì)技巧 2.4 FPGA硬件系統(tǒng)的調(diào)試方法 2.5 典型實(shí)例1:在Altera的FPGA開發(fā)板上運(yùn)行第一個(gè)FPGA程序 2.6 典型實(shí)例2:在Xilinx的FPGA開發(fā)板上運(yùn)行第一個(gè)

2012-02-09 15:45:32

;fromuid=220353典型實(shí)例1 在Altera的FPGA開發(fā)板上運(yùn)行第一個(gè)FPGA程序.rar典型實(shí)例2 在Xilinx的FPGA開發(fā)板上運(yùn)行第一個(gè)FPGA程序.rar典型實(shí)例3_1 數(shù)字跑表

2012-02-09 16:29:46

FPGA入門:第一個(gè)工程實(shí)例之設(shè)計(jì)輸入 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問(wèn)網(wǎng)盤:http://pan.baidu.com/s

2019-02-13 03:22:24

圖3其中圖1為demo_test.v圖2為 testbench_demo_test.sv圖3為run.do啟動(dòng)仿真平臺(tái)A. 把三個(gè)文件放置到同一個(gè)目錄下,該目錄的路徑必須是純英文或有短下劃線(關(guān)于

2013-11-26 13:11:10

arm9的第一個(gè)應(yīng)用程序 helloworld 的軟件 硬件平臺(tái)都有哪些?比如軟件開發(fā)環(huán)境需要搭建一個(gè)什么平臺(tái) 等等 ,路過(guò)的朋友不妨看看,謝謝。

2013-11-12 14:41:44

Dymola 是法國(guó)Dassault Systems公司的多學(xué)科系統(tǒng)仿真平臺(tái),廣泛應(yīng)用于國(guó)內(nèi)外汽車、工業(yè)、交通、能源等行業(yè)的系統(tǒng)總體架構(gòu)設(shè)計(jì)、指標(biāo)分解以及系統(tǒng)功能驗(yàn)證及優(yōu)化等。Dymola 支持FMI 標(biāo)準(zhǔn)接口協(xié)議,可用于集成不同軟件建立的、不同詳細(xì)程度的模型,進(jìn)行MIL、SIL 和HIL 測(cè)試。

2021-01-22 06:35:10

Dymola多學(xué)科系統(tǒng)仿真平臺(tái)

2020-12-23 07:59:30

仿真平臺(tái)用起來(lái)真的很方便。公司之前使用的是國(guó)外某知名仿真平臺(tái),做半實(shí)物測(cè)試操作十分繁瑣,特別是使用FPGA做硬件仿真的時(shí)候使用比較麻煩,每修改一點(diǎn)都需要編譯幾十分鐘,所以往往都是需要仿真器廠家派工程

2023-04-14 14:32:58

``附件里是FRDM-KL25Z開發(fā)第一期(平臺(tái)介紹、環(huán)境搭建、第一個(gè)工程)的資料。其中第一部分和第二部分PPT里有介紹。第三部分工程建立請(qǐng)看以下圖片資料:``

2015-01-30 18:12:05

的組件,是整個(gè)驗(yàn)證平臺(tái)數(shù)據(jù)流的源泉。本節(jié)以一個(gè)簡(jiǎn)單的DUT為例,說(shuō)明一個(gè)只有driver的UVM驗(yàn) 證平臺(tái)是如何搭建的。最簡(jiǎn)單的驗(yàn)證平臺(tái),假設(shè)有如下的DUT定義:這個(gè)DUT的功能非常簡(jiǎn)單,通過(guò)rxd接收

2020-12-04 15:48:19

之前談增程式電動(dòng)汽車仿真平臺(tái)時(shí),用過(guò)下圖的仿真軟件架構(gòu)。最近一段時(shí)間,我們想嘗試搭建一個(gè)豐田THS系統(tǒng)仿真平臺(tái),其基本架構(gòu)也是一樣的。駕駛員模型部分一樣,不用修改;控制策略部分需要大改,因?yàn)榛靹?dòng)控制

2021-08-27 07:59:14

軟件在功能強(qiáng)大、符合要求的硬件和可擴(kuò)展操作系統(tǒng)上運(yùn)行時(shí),相比以硬件為中心的策略,更快地定位設(shè)計(jì)中存在的風(fēng)險(xiǎn)。硬件仿真已有四十年的發(fā)展歷史,在開拓主流市場(chǎng)后,Veloce 硬件仿真平臺(tái)已成為硬件、軟件

2016-04-15 16:25:55

FPGA仿真板軟件(ISE 6.2)安裝步驟一ISE 6.2的安裝文件包含兩個(gè)部分:CD1和CD2。其中CD1主要為軟件安裝,CD2主要為庫(kù)安裝。二打開CD1文件夾下的ise CD1文件夾,運(yùn)行其中

2012-03-02 10:41:12

`Xilinx FPGA入門連載23:PLL實(shí)例之功能簡(jiǎn)介特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 PLL概述PLL

2015-11-10 08:44:06

`Xilinx FPGA入門連載27:基于Chipscope的超聲波測(cè)距調(diào)試之功能簡(jiǎn)介特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2015-11-23 11:24:49

`Xilinx FPGA入門連載35:倒車?yán)走_(dá)實(shí)例之功能簡(jiǎn)介特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 倒車?yán)走_(dá)應(yīng)用背景如圖所示

2015-12-11 11:21:18

`Xilinx FPGA入門連載39:SRAM讀寫測(cè)試之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫(kù)設(shè)置

2015-12-23 15:06:56

Xilinx FPGA入門連載43:FPGA片內(nèi)ROM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-06 12:22:53

Xilinx FPGA入門連載45:FPGA片內(nèi)ROM實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫(kù)

2016-01-11 12:17:28

Xilinx FPGA入門連載47:FPGA片內(nèi)RAM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-20 12:28:28

`Xilinx FPGA入門連載49:FPGA片內(nèi)RAM實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫(kù)

2016-01-25 12:55:23

“Project”界面下出現(xiàn)了兩個(gè)設(shè)備,如圖所示。選擇第一個(gè)設(shè)備。在第一個(gè)設(shè)備上單擊鼠標(biāo)右鍵,如圖所示,選擇“Configure…”。接著彈出的配置界面中,點(diǎn)擊“Select New File”,彈出右側(cè)所示

2016-01-27 13:10:35

Xilinx FPGA入門連載51:FPGA片內(nèi)FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-02-26 10:26:05

`Xilinx FPGA入門連載53:FPGA片內(nèi)FIFO實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx

2016-03-02 12:30:57

“Project”界面下出現(xiàn)了兩個(gè)設(shè)備,如圖所示。選擇第一個(gè)設(shè)備。在第一個(gè)設(shè)備上單擊鼠標(biāo)右鍵,如圖所示,選擇“Configure…”。接著彈出的配置界面中,點(diǎn)擊“Select New File”,彈出

2016-03-04 13:13:12

`Xilinx FPGA入門連載55:FPGA 片內(nèi)異步FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門連載57:FPGA 片內(nèi)異步FIFO實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-03-16 11:32:11

看到“Project”界面下出現(xiàn)了兩個(gè)設(shè)備,如圖所示。選擇第一個(gè)設(shè)備。在第一個(gè)設(shè)備上單擊鼠標(biāo)右鍵,如圖所示,選擇“Configure…”。接著彈出的配置界面中,點(diǎn)擊“Select New File

2016-03-16 12:13:05

`Xilinx FPGA入門連載59:FPGA 片內(nèi)ROM FIFO RAM聯(lián)合實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:43:36

`Xilinx FPGA入門連載60:FPGA 片內(nèi)ROM FIFO RAM聯(lián)合實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-18 09:20:25

`Xilinx FPGA入門連載72:波形發(fā)生器之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡(jiǎn)介 該實(shí)例工程的功能

2016-04-20 10:14:34

FPGA SF-SP6入門指南 -- FPGA片內(nèi)ROM實(shí)例之功能仿真Lesson48 特權(quán)Xilinx FPGA SF-SP6入門指南 -- FPGA片內(nèi)ROM實(shí)例之chipscope在線調(diào)試

2015-07-22 11:49:20

調(diào)試方法,主要包括Keil uV2與Proteus結(jié)合搭建仿真平臺(tái),利用匯編語(yǔ)言方式、omf格式文件的C51語(yǔ)言方式和UBROF格式文件的C51語(yǔ)言方式進(jìn)行源代碼級(jí)調(diào)試;第6章包括22個(gè)實(shí)例項(xiàng)目,每個(gè)實(shí)例項(xiàng)目都給出了詳細(xì)的實(shí)例目的、實(shí)例原理圖、實(shí)例內(nèi)容、實(shí)例步驟、參考程序。`

2012-08-06 23:45:18

環(huán)境搭建完成下一步就是開始編程,通常的第一個(gè)實(shí)例程序當(dāng)然是跑馬燈。以下是用庫(kù)函數(shù)進(jìn)行編寫的部分程序截圖,和實(shí)驗(yàn)效果,總體感覺(jué)和STM32差異不大,從發(fā)燒友論壇下了開發(fā)板的原理圖和一些歷程,程序模板

2016-08-10 18:16:02

正式搭建環(huán)境,完成第一個(gè)項(xiàng)目。聲明一下,我用的代碼是官方的例程,本想發(fā)自己的例程,但是那么久沒(méi)發(fā)帖子了,加上剛搞明白怎樣搭環(huán)境,所以,先發(fā)官方的例程,好給大家個(gè)指導(dǎo)。當(dāng)然要把板子插上,出現(xiàn)如下提示,說(shuō)明板子

2017-05-27 12:18:53

全數(shù)字仿真平臺(tái)作為工業(yè)領(lǐng)域不可缺少的重要軟件之一,除了可以與MATLAB或者Simulink集成外,還支持哪些優(yōu)秀的功能?在了解新一代全數(shù)字仿真平臺(tái)SkyEye之前,先來(lái)學(xué)習(xí)一下什么是全數(shù)字仿真平臺(tái)

2021-12-17 07:48:56

全數(shù)字仿真平臺(tái)作為工業(yè)領(lǐng)域不可缺少的重要軟件之一,除了可以與MATLAB或者Simulink集成外,還支持哪些優(yōu)秀的功能?在了解新一代全數(shù)字仿真平臺(tái)SkyEye之前,先來(lái)學(xué)習(xí)一下什么是全數(shù)字仿真平臺(tái)

2021-12-21 06:42:16

locked就會(huì)拉高,我們以此信號(hào)作為系統(tǒng)的復(fù)位信號(hào),因此也做了“異步復(fù)位,同步釋放”的處理。PLL的輸入時(shí)鐘為FPGA外部晶振產(chǎn)生的時(shí)鐘信號(hào),它經(jīng)過(guò)PLL處理后產(chǎn)生一個(gè)25MHz的時(shí)鐘信號(hào),24位計(jì)數(shù)器在這個(gè)PLL時(shí)鐘的“節(jié)拍”下不停的計(jì)數(shù)。 圖3.1 工程實(shí)例1功能框圖 `

2016-09-09 18:29:24

`例說(shuō)FPGA連載36:DDR控制器集成與讀寫測(cè)試之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實(shí)例對(duì)Altera提供

2016-10-08 17:05:55

例說(shuō)FPGA連載46:Qsys系統(tǒng)搭建與軟件開發(fā)之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖5.1所示,本實(shí)例

2016-11-14 16:00:53

`例說(shuō)FPGA連載50:NAND Flash實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實(shí)例在工程實(shí)例3的基礎(chǔ)上

2016-11-21 17:41:21

外設(shè)子板的第一個(gè)實(shí)驗(yàn)。我們先不動(dòng)用FPGA,而是直接使用Cypress官方給出的bulkloop例程,PC端發(fā)送一組數(shù)據(jù)給FX2,F(xiàn)X2內(nèi)部自動(dòng)將其返回給PC,整個(gè)過(guò)程FX2自動(dòng)完成,無(wú)需FPGA參與。傳輸數(shù)據(jù)流的示意如圖13.3所示。圖13.3 USB傳輸數(shù)據(jù)流 `

2017-02-13 13:16:19

`例說(shuō)FPGA連載99:雙攝像頭圖像采集之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實(shí)例功能框圖20.1如下所示。攝像頭

2017-05-11 21:26:52

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載47:基于仿真的第一個(gè)工程實(shí)例之調(diào)用Modelsim仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-02-05 15:37:06

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載40:基于仿真的第一個(gè)工程實(shí)例之新建工程特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 雙擊

2018-01-15 17:37:56

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載41:基于仿真的第一個(gè)工程實(shí)例之Verilog源碼文件創(chuàng)建特權(quán)同學(xué),版權(quán)所有 下面我們就來(lái)創(chuàng)建工程頂層文件,我們可以點(diǎn)擊菜單欄的“FileàNew

2018-01-17 10:03:58

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載42:基于仿真的第一個(gè)工程實(shí)例之Verilog源碼文件編輯特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-21 21:40:51

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載43:基于仿真的第一個(gè)工程實(shí)例之Verilog語(yǔ)法檢查特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-22 21:05:42

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載44:基于仿真的第一個(gè)工程實(shí)例之Modelsim仿真驗(yàn)證基本設(shè)置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-24 21:20:50

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載45:基于仿真的第一個(gè)工程實(shí)例之測(cè)試腳本創(chuàng)建與編輯特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-26 22:41:26

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載46:基于仿真的第一個(gè)工程實(shí)例之測(cè)試腳本關(guān)聯(lián)設(shè)置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-29 15:00:18

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載78:FPGA片內(nèi)ROM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 該工程

2018-06-16 19:39:24

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載82:FPGA片內(nèi)ROM實(shí)例之功能仿真與在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-06-27 20:04:52

工程實(shí)例內(nèi)部系統(tǒng)功能框圖如圖9.37所示。我們通過(guò)IP核例化一個(gè)RAM,定時(shí)遍歷寫入其所有地址的數(shù)據(jù),然后再遍歷讀出所有地址的數(shù)據(jù)。通過(guò)Quartus II中集成的在線邏輯分析儀SiganlTapII

2018-06-30 17:16:32

職位描述:1.負(fù)責(zé)我司數(shù)據(jù)通信產(chǎn)品的FPGA和ASIC應(yīng)用的仿真驗(yàn)證工作; 2.著重負(fù)責(zé)仿真驗(yàn)證平臺(tái)系統(tǒng)的搭建和仿真驗(yàn)證方法的引進(jìn); 3.編寫各種設(shè)計(jì)文檔和標(biāo)準(zhǔn)化資料,實(shí)現(xiàn)資源、經(jīng)驗(yàn)共享。 任職要求

2015-07-16 11:04:49

1、如何從零開始在win平臺(tái)搭建SpinalHDL開發(fā)環(huán)境并跑通第一個(gè)spinal project demo需安裝軟件綜述首先列出需要安裝的軟件,并逐一對(duì)這些軟件的功能和其必要性進(jìn)行說(shuō)明.需要安裝

2022-08-02 15:37:04

李立兵等: 基于M at lab的同步電機(jī)實(shí)時(shí)仿真平臺(tái)基于M a tlab的同步電機(jī)實(shí)時(shí)仿真平臺(tái)李立兵,馮志彪( 同濟(jì)大學(xué) 上海 200092)摘 要:電力系統(tǒng)數(shù)字仿真已成為電力系統(tǒng)研究、試驗(yàn)和人員培訓(xùn)的有效工具。改進(jìn)現(xiàn)有電力系統(tǒng)研究仿真軟件, 開發(fā)用...

2021-09-03 08:38:06

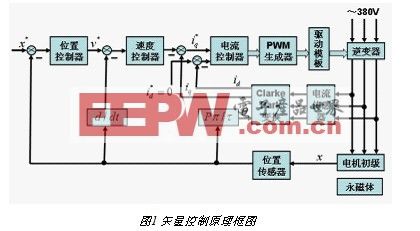

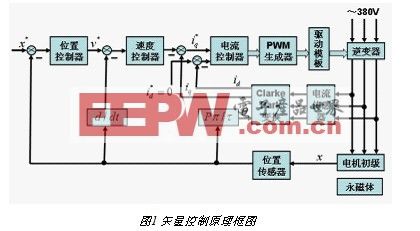

。執(zhí)行器為液壓控制單元、制動(dòng)管路以及制動(dòng)器。傳感器為壓力傳感器,獲取各個(gè)輪缸以及主缸的壓力值,并將壓力信號(hào)傳給控制器和下位機(jī),從而形成一個(gè)閉環(huán)系統(tǒng)。仿真平臺(tái)結(jié)構(gòu)如圖1所示。圖1 仿真平臺(tái)結(jié)構(gòu)圖 仿真平臺(tái)

2011-09-07 09:09:25

基于STM32-XPC仿真平臺(tái)的構(gòu)架 xPC Target是MathWorks公司的MATLAB提供的一個(gè)基于RTW(Real-Time Workshop)體系框架的附加產(chǎn)品,是一種用于產(chǎn)品原型開發(fā)

2021-08-18 07:20:04

數(shù)字預(yù)失真平臺(tái)系統(tǒng)模型是怎樣構(gòu)成的?如何對(duì)數(shù)字預(yù)失真平臺(tái)系統(tǒng)進(jìn)行仿真測(cè)試?

2021-04-21 07:23:32

以下是課程設(shè)計(jì)的要求,各位大神幫幫忙唄,小弟實(shí)在不會(huì),所以來(lái)著請(qǐng)教各位大神,謝謝!{:4_107:}意義:建立與本科《數(shù)字信號(hào)處理》課理論教學(xué)相配套的實(shí)驗(yàn)教學(xué)仿真平臺(tái)。要求:a、 構(gòu)建總體結(jié)構(gòu)框架

2013-12-27 13:04:39

的搭建輕車熟路,一個(gè)基本的測(cè)試平臺(tái)往往是長(zhǎng)這樣的:作為一個(gè)優(yōu)秀的硬件描述語(yǔ)言,SpinalHDL通過(guò)集成第三方開源仿真器接口調(diào)用同樣可以完成仿真驗(yàn)證。DUT為簡(jiǎn)單起見(jiàn),這里采用一個(gè)簡(jiǎn)單的加法器

2022-07-20 14:38:07

求適用于K60的智能車仿真平臺(tái)。

2017-01-05 18:36:55

(STAR開發(fā)板)Le***n06 軟件安裝配置說(shuō)明Le***n07 第一個(gè)工程創(chuàng)建、源碼輸入與仿真Le***n08 第一個(gè)工程編譯、引腳分配、下載與固化Le***n09 FPGA入門實(shí)例:撥碼開關(guān)

2020-03-20 09:36:01

功能之強(qiáng)大,他集成了keil,Altium Designer和Multisim的基本功能,可以進(jìn)行代碼創(chuàng)作,繪制電路板以及電路仿真。下面就來(lái)建立我們的第一個(gè)流水燈工程。第一步,先安裝proteus,這...

2021-12-08 07:48:26

復(fù)制與粘貼4.6.2ISE設(shè)置4.7PlatformCable USB驅(qū)動(dòng)安裝4.8串口芯片驅(qū)動(dòng)安裝4.8.1驅(qū)動(dòng)安裝4.8.2設(shè)備識(shí)別勇敢的芯伴你玩轉(zhuǎn)Xilinx FPGA第5章基于仿真的第一個(gè)工程

2017-11-27 12:23:53

Adams 是一款系統(tǒng)級(jí)多體動(dòng)力學(xué)仿真平臺(tái),被廣泛應(yīng)用于汽車、能源、重型機(jī)械等多個(gè)行業(yè)。該工具凝聚了豐富行業(yè)應(yīng)用經(jīng)驗(yàn),能夠快速進(jìn)行系統(tǒng)級(jí)的運(yùn)動(dòng)學(xué)、動(dòng)力學(xué)仿真、系統(tǒng)級(jí)模態(tài)及振動(dòng)分析、與控制系統(tǒng)

2022-05-10 10:18:24

概述隨著智能駕駛系統(tǒng)功能的提升,駕駛員與智能駕駛系統(tǒng)之間的交互功能越來(lái)越多,測(cè)試的復(fù)雜度也越來(lái)越高。經(jīng)緯恒潤(rùn)新推出的虛擬駕駛仿真平臺(tái),可以在實(shí)驗(yàn)室環(huán)境下提供逼真的虛擬駕駛場(chǎng)景、真實(shí)的駕駛座艙環(huán)境

2022-06-07 11:34:49

研究了EPA產(chǎn)品開發(fā)仿真平臺(tái)的設(shè)計(jì)原理和各個(gè)模塊實(shí)現(xiàn)的技術(shù),說(shuō)明了仿真平臺(tái)軟硬件的內(nèi)部結(jié)構(gòu)以及它們之間的連接,介紹了EPA開發(fā)仿真平臺(tái)中核心的PTP技術(shù)、CSME技術(shù)、EPA設(shè)備管

2009-03-17 10:08:52 22

22 為研究適用于低軌衛(wèi)星網(wǎng)絡(luò)的協(xié)議與算法,在OPNET中搭建仿真平臺(tái),包括衛(wèi)星網(wǎng)絡(luò)拓?fù)涞脑O(shè)計(jì)、節(jié)點(diǎn)模型、進(jìn)程模型以及鏈路模型的建立。該平臺(tái)能模擬低軌衛(wèi)星網(wǎng)絡(luò)路由表的建

2010-08-11 16:20:32 0

0 三維虛擬仿真平臺(tái),三維虛擬仿真平臺(tái)是什么意思

1. 概述

三維虛擬仿真平臺(tái)旨在建設(shè)一個(gè)具有大范圍的海量

2010-04-10 11:35:34 5770

5770 永磁同步直線電機(jī)硬件在環(huán)實(shí)時(shí)仿真平臺(tái)

挑戰(zhàn):采用LabView8.6.1和兩個(gè)cRIO軟硬件平臺(tái)快速搭建一套永磁同步直線電機(jī)硬件在環(huán)實(shí)時(shí)仿真系統(tǒng)。

2010-05-13 10:24:07 2168

2168

本文基于PXI和cRIO搭建了ESP硬件在環(huán)仿真平臺(tái)。平臺(tái)可以將控制器放在仿真回路中,方便對(duì)控制器中的算法進(jìn)行測(cè)試。仿真試驗(yàn)臺(tái)的搭建提高了ESP控制算法的開發(fā)速度。

2011-08-26 10:31:27 6238

6238

ADS無(wú)線協(xié)同仿真平臺(tái)

2011-10-11 16:30:41 0

0 文中闡述了4G無(wú)線仿真平臺(tái)的搭建,描述了系統(tǒng)的架構(gòu)和處理流程,并介紹了相關(guān)模塊,以及模塊間的交互過(guò)程。重點(diǎn)闡述了模塊間通信的介質(zhì)-環(huán)形緩沖區(qū)的使用,使得數(shù)據(jù)能夠在模塊間安全的傳遞。該環(huán)形緩沖區(qū)具有

2015-12-18 16:03:05 13

13 Xilinx FPGA工程例子源碼:FPGA語(yǔ)音通信平臺(tái)設(shè)計(jì)實(shí)例

2016-06-07 14:13:43 13

13 Xilinx合作伙伴和客戶展示了他們?nèi)绾问褂肸ynq仿真平臺(tái)。

2019-01-03 13:14:43 4329

4329 本文檔詳細(xì)介紹的是FPGA視頻教程之QuartusII使用簡(jiǎn)介與第一個(gè)工程實(shí)例的詳細(xì)資料說(shuō)明主要內(nèi)容包括了:1.如何安裝軟件?,2.如何獲取免費(fèi)的License?,3.如何安裝I icense?

2019-03-01 16:13:00 5

5 基于QuartusII通過(guò)實(shí)驗(yàn)板上的KEY1按鈕控制FPGA核心板上的第一個(gè)LED燈。本實(shí)驗(yàn)比較簡(jiǎn)單,使用本站FPGA開發(fā)板或者CPLD開發(fā)板以及其它FPGA開發(fā)板都可進(jìn)行實(shí)驗(yàn)。下面實(shí)驗(yàn)?zāi)康模和ㄟ^(guò)該實(shí)例學(xué)習(xí),可以了解FPGA的基本開發(fā)流程,熟識(shí)quartusII軟件基本功能的使用。

2019-03-07 15:41:01 8618

8618 復(fù)雜嵌入式系統(tǒng)仿真平臺(tái)(嵌入式開發(fā)板有哪些功能模塊)-該文檔為復(fù)雜嵌入式系統(tǒng)仿真平臺(tái)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 13:59:06 5

5 基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)講解(電源技術(shù)國(guó)內(nèi)外的發(fā)展)-該文檔為基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-08-31 18:35:25 18

18 基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)總結(jié)(中遠(yuǎn)通電源技術(shù))-該文檔為基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-15 11:52:40 10

10 基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)(通信電源技術(shù)是什么級(jí)別期刊)-該文檔為基于dSPACE半實(shí)物仿真平臺(tái)的設(shè)計(jì)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 11:03:03 10

10 基于dSPACE半實(shí)物仿真平臺(tái)設(shè)計(jì)(電源技術(shù)投稿流程)-該文檔為基于dSPACE半實(shí)物仿真平臺(tái)設(shè)計(jì)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-09-16 11:05:48 26

26 功能之強(qiáng)大,他集成了keil,Altium Designer和Multisim的基本功能,可以進(jìn)行代碼創(chuàng)作,繪制電路板以及電路仿真。下面就來(lái)建立我們的第一個(gè)流水燈工程。第一步,先安裝proteus,這...

2021-11-25 14:36:11 13

13 遙控器仿真平臺(tái)(M34559G6)用戶手冊(cè)

2023-05-08 18:39:58 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論