關(guān)鍵詞: 1200ZE , Lattice , MachXO2 , PLD

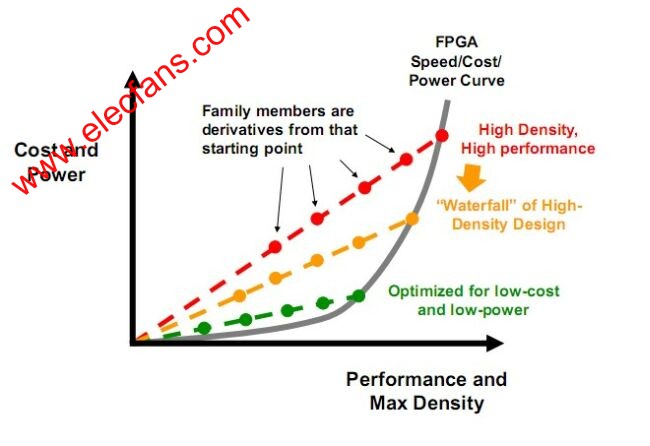

Lattice公司的MachXO2系列是非易失性的無(wú)限制重新配置的可編程邏輯器件(PLD),具有低容量PLD,低成本,低功耗和高系統(tǒng)集成度等特點(diǎn),采用65nm閃存工藝技術(shù),和MachXO PLD相比,邏輯容量增加3x,嵌入存儲(chǔ)器曾加10x,靜態(tài)功耗降低100x,查找表(LUT)從256 到 6864,主要用在系統(tǒng)應(yīng)用如通信架構(gòu),計(jì)算,高端工業(yè)設(shè)備和高端醫(yī)療設(shè)備以及消費(fèi)類電子如智能手機(jī),GPS,數(shù)碼相機(jī)和移動(dòng)計(jì)算等.本文介紹了MachXO2系列主要特性, MachXO2-1200器件框圖以及MachXO2 1200ZE評(píng)估板主要特性,方框圖,電路圖與材料清單.

2012-5-3 09:24:08 上傳

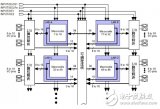

The MachXO2 family of ultra low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I2C controller and timer/counter. These fea-tures allow these devices to be used in low cost, high volume consumer and system applications. The MachXO2 devices are designed on a 65nm non-volatile low power process. The device architecture has sev-eral features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family. The MachXO2 devices are available in two versions – ultra low power (ZE) and high performance (HC and HE) devices.

The ultra low power devices are offered in three speed grades -1, -2 and -3, with -3 being the fastest. Sim-ilarly, the high-performance devices are offered in three speed grades: -4, -5 and -6, with -6 being the fastest. HC devices have an internal linear voltage regulator which supports external VCC supply voltages of 3.3V or 2.5V. ZE and HE devices only accept 1.2V as the external VCC supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other. The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5x2.5 mm WLCSP to the 23x23 mm fpBGA. MachXO2 devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters. The pre-engineered source synchronous logic implemented in the MachXO2 device family supports a broad range of interface standards, including LPDDR, DDR, DDR2 and 7:1 gearing for display I/Os.

The MachXO2 devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compati-bility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a “per-pin” basis. A user-programmable internal oscillator is included in MachXO2 devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and sim-ilar state machines. The MachXO2 devices also provide flexible, reliable and secure configuration from on-chip Flash memory. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I2C port. Additionally, MachXO2 devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability. Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO2 family of devices. Popular logic synthesis tools provide synthesis library support for MachXO2. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO2 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification. Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE™ modules, including a number of reference designs licensed free of charge, optimized for the MachXO2 PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increas-ing their productivity.

MachXO2系列主要特性:

MachXO2系列產(chǎn)品性能表:

2012-5-3 09:24:08 上傳

下載附件 (35.59 KB)

2012-5-3 09:24:08 上傳

下載附件 (39.55 KB)圖1.MachXO2-1200器件框圖

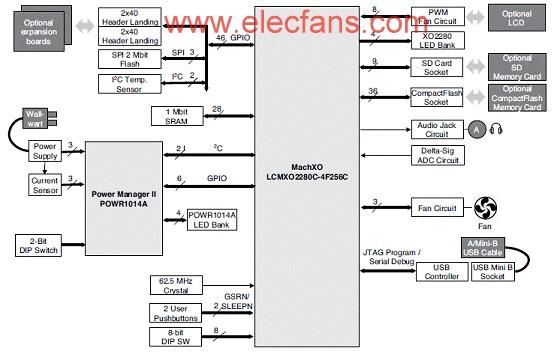

MachXO2 1200ZE評(píng)估板

This user’s guide describes how to start using the MachXO2-1200ZE Breakout Board, an easy-to-use platform for evaluating and designing with the MachXO2-1200ZE PLD. Along with the board and accessories, this kit includes a pre-loaded demonstration design. You may also reprogram the on-board MachXO2-1200ZE device to review your own custom designs.

MachXO2 1200ZE評(píng)估板包括:

–MachXO2-1200ZE PLD (LCMXO2-1200ZE-1TG144C)

–USB mini-B connector for power and programming

–Eight LEDs

–60-hole prototype area

–Four 2x20 expansion header landings for general I/O, JTAG, and external power

–1x8 expansion header landing for JTAG

–3.3V and 1.2V supply rails

• MachXO2-1200ZE Breakout Board – The board is a 3” x 3” form factor that features the following on-board components and circuits:

• Pre-loaded Demo – The kit includes a pre-loaded counter design that highlights use of the embedded MachXO2-1200ZE oscillator and programmable I/Os configured for LED drive.

• USB Connector Cable – The board is powered from the USB mini-B socket when connected to a host PC. The USB channel also provides a programming interface to the LCMXO2-1200ZE JTAG port.

• Lattice Breakout Board Evaluation Kits Web Page

2012-5-3 09:24:08 上傳

下載附件 (65.65 KB)圖2.MachXO2 1200ZE評(píng)估板外形圖

2012-5-3 09:24:08 上傳

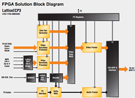

下載附件 (18.57 KB)圖3.MachXO2 1200ZE評(píng)估板方框圖

2012-5-3 09:24:08 上傳

下載附件 (9.8 KB)圖4.MachXO2 1200ZE評(píng)估板電路圖:框圖

2012-5-3 09:24:08 上傳

下載附件 (19.46 KB)圖5.MachXO2 1200ZE評(píng)估板電路圖:USB和JTAG接口

2012-5-3 09:24:08 上傳

下載附件 (20.43 KB)圖6.MachXO2 1200ZE評(píng)估板電路圖:FPGA(1)

2012-5-3 09:24:08 上傳

下載附件 (23.42 KB)圖7.MachXO2 1200ZE評(píng)估板電路圖: FPGA(2)

2012-5-3 09:24:08 上傳

下載附件 (15.68 KB)圖8.MachXO2 1200ZE評(píng)估板電路圖: LED電源

MachXO2 1200ZE評(píng)估板材料清單:

2012-5-3 09:24:08 上傳

下載附件 (56.53 KB)詳情請(qǐng)見(jiàn):

38834[1].pdf (7.4 MB, 下載次數(shù): 6)

2012-5-3 11:11:38 上傳

下載次數(shù): 6下載積分: 積分 -1 和

EB68[1].pdf (768.1 KB, 下載次數(shù): 2)

2012-5-3 11:12:39 上傳

下載次數(shù): 2下載積分: 積分 -1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論