接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計要求會更嚴格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進行PCB布線設(shè)計。 高速信號布線時盡量少打孔

2023-08-02 08:41:11 1437

1437

高速PCB布線實踐指南詳細介紹(例題分析)

雖然印制電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往是電路設(shè)計過程的最后幾個步驟之一。高速PCB布線有很多

2009-12-04 09:30:59 819

819 高速電路PCB電源布線技巧

PCB設(shè)計來說電源處理好壞直接關(guān)系到整個電路板的性能。下面我們分析一下高速電路PCB板的電源布線需要注意的地方和技

2010-03-21 18:29:39 2744

2744

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計要求會更嚴格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進行PCB布線設(shè)計。 高速信號布線時盡量

2023-08-01 18:10:06 1266

1266

在高速PCB的設(shè)計過程中,布線是技巧最細、限定最高的,工程師在這個過程中往往會面臨各種問題。本文將首先對PCB做一個基礎(chǔ)的介紹,同時對布線的原則做一個簡單講解,最后還會帶來非常實用的四個PCB布線的技巧和要領(lǐng)。

2016-11-10 11:00:28 4638

4638 快速理解高速layout設(shè)計 ? 在高速PCB電路的布線中需要注意些什么?

2021-03-05 06:00:06

PCB布線設(shè)計原理在當今激烈競爭的電池供電市場中,由于成本指標限制,設(shè)計人員常常使用雙面板。盡管多層板(4層、6層及8層)方案在尺寸、噪聲和性能方面具有明顯優(yōu)勢,成本壓力卻促使工程師們重新考慮其布線

2009-11-24 10:58:51

PCB布線在PCB設(shè)計中,布線是完成產(chǎn)品設(shè)計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設(shè)計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層

2018-12-07 09:44:39

PCB設(shè)計工程師在設(shè)計PCB時,往往很想使用自動布線。通常,純數(shù)字的電路板(尤其信號電平比較低,電路密度比較小時)采用自動布線是沒有問題的。但是,在設(shè)計模擬、混合信號或高速電路板時,如果采用PCB設(shè)計軟件的自動布線工具,可能會出現(xiàn)一些問題,甚至很可能帶來嚴重的電路性能問題。

2019-07-10 06:11:44

,這就導(dǎo)致了急劇上升的邊緣速率。無端接設(shè)計中的邊緣速率將會引發(fā)反射和信號質(zhì)量問題。 串擾 在高速信號設(shè)計中,密集路徑往往會導(dǎo)致串擾——在PCB上,走線間的電磁耦合關(guān)聯(lián)現(xiàn)象。 串擾可以是同一層上走線

2018-09-19 15:41:05

本人想做一個陣列接收模塊,初步想法是FPGA+adc芯片,采集16Khz左右正弦信號,得到其相位與幅度信息。如果要做64路,adc采用并行ad,這樣需要的IO口會很多,但如果不用一片fpga就不能同時采集信號。想問一下有沒有什么好的解決方案呢?求大佬關(guān)注一下!!!謝謝!!!

2019-03-06 19:01:51

在pcb設(shè)計中FPGA與高速并行DAC的布線應(yīng)該注意什么?

2023-04-11 17:30:54

高速PCB布線實踐指南

2019-06-12 21:52:52

高速PCB布線實踐指南_(上)

2012-08-20 16:26:24

在PCB設(shè)計中,布線是完成產(chǎn)品設(shè)計的重要步驟,可以說前面的準備工作都是為它而做的,在整個PCB設(shè)計中,以布線的設(shè)計過程限定最高,技巧最細、工作量最大。要想很好地掌握它,還需廣大電子工程設(shè)計人員去自已

2012-07-20 19:11:26

設(shè)計高速系統(tǒng)并不僅僅需要高速元件,更需要天才和仔細的設(shè)計方案。設(shè)備模擬方面的重要性與數(shù)字方面是一樣的。在高速系統(tǒng)中,噪聲問題是一個最基本的考慮。高頻會產(chǎn)生輻射進而產(chǎn)生干擾。邊緣極值的速度可以產(chǎn)生振鈴

2021-03-31 06:00:00

設(shè)計高速系統(tǒng)并不僅僅需要高速元件,更需要天才和仔細的設(shè)計方案。設(shè)備模擬方面的重要性與數(shù)字方面是一樣的。在高速系統(tǒng)中,噪聲問題是一個最基本的考慮。高頻會產(chǎn)生輻射進而產(chǎn)生干擾。邊緣極值的速度可以產(chǎn)生振鈴

2022-04-18 15:22:08

高速PCB布線指南

2012-08-20 15:59:45

在高速PCB的設(shè)計過程中,布線是技巧最細、限定最高的,工程師在這個過程中往往會面臨各種問題。本文將首先對PCB做一個基礎(chǔ)的介紹,同時對布線的原則做一個簡單講解,最后還會帶來非常實用的四個PCB布線

2018-11-28 11:41:21

15條高速PCB布線經(jīng)驗分享

2021-01-29 06:10:51

高速PCB布線需要遵守哪些規(guī)則?比如SATA III它對布線長度有要求嗎?對穿過的過孔有要求嗎?

2016-04-27 20:58:12

必須相互靠近布線; 2、兩條跡線的長度必須匹配。 當一對必須繞彎道布線時,問題會出現(xiàn),如下圖所示。問題是在兩個未對齊的組件之間路由差分對。圖A中的解決方案存在缺陷,因為外側(cè)的軌道明顯長于內(nèi)側(cè)的軌道

2023-04-12 15:20:37

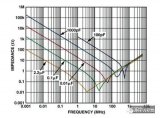

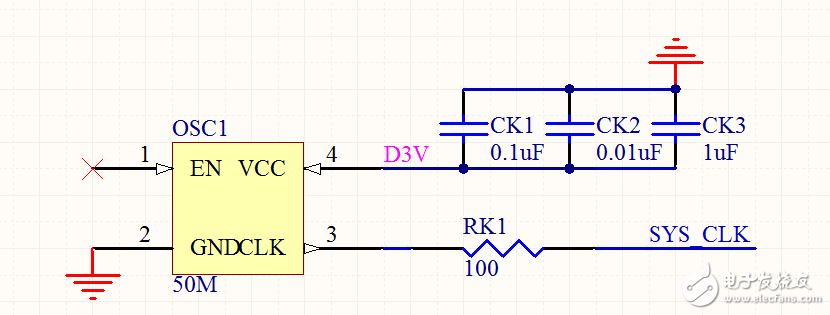

`高速PCB板的電源布線設(shè)計隨著集成電路工藝和集成度的不斷提高,集成電路的工作電壓越來越低,速度越來越快。進入新世紀后,CPU和網(wǎng)絡(luò)都邁入了GHZ的時代,這對于PCB板的設(shè)計提出了更高的要求。本文正是基于這種背景下,對高速PCB設(shè)計中最重要的環(huán)節(jié)之一——電源的合理布局布線進行分析和探討。`

2009-12-09 13:58:28

高速PCB板的電源布線設(shè)計

2009-03-26 21:50:55

PCB(印制電路板)布線在高速電路中具有關(guān)鍵作用,那么高速PCB的布線需要考慮哪些事項呢? 這個問題大家考慮過嗎?

2019-08-02 06:46:56

本帖最后由 eehome 于 2013-1-5 10:01 編輯

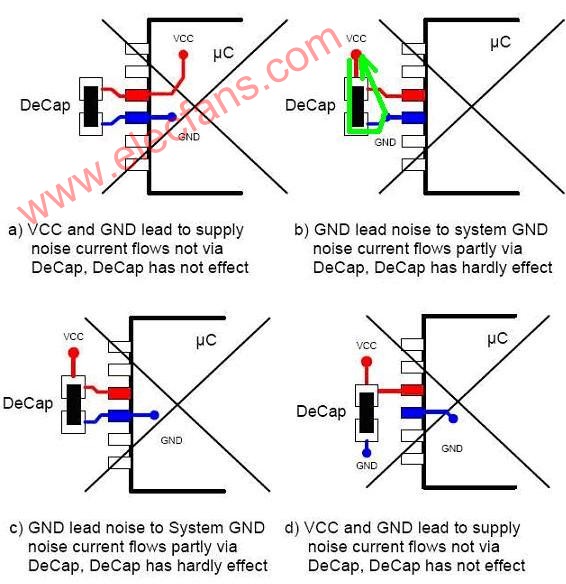

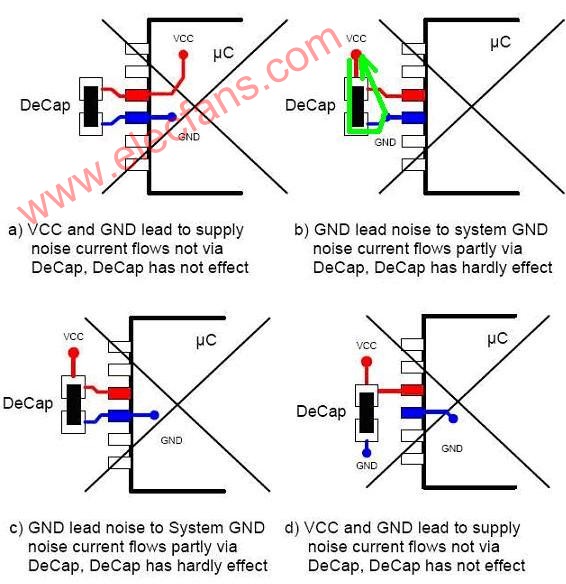

高速PCB板信號接地設(shè)計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設(shè)計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲和電磁輻射問題的方法。

2012-03-31 14:31:52

高速PCB設(shè)計中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-02-16 15:06:01

` 本帖最后由 飛翔的烏龜005 于 2017-2-10 10:43 編輯

高速PCB設(shè)計中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應(yīng)從PIN中心引出(一般采用

2017-02-10 10:42:11

在PCB設(shè)計中,布線是完成產(chǎn)品設(shè)計的重要步驟,可以說前面的準備工作都是為它而做的, 在整個PCB中,以布線的設(shè)計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、 雙面布線及多層布線。布線

2012-08-13 16:30:47

在高速pcb設(shè)計中,經(jīng)常聽到要求阻抗匹配。而設(shè)計中導(dǎo)致阻抗不匹配的原因有哪些呢?一般又對應(yīng)著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

影響高速信號鏈設(shè)計性能的機制是什么?高速ADC設(shè)計中的PCB布局布線技巧有哪些?

2021-04-21 06:29:52

高速信號PCB布線中降低寄生電感的具體措施

2021-03-08 08:49:46

的高速數(shù)據(jù)采集卡,單塊板卡可實現(xiàn)2通道、14bit、1GS/s的快速、高精度脈沖數(shù)據(jù)采集,整個系統(tǒng)可實現(xiàn)多板卡、更多通道的同步數(shù)據(jù)采集工作。經(jīng)過檢測,用戶信號脈寬在20ns左右,利用以上解決方案,實現(xiàn)

2016-03-28 15:11:59

目前,無論是ARM、DSP、FPGA等大多數(shù)封裝基本上都是BGA或MBGA,BGA在PCB布線上的可靠性還都基本上能滿足,但是MBGA封裝的:間距在0.5mm一下的,在PCB中布線到PCB加工制成,特別對于高速信號來說,布線會造成信號完整性的問題及制版質(zhì)量問題,請教各位大俠,如何解決???

2022-04-23 23:15:51

量產(chǎn)。 Cadence PCB設(shè)計解決方案集成在以下產(chǎn)品中: Cadence Allegro PCB Design LXL和GXL Cadence OrCAD PCB Designer、Cadence

2018-08-30 10:49:16

本文探討PADS在PCB布局布線中如何解決高速問題。點擊下載

2019-04-29 17:24:10

的數(shù)據(jù)寫到 FPGA 的發(fā)送 FIFO 中,速率約為4.5GB/s,該采集卡具備上位機讀寫 FPGA 用戶寄存器的功能,讀寫接口為 local bus 接口,方便易用。1. 系統(tǒng)結(jié)構(gòu)圖方案一2. 采用此

2021-05-19 08:58:02

概述由于VPX系統(tǒng)的自身特點及優(yōu)勢,成為當下數(shù)據(jù)采集領(lǐng)域的熱點,很多工程應(yīng)有都采用了VPX相關(guān)的解決方案。北京坤馳科技有限公司結(jié)合其具備技術(shù)優(yōu)勢的多通道同步采集存儲板卡和緊湊型的3U VPX機箱

2016-03-25 15:19:36

等高頻信號線都是要求盡可能的走線越短越好。 3、高速電子器件管腳間的引線彎折越少越好 高頻電路布線的引線最好采用全直線,需要轉(zhuǎn)折,可用45度折線或者圓弧轉(zhuǎn)折,這種要求在低頻電路中僅僅用于提高銅箔

2017-01-20 11:44:22

對數(shù)據(jù)采集與處理系統(tǒng)提出了新的更高的要求,即高速度、高精度和高實時性。對數(shù)據(jù)采集與處理系統(tǒng)的設(shè)計,有以下3種方案可供選擇:(1)A/D+DSP方案在傳統(tǒng)的高速信號處理中,大多采用這種方案。將A/D、D

2019-07-05 06:41:27

高速、超寬帶信號采集技術(shù)在雷達、天文和氣象等領(lǐng)域應(yīng)用廣泛。高采樣率需要高速的模/數(shù)轉(zhuǎn)換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現(xiàn)的數(shù)據(jù)采集對FPGA的性能和PCB布局布線技術(shù)提出了嚴峻的挑戰(zhàn)。

2019-11-08 06:34:52

使用高速轉(zhuǎn)換器時,有哪些重要的PCB布局布線規(guī)則?

2021-04-21 06:58:58

高速PCB設(shè)計中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 16:04:35

高速PCB設(shè)計中常規(guī)PCB布線,有以下基本要求:(1)QFP、SOP等封裝的矩形焊盤出線,應(yīng)從PIN中心引出(一般采用鋪shape)(2)布線到板邊的距離不小于20MIL。(3)金屬外殼器件下

2017-01-23 09:36:13

PCB分區(qū)為模擬部分和數(shù)字部分,模擬信號在電路板所有層的模擬區(qū)內(nèi)布線,而數(shù)字信號在數(shù)字電路區(qū)內(nèi)布線,在這種情況下,數(shù)字信號返回電流不會流入到模擬信號的地。經(jīng)過以上設(shè)計,噪聲影響明顯降低。4 接口解決方案

2018-12-18 10:22:18

目前,在數(shù)據(jù)采集系統(tǒng)的硬件設(shè)計方案中,有采用通用單片機和USB相結(jié)合的方案,也有采用DSP和USB相結(jié)合的方案,前者雖然硬件成本低,但是時鐘頻率較低,難以滿足數(shù)據(jù)采集系統(tǒng)對速度要求;后者雖然可以實現(xiàn)

2019-09-05 07:22:57

時候根本沒有選擇。隨著信號速度越來越快,空間越來越小,像對埋孔這類的額外需求開始增加,這些都應(yīng)成為PCB解決方案的成本要素。 在采用帶狀線布線時,信號被FR-4材料夾在中間。而微帶線時,一條導(dǎo)體是裸露

2018-08-30 10:49:26

PCB解決方案的成本要素。 在采用帶狀線布線時,信號被FR-4材料夾在中間。而微帶線時,一條導(dǎo)體是裸露在空氣中的。因為空氣的介電常數(shù)最低(Er= 1),故頂層最適合布設(shè)一些關(guān)鍵信號,如時鐘信號或者高頻

2018-11-27 10:07:39

從事的電路設(shè)計那樣輕松。在設(shè)計最終能夠正常工作、有人對性能作出肯定之前,PCB設(shè)計師都面臨著許多新的挑戰(zhàn)。這正是目前高速PCB設(shè)計的現(xiàn)狀--設(shè)計規(guī)則和設(shè)計指南不斷發(fā)展,如果幸運的話,它們會形成一個成功

2019-07-10 06:22:53

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

大神手把手教你如何進行pcb高速線布線

2021-05-13 06:22:15

- 安裝在高速 ADC(包括高速運算放大器、FIFO 和 SRAM)的周圍。ADC 的數(shù)據(jù)輸出流被寫入 FIFO,存儲在 SRAM 塊中,并在 FPGA 的數(shù)據(jù)采集邏輯的控制下通過寄存器直接發(fā)送至外界

2012-12-12 11:48:15

深入了解PCB設(shè)計,并且合理利用。熱門PCB設(shè)計技術(shù)方案:PCB設(shè)計的核心與解決方案高速PCB中電源完整性的設(shè)計闡述DFM技術(shù)在PCB設(shè)計中的應(yīng)用闡述高速DSP系統(tǒng)的電路板級電磁兼容性設(shè)計高速PCB

2014-12-16 13:55:37

顯示了 FPGA 開發(fā)套件中典型的 FPGA 電源解決方案。設(shè)計該方案除了要選擇正確的器件和電感器外,還需要具備一些其它的專業(yè)知識。例如,需要考慮部件放置和板面布局方面的細節(jié)。圖 1. 典型的 FPGA

2022-11-23 07:14:47

綜合布線系統(tǒng)憑借尖端的技術(shù)與智能化設(shè)計,具有無與倫比的優(yōu)越性。那么誰知道綜合布線系統(tǒng)中的屏蔽技術(shù)具體有哪些解決方案嗎?

2019-08-06 06:28:23

誰有高速PCB布局布線規(guī)范,謝謝

2020-04-16 21:10:10

高速PCB板的電源布線設(shè)計:本文分析討論了高速PCB板上由于高頻信號干擾和走線寬度的減小而產(chǎn)生的電源噪聲和壓降,并提出了高速PCB的電源模型,采用電源總線網(wǎng)絡(luò)布線,選取合適

2009-03-24 14:08:40 0

0 本文針對高速PCB板信號接地設(shè)計中存在接地噪聲及電磁輻射等問題,提出了高速PCB接地模型,并從PCB設(shè)計中布線策略的分析和去耦電容的使用等幾個方面討論了解決高速PCB板的接地噪聲

2009-12-08 14:53:23 63

63 本內(nèi)容詳細介紹了高速PCB設(shè)計的布局布線優(yōu)化方法,歡迎大家下載學(xué)習(xí)

2011-09-27 16:22:33 0

0 恒頤基于ARM+FPGA的高速同步數(shù)據(jù)采集方案,解決了數(shù)據(jù)采集的同步性問題,與以往的數(shù)據(jù)采集方案相比,具有高精度、高速率、多參數(shù)同步測量、實時處理、網(wǎng)絡(luò)傳輸不受區(qū)域限制等特點

2012-11-27 10:51:24 1198

1198 高速PCB布線實踐指南,只是理論知識,不是實際軟件操作

2015-12-11 16:59:38 0

0 高速PCB布線實踐指南,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:41:19 0

0 高速PCB布線實踐指南_(上冊),好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:41:19 0

0 高速PCB板的電源布線設(shè)計,有需要的下來看看。

2016-02-22 16:14:48 31

31 基于FPGA高速數(shù)據(jù)采集的解決方案,下來看看

2016-05-11 09:46:01 13

13 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)設(shè)計,用ad芯片和sdram構(gòu)成高速數(shù)據(jù)采集系統(tǒng)。

2016-05-17 09:49:51 35

35 本文針對由FPGA構(gòu)成的高速數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)處理能力弱的問題,提出FPGA與單片機實現(xiàn)數(shù)據(jù)串行通信的解決方案。

2017-02-11 14:30:00 11246

11246 采用FPGA實現(xiàn)對AD 輸出數(shù)據(jù)的高速采集

2017-08-30 17:16:02 35

35 簡述了關(guān)于高速設(shè)計對應(yīng)問題的相關(guān)設(shè)計領(lǐng)域,包括PCB分層設(shè)計,PCB布局設(shè)計和PCB布線設(shè)計方面的各種解決方案。

2018-06-22 10:17:00 1400

1400

雖然印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計過程的最后幾個步驟之一。

2020-10-21 11:23:37 3283

3283

在布線電路板時, PCB 設(shè)計人員的任務(wù)很艱巨。當涉及到高速 PCB 布線和信號時,事情就變得更加復(fù)雜。為了幫助不同的 PCB 設(shè)計人員,已列出了一系列最佳的高速 PCB 布線實踐,以幫助他們實現(xiàn)

2020-10-27 19:12:24 2847

2847 讓你布線少走彎道的15條高速PCB布線經(jīng)驗分享

2022-02-12 10:44:53 5487

5487 讓你布線少走彎道的15條高速PCB布線經(jīng)驗分享

2021-03-04 06:24:26 31

31 AN-1142: 高速ADC PCB布局布線技巧

2021-03-20 22:11:52 28

28 雖然印刷電路板(PCB)布線在高速電路中具有關(guān)鍵的作用,但它往往只是電路設(shè)計過程的最后幾個步驟之一。高速PCB布線有很多方面的問題,關(guān)于這個主題已有大量的文獻可供參考。本文主要從實踐的角度來探討高速

2021-06-21 10:58:05 0

0 淺析ROHM的汽車照明解決方案

2021-11-19 14:50:28 5

5 淺析LED電磁兼容解決方案

2022-01-25 16:10:59 10

10 本文主要從實踐的角度來探討高速電路的布線問題。主要目的

在于幫助新用戶當設(shè)計高速電路 PCB 布線時對需要考慮的多

種不同問題引起注意。

2022-10-21 16:09:05 0

0 如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計要求會更嚴格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進行PCB布線設(shè)計。高速信號布線時盡量少打孔

2023-08-03 17:31:07 663

663

高速PCB板的電源布線設(shè)計

2022-12-30 09:22:11 5

5

電子發(fā)燒友App

電子發(fā)燒友App

評論