本文提出了一套基于TMS320F2407芯片的變頻調速系統設計方案,方案中的硬件平臺以DSP為核心,系統中采用SVPWM算法來實現變頻調速。

2013-11-20 11:53:22 4324

4324

本帖最后由 發燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實現PID算法,面臨著小數的計算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

采集數據中的量化噪聲,在進行數據壓縮前采用濾波的預處理技術。介紹LZW算法和滑動濾波算法的基本理論,詳細闡述用單片FPGA實現兩種算法的方法。最終測試結果表明,該設計方案能夠有效濾除數據中的高頻噪聲

2010-04-24 09:05:21

FPGA典型設計方案精華匯總

2012-08-16 16:29:32

)、System Generator和AccelDSP的圖形化設計實例,通過大量的程序實例,全面、精辟地介紹了利用現場可編程門陣列(FPGA)實現數字信號處理的方方面面。本課程首先介紹了當前的FPGA技術

2009-07-21 09:22:42

大多數工程師在碰到需要在 FPGA 中實現諸如正弦、余弦或開平方這樣的數學函數時,首先會想到的是用查找表,可能再結合線性內插或者冪級數(如果有乘法器可用)。不過對這種工作來說,CORDIC 算法

2019-09-19 09:07:16

各位FPGA設計大賽參賽者注意了:小編這里幫大家解釋一下設計方案提交規則和活動時間安排

自4月23日比賽開始,參賽者報名之后即可提交設計方案。設計方案提交的截止日期是活動結束,暨設計方案評選的最后

2012-05-04 10:27:46

你好: 我是一個購買的帳戶,所以我的許可證應該允許訪問所有內容。但是當我使用System Generator for DSP時,系統說我的SysGen簽出許可證失敗了。有人知道怎么解決嗎?謝謝

2019-01-28 07:16:36

FPGA中的數字控制器是什么?System Generator中的PID控制器是如何設計的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個不讓我繼續參與我的硬件協同仿真項目的問題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據我的理解,System Generator是MatLab到RTL的轉換,因此不包括Vivado的優化過程。問題1--是真的。確實,Vivado中的優化將大大改變系統描述,而系統描述不會向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天評估包,Matalb 2014B。簡單地說我想使用FIR編譯器,當我嘗試編輯它的參數時,我得到了兩個錯誤: - 1.“來自MEX

2020-03-24 09:01:59

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統的性能。傳統的實現方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何時才能勝任64位Windows 7?以上來自于谷歌翻譯以下為原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,發現getway in這個模塊參數設置變化導致MATLAB閃退問題,貼圖如下其中getway in 這個模塊數據類型換成定點有符號或者無符號數都不得行,換成布爾值又會出現錯誤,不知為何啊!求教。

2018-01-05 21:43:53

,它的局限性也逐漸暴露出來.在很多計算機信息安全系統中,硬件加密手段被應用到設備中來提高密碼運算速度和系統的安全性. 給出了一種RC4加密算法的FPGA實現方案,相比用軟件實現,該方案速度更快,安全性更高

2012-08-11 11:48:18

)、System Generator和AccelDSP的圖形化設計實例,通過大量的程序實例,全面、精辟地介紹了利用現場可編程門陣列(FPGA)實現數字信號處理的方方面面。本課程首先介紹了當前的FPGA技術

2009-07-21 09:20:11

翻譯成verilog,在FPGA里面實現,即system generator。altera有沒有類似的接口,與matlab可以互連,直接在matlab里設計我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

組的FPGA實現7.7 本章小結第8章基于System Generator的DSP系統開發技術8.1 System Generator的簡介與安裝8.1.1 System Generator簡介

2012-04-24 09:23:33

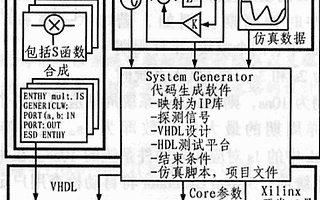

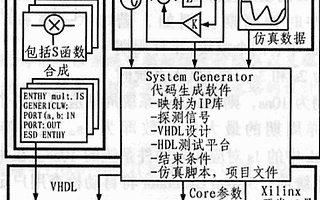

針對實現DSP的設計軟件—System Generator。在使用FPGA為原型平臺運行算法時,它不僅能夠對硬件的真實情況進行仿真,還能夠自動生成硬件實現所需要的硬件描述語言代碼。與語 言設計相比

2019-06-21 06:25:23

二維聲源定位算法仿真設計方案文中提出新的高精度, 快速二維聲源定位算法。計算機采集四個聲音傳感器, 一個風速傳感器和一個風向傳感器的信號, 計算出聲源的位置和當地的聲速。用MatLab語言進行的仿真

2009-12-10 16:24:07

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

使用system generator導入xilinx模塊時,只要連線兩個模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

分享一款不錯的音頻信號采集與AGC算法的DSP設計方案

2021-06-08 06:24:56

本文以星載測控系統為背景,提出了一種基于 Actel Flash FPGA的高可靠設計方案。采用不易發生單粒子翻轉的 flash FPGA芯片,結合 FPGA內部的改進型三模冗余、分區設計和降級重構,實現了高實時、高可靠的系統。

2021-05-10 06:58:47

.Vivado 2016.4與Spartan-6不兼容。據Xilinx稱,Vivado不支持任何早于7系列的設備系列。)根據以下說明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

個System Generator設計中,我想在FPGA運行時改變一些變量。例如,希望能夠從“外部世界”修改特定ASR的長度,或控制多路復用器以手動選擇不同的信道。在設計運行時修改這些參數的常用方法

2019-01-15 10:39:11

在system generator中,我把(-128~127),變為(-1~1),但是下載到硬件中,使用chipscope抓取到的數據確實(-128~127),請問是怎么回事

2016-08-10 15:32:38

上學時做的變頻器設計方案,利用simulink仿真,基于FPGA的變頻器設計方案。

2014-09-10 10:40:12

基于FPGA的數據無阻塞交換設計方案,不看肯定后悔

2021-04-29 06:48:07

有做System Generator處理圖像的嗎?遇到一些問題,一起商量下

2020-09-28 19:04:58

基于STM32的便攜體檢裝置的設計與實現基于STM32的電能質量檢測技術研究基于STM32的EMS液晶顯示觸摸屏設計方案STM32的曼徹斯特編譯碼系統設計STM32微控制器中采用DMA實現方波的產生和捕獲

2018-09-05 16:41:46

多種EDA工具的FPGA設計方案

2012-08-17 10:36:17

嗨,我正在嘗試學習如何使用System Generator來創建自己的IP核。首先,我在DocNav中找到了一個ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

如何用FPGA實現DVB碼流分析功能的嵌入式設計方案?

2021-04-28 06:19:10

各位大佬,我在安裝System Generator時,跟著教程走,發現在vivado中沒有出現System Generator for DSP這個選項,請問是我哪里安裝得不對嗎?

2023-09-26 21:54:58

當我完成SDx 2017.2的安裝時,沒有安裝System Generator的選項。我正在運行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創建一個雙向(inout)端口。我正在嘗試為Xilinx的外部存儲器創建一個接口

2019-05-09 14:36:24

最近在使用system generator設計一個rs編碼譯碼的模型,總的思想是在rs編碼產生信號后,插入一個誤碼,然后作為信號源進行解碼,看是否能夠正常的進行解碼,求解是怎么才能把rs編碼后的信號存儲起來作為信號源

2016-07-20 20:13:59

System Generator for DSP的特點是什么?如何使用System Generator for DSP實現系統級建模?怎么在Matlab中實現數字通信FPGA硬件設計?

2021-04-29 06:20:46

如何去設計一款合理的電子硬件解決方案,從而實現經濟有效的大規模生產與部署?怎樣去驗證可部署目標硬件與軟件算法模型之間的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

“玩轉FPGA:iPad2,賽靈思開發板等你拿”活動持續火爆進行中……………………活動得到了廣大電子工程師積極強烈的支持,為了回報電子工程師和網站會員,現在只需提交fpga設計方案,就有機會獲得賽靈

2012-07-06 17:24:41

有用Xilinx的system generator做圖像處理的嘛?求交流 。我正在用這個做圖像處理,已經用了3個月了,在做一些算法,遇到一些困難,求一起交流學習。發現用這個開發的人真不多啊。

2014-05-09 14:57:21

討論了一種基于FPGA的64點FFT處理器的設計方案,輸入數據的實部和虛部均以16位二進制數表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發平臺對處理器各個的模塊進行設計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結果正確。

2021-04-29 06:25:54

以前,我們有Matlab 2006a和ISE 8.2i,并且正在使用System Generator。我們不得不重新安裝Matlab 2006a以啟用新的工具箱,但現在Simulink中沒有

2018-11-19 14:42:56

小波盲源分離算法的仿真及FPGA實現:提出了一種基于小波變換的盲源分離方法,在理論分析和仿真結果的基礎上,給出了FPGA 的實現方案。針對傳統盲分離算法對源信號統計特征敏

2009-06-21 22:44:09 21

21 System Generator for DSP 是一款具有高抽象層的設計工具,為算法開發人員和系統架構師從 Simulink 算法參考模型過渡到FPGA 硬件實施技術提供了一種高效的途徑,且無需任何 HDL 編碼工作

2010-06-10 08:21:19 29

29

采用Gardner算法,對QPSK調制解調系統中的位同步系統進行設計與實現,大大提高了系統性能和資源利用率。重點闡述采用FPGA開發環境System Generator系統設計工具進行位同

2010-07-21 16:12:40 26

26 用matlab來實現fpga功能的設計

摘要:System Generator for DSP是Xilinx公司開發的基于Matlab的DSP開發工具?熗?時也是一個基于FPGA的信號處理建模和設計工具。

2008-01-16 18:10:54 11207

11207

深入了解賽靈思System Generator中的時間參數

基于模型的設計(MBD)因其在縮小實時系統抽象的數學建模和物理實現之間差距方面的光明前景而備受關注。通過使用相同的

2009-12-29 11:40:30 1300

1300

HDL設計和驗證與System Generator相結合

Xilinx®SystemGeneratoRForDSP是用來協助系統設計的MATLABSimulink模塊集。SystemGeneratorforDSP在熟悉的MATLAB環境中引入XilinxFPGA對象,讓您能夠

2010-01-06 14:39:30 1181

1181

基于FPGA的高速定點FFT算法的設計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學科領域(如信號處理、圖像處理、生物信息學、計算物理

2010-02-09 10:47:50 992

992

多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 670

670

System Generator 工具由 MathWorks 與 Xilinx 合作開發而成,DSP 設計人員可使用 MATLAB 和Simulink 工具在 FPGA 內進行開發和仿真來完善 DSP 設計。 該工具為系統級 DSP 設計與 FPGA 硬件實現的融合起

2011-05-11 18:36:23 224

224 介紹了一種適于TUD 系統的SHA256算法和HMAC算法! 給出了在FPGA上實現SHA256算法和HMAC 算法的一種電路設計方案!并對算法的硬件實現部分進行了優化設計! 給出了FPGA的實現結果

2011-05-16 16:50:45 141

141 Xilinx公司推出的DSP設計開發工具System Generator是在Matlab環境中進行建模,是DSP高層系統設計與Xilinx FPGA之間實現的橋梁。在分析了FPGA傳統級設計方法的基礎上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源碼:System Generator的設計實例

2016-06-07 14:41:57 22

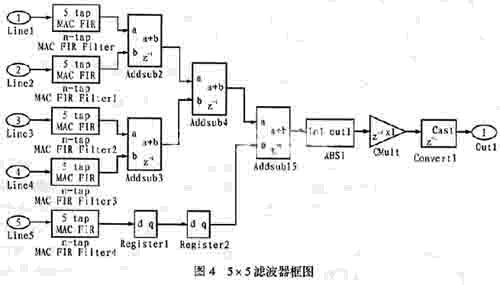

22 環境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實現步驟 1、模型搭建與仿真 在simulink環境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

最新版System Generator支持快速開發和實現基于All Programmable FPGA、SoC和MPSoC的無線電設計 賽靈思日前宣布推出高級設計工具System Generator

2017-02-09 01:23:41 279

279 一直都在System Generator下做圖像處理相關的算法,感覺SysGen挺強大的,前幾天突發奇想,能否直接用SysGen實現數據的通信呢,畢竟一句HDL代碼都不寫對于做FPGA的人來說卻是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設計的方法都試驗過了,更高級的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

system generator是xilinx公司的系統級建模工具,它是擴展mathworks公司的MATLAB下面的simulink平臺,添加了XILINX FPGA專用的一些模塊。加速簡化了FPGA的DSP系統級硬件設計。

2017-02-11 19:21:33 7386

7386

利用System Generator軟件平臺,實現基于模塊化建模方法的變換器建模,并簡化語言編寫控制系統的復雜過程。研究了從MATLAB-Xilinx環境中導出使用模塊化建模方法搭建的控制算法。通過

2017-11-15 14:31:34 4985

4985

現在的FPGA算法的實現有下面幾種方法: 1. Verilog/VHDL 語言的開發 ; 2. system Generator; 3. ImpulsC 編譯器實現從 C代碼到 HDL 語言; 4.

2017-11-17 14:29:06 7298

7298 在FPGA平臺上應用System Generator工具實現了高精度頻率估計Rife算法。不同于傳統的基于HDL代碼和IP核的設計方法,采用System Generator工具可以使復雜算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是專門為數字信號算法處理而推出的模型化設計平臺,可以快速、簡單地將DSP系統的抽象算法轉換成可綜合的、可靠的硬件系統,彌補了大部分對C語言以及Matlab工具很熟悉的DSP工程師對于硬件描述語言VHDL和Verilog HDL認識不足的缺陷。

2018-07-19 09:32:00 3716

3716

。在進行FFT這類并行運算為主的算法時,采用FPGA的優勢不言而喻。用FPGA實現FFT算法進行諧波檢測成為了一大熱點。

2018-07-16 18:22:00 3391

3391

PLD/FPGA 常用開發軟件System Generator 9.10。 業內領先的高級系統級FPGA開發高度并行系統。

2017-11-26 11:34:56 12

12 了解如何將Vivado HLS設計作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設計保存為IP模塊,并了解如何將此IP輕松整合到System Generator for DSP的設計中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多個時鐘域,從而可以實現復雜的DSP系統。

2018-11-27 06:42:00 3450

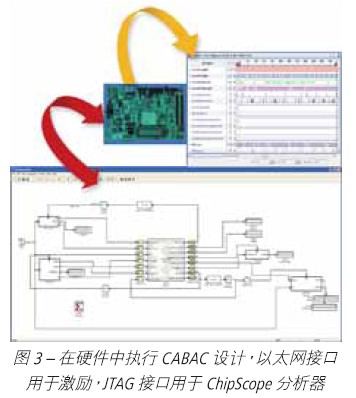

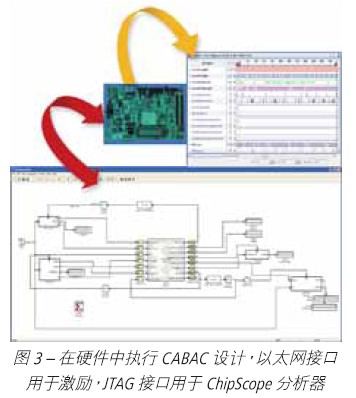

3450 了解如何使用Vivado System Generator for DSP進行點對點以太網硬件協同仿真。

System Generator提供硬件協同仿真,可以將FPGA中運行的設計直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 隨著信息技術和網絡化進程的發展,網絡通信安全問題日益突出。現場可編程門陣列(FPGA)以其自身設計靈活、可靠性高的優點廣泛應用于加密領域。硬件實現的加密算法不占用計算機資源.加密過程完全與外部總線

2019-03-12 08:55:13 7028

7028

專用電路.FPGA具有實現高性能并行算法的能力,是構成高性能可定制數據通路處理器(數字濾波、FFT)的理想器件.如Virtex-II Pro FPGA包含高性能的可編程架構、嵌入式PowerPC處理器和3.125Gbps收發器等.

2020-09-24 20:11:32 1336

1336

框架結構,提出了一種高度并行、緊湊流水線的FPGA實現方案.用Verilog HDL硬件描述語言設計了編碼,在QuARTuSⅡ集成開發環境下,進行了仿真驗證,并寫入FPGA芯片,實現了“十字”形運動估計算法.經測試表明:該設計方案搜索高效、邏輯簡潔,對比全搜索法占用硬件資源較小

2021-02-03 14:46:00 12

12 BLE實驗詳解之藍牙鍵盤設計方案

2021-03-30 16:41:08 58

58 BLE實驗詳解之藍牙血壓計設計方案

2021-03-30 16:46:02 36

36 BLE實驗詳解之藍牙溫度計設計方案

2021-03-30 16:50:07 25

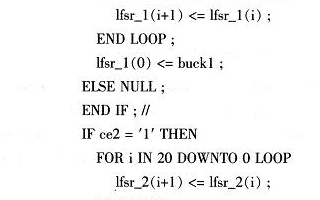

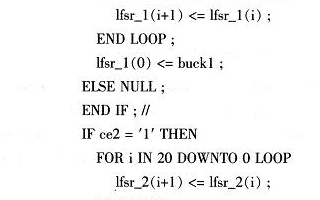

25 基于FPGA的偽隨機數發生器設計方案

2021-06-28 14:36:49 4

4 GPIO模擬UART的算法實現與設計方案

2021-07-07 09:49:29 9

9 本篇博文是面向希望學習 Xilinx System Generator for DSP 入門知識的新手的系列博文第一講。其中提供了有關執行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

本文詳細描述了FPGA實現圖像去霧的實現設計方案,采用暗通道先驗算法實現,并利用verilog并行執行的特點對算法進行了加速;

2023-06-05 17:01:45 862

862

電子發燒友網站提供《基于FPGA的窄帶干擾抑制算法的實現方案.pdf》資料免費下載

2023-11-07 09:29:35 0

0 將再啰嗦一次,詳解從均值濾波到非局部均值濾波算法的原理及實現方式。 細數主要的2D降噪算法,如下圖所示,從最基本的均值濾波到相對最好的BM3D降噪,本文將盡量用最同屬的語言,詳解這些算法的實現流程,并給予一定的 FPGA 加速實現的實現

2023-12-19 16:30:02 242

242

電子發燒友App

電子發燒友App

評論