本文首先闡述了FPGA的原理了,其次分析了FPGA比CPU和GPU快的原理,最后闡述了CPU與GPU的區(qū)別。

2018-05-31 09:00:29 15956

15956

或許有很多人也曾下載過一些測量心跳或幫助減肥的APP,但這些APP最終的結(jié)局不是被冷落就是被卸載。因為大家都對這類醫(yī)療APP抱有同一個疑問:這些醫(yī)療APP的測試結(jié)果真的可信嗎?對我們的健康真的有幫助嗎?移動醫(yī)療大行其道,如何才能解開用戶心中的團團疑問,專業(yè)醫(yī)療平板為您解惑。

2013-01-28 10:34:14 4533

4533 由于FPGA技術(shù)和ARM技術(shù)應用越來越廣泛,通過設計并行總線接口來實現(xiàn)兩者之間的數(shù)據(jù)交換,可以較容易地解決快速傳輸數(shù)據(jù)的需求,因此設計滿足系統(tǒng)要求的FPGA并行總線顯得尤為重要。本文設計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用.

2013-08-15 10:44:19 7204

7204

《日本經(jīng)濟新聞》11月6日報道,在智能手機核心部件CPU(中央處理器)市場上,臺灣半導體企業(yè)聯(lián)發(fā)科技(MediaTek)正在快速擴大市場份額,其原動力就是低價智能手機。該公司的產(chǎn)品性能優(yōu)越、價格實惠,中國大陸的智能手機廠商等紛紛采購...

2013-11-07 09:56:58 706

706 深亞微米時代,傳統(tǒng)材料、結(jié)構(gòu)乃至工藝都在趨于極限狀態(tài),摩爾定律也已有些捉襟見肘。而步入深亞納米時代,晶體管的尺寸就將接近單個原子,無法 再往下縮減。傳統(tǒng)ASIC和ASSP設計不可避免地遭遇了諸如設計流程復雜、生產(chǎn)良率降低、設計周期過長,研發(fā)制造費用劇增等難題,從某種程度上大大放緩 了摩爾定律的延續(xù)。

2015-07-30 11:15:16 1051

1051

全球領先的信息技術(shù)研究和顧問公司Gartner的一項近期調(diào)查顯示,移動設備應用于工作場所尚不成熟。盡管80%的受訪員工都擁有一臺或多臺公司配備的設備,但臺式電腦依然在企業(yè)內(nèi)大行其道,其中過半員工均在使用企業(yè)配備的臺式電腦。

2016-12-14 16:40:19 814

814 圖像處理算法在各種場景中都有廣泛應用,借助于FPGA并行計算的優(yōu)勢可以將算法性能有效提升,但為了提升系統(tǒng)整體性能,僅僅提升某一部分的性能是不夠的,一個好的方法是在FPGA內(nèi)實現(xiàn)全部視頻輸入輸出接口

2020-11-04 12:07:05 3073

3073 FPGA 復用主機網(wǎng)絡的初心是加速網(wǎng)絡和存儲,更深遠的影響則是把 FPGA 之間的網(wǎng)絡連接擴展到了整個數(shù)據(jù)中心的規(guī)模,做成真正 cloud-scale 的「超級計算機」。

2023-04-07 14:16:58 408

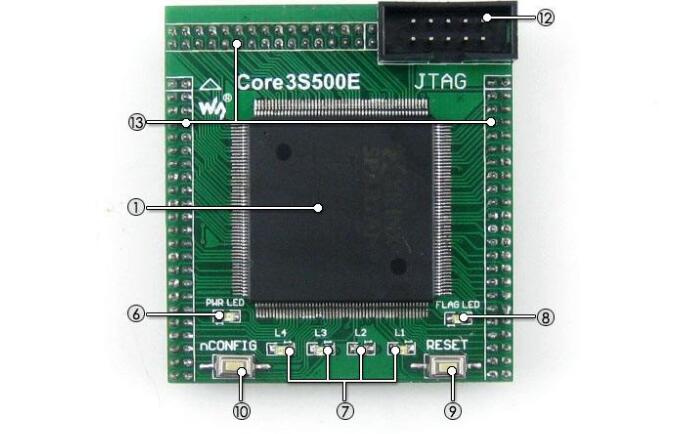

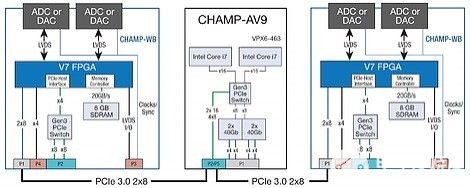

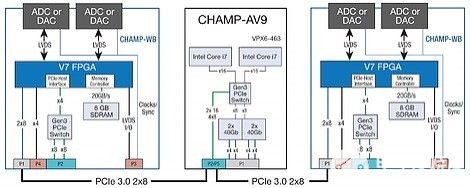

408 ADC和DAC是FPGA與外部信號的接口,從數(shù)據(jù)接口類型的角度劃分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 1624

1624

SoC FPGA正日益加速入侵嵌入式系統(tǒng)市占。值此迅猛擴張之勢,高性能計算、通信網(wǎng)絡、汽車電子、工業(yè)等應用領域的技術(shù)與功能迅速升級,如為加強汽車安全性,車載通信系統(tǒng)整合視覺系統(tǒng)的整合方案將會大行其道

2013-04-15 08:53:09 3600

3600 、移動設備和汽車等日常生活設備中的迅速普及,但是機器視覺的最大進步莫過于處理能力。隨著處理器的性能以每兩年翻一番的速度不斷提升,以及多核CPU和FPGA等并行處理技術(shù)日益受到關(guān)注,視覺系統(tǒng)設計人員現(xiàn)在可以

2018-08-03 11:13:19

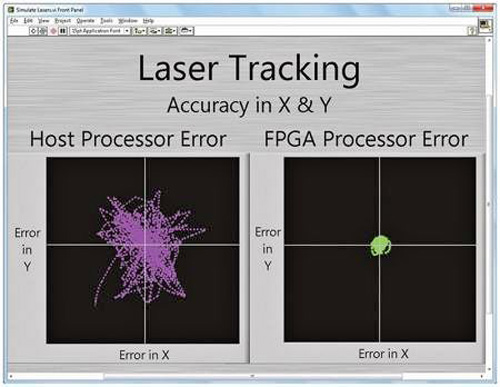

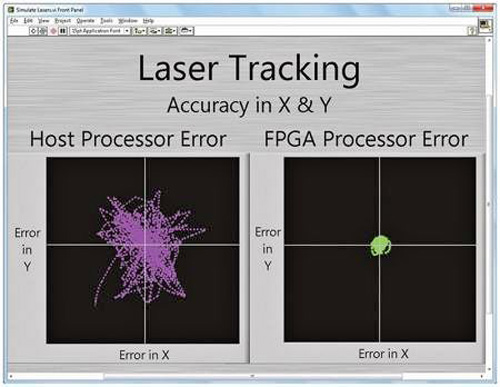

本篇討論的是有關(guān)CPU(在Zynq SoC中是指ARM處理器核)和FPGA的可編程邏輯架構(gòu)之間的機器視覺算法分割。美國國家儀器公司(National Instruments)的Carlton

2021-05-31 09:17:44

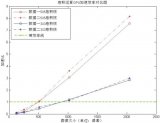

CPU和GPU都屬于馮·諾依曼結(jié)構(gòu),指令譯碼執(zhí)行,共享內(nèi)存。FPGA之所以比CPU、GPU更快,本質(zhì)上是因為其無指令,無共享內(nèi)存的體系結(jié)構(gòu)所決定的。馮氏結(jié)構(gòu)中,由于執(zhí)行單元可能執(zhí)行任意指令,就需要

2018-08-16 09:54:23

個“選通”信號加上一個“等待”信號。其中的“選通”信號來源于PC,而“等待”信號則是傳輸進PC的。其原理是這樣的:每次傳輸中,PC都會插入一種選通,然后FPGA以等待信號響應。我們選一個選通信號(一次

2019-08-06 05:00:00

的特性,在熵編解碼算法的處理上優(yōu)于GPU。三.FPGA加速性能的主要因素:并行度FPGA算法一般運行頻率在幾百MHz的級別,CPU的頻率已達到GHz。我們一定會想FPGA的算法為什么比通用CPU的算法

2018-08-01 09:55:53

中使用FPGA器件的開發(fā)團隊,提供一種快速方便地在當前設計的處理性能、材料清單(BOM)成本和效率之間尋找和實現(xiàn)最有效平衡的方法嗎?理解并行工程如何影響一個團隊的設計工作,以及它如何影響開發(fā)團隊從項目

2018-10-08 15:17:52

FPGA的并行多通道激勵信號產(chǎn)生模塊FPGA的并行多通道激勵信號產(chǎn)生模塊.docx

2012-08-11 10:35:50

相關(guān)和目標設備的定位也相關(guān)。因為FPGA作為簡單業(yè)務流大數(shù)據(jù)量的處理形態(tài)仍然是CPU無可比擬的優(yōu)勢,FPGA內(nèi)部可以開發(fā)大量業(yè)務數(shù)據(jù)并行,從而實現(xiàn)高速的數(shù)據(jù)處理。 在實現(xiàn)高速處理方面,CPU的另一個

2018-08-06 11:45:27

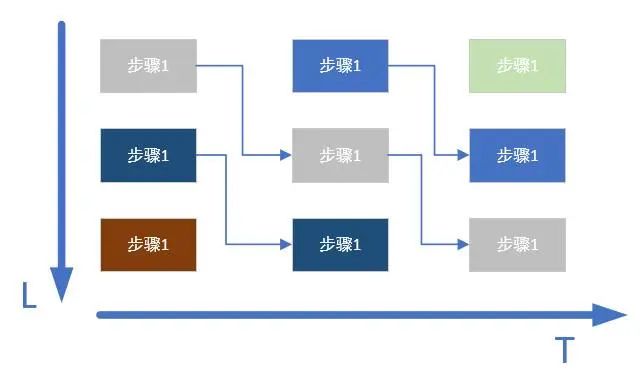

`fpga基礎篇(二):三大并行結(jié)構(gòu)最近小編比較忙,所以這期給大家介紹一個基礎篇,比較簡單,但卻是FPGA編程的基礎。我們知道FPGA與單片機最大的區(qū)別就是FPGA是并行執(zhí)行的,而單片機是串行的,說

2017-04-13 10:23:27

并行控制編程將根據(jù)任務而不是輸入進行工作劃分。如果將100通道的并行數(shù)據(jù)算法比作汽車工廠內(nèi)100個工人各自在組裝一輛汽車,那么并行控制程序就可以比作有100個工作崗位的組裝線,每個崗位完成

2019-08-01 06:36:16

基本概念在MIPI目前公布的協(xié)議中,有3類基于攝像頭的接口,一個是前幾年大行其道的D-PHY接口,一個是C-PHY接口,還有一個是M-PHY接口。D-PHY接口一般是1/2/4 Lane,每個

2021-07-29 07:21:11

`產(chǎn)品特點基于ZYNQ+并行DSP處理架構(gòu)處理架構(gòu)十分靈活,能夠滿足各類并行加速需求支持OpenCL編程,方便算法移植系統(tǒng)處理靈活:FPGA或DSP可選尺寸小巧,方便集成擴展能力強 應用領域并行控制

2017-06-08 10:33:07

DSP的并行互連方法有哪些,其各自的優(yōu)缺點是什么?如何利用TMS320C6x的HPI組成多DSP互聯(lián)并行系統(tǒng)?如何利用ADSP2106x的Link口組成多DSP互連并行系統(tǒng)?

2021-04-08 06:41:13

是遍歷性的算法,其運算量大,在實時處理中受到限制。利用2片TI公司的高速DSP芯片TMS320C6201,應用其HPI接口并行實現(xiàn)多種滑窗算法, 滿足了某雷達系統(tǒng)解模糊的實時需要。系統(tǒng)由2片

2019-04-08 09:36:19

報文的可讀性和調(diào)試性上有很大的優(yōu)勢。現(xiàn)在互聯(lián)網(wǎng)大行其道,HTTP可以說是無處不在(HTTPS就是HTTP的TLS/SSL的加密傳輸形式,這種方式在認證上比較復雜)。下圖展示了其處于網(wǎng)絡的應用層:...

2022-02-10 07:46:30

。CPU很好(我想)但其余的硬件都是TRYINg來跟上..有任何想法嗎?可以使用當前窗口完成并行處理。完全升級會發(fā)生多少變化?以上來自于谷歌翻譯以下為原文Im an old time computer

2018-10-18 14:06:51

的定位也相關(guān)。因為FPGA作為簡單業(yè)務流大數(shù)據(jù)量的處理形態(tài)仍然是CPU無可比擬的優(yōu)勢,FPGA內(nèi)部可以開發(fā)大量業(yè)務數(shù)據(jù)并行,從而實現(xiàn)高速的數(shù)據(jù)處理。在實現(xiàn)高速處理方面,CPU的另一個發(fā)展趨勢是多核

2017-06-07 13:12:54

在數(shù)字系統(tǒng)的設計中,FPGA+ARM 的系統(tǒng)架構(gòu)得到了越來越廣泛的應用,FPGA 主要實現(xiàn)高速數(shù)據(jù)的處理;ARM 主要實現(xiàn)系統(tǒng)的流程控制.人機交互.外部通信以及FPGA 控制等功能.I2C.SPI

2019-09-17 06:21:10

數(shù)字和網(wǎng)絡越來越多的滲透到我們生活的時候,無處不在的嵌入式設備正在你的周圍,雖然大多數(shù)時間沒有意識到,但這些嵌入式設備確實在并不斷滲入到我們的日常生活。最顯而易見的方面包括正在如火如荼開展的數(shù)字電視革命,信息和數(shù)據(jù)在數(shù)字電視網(wǎng)絡上大行其道。

2019-09-27 06:20:31

本文提出了一種基于FPGA的適合大規(guī)模數(shù)字信號處理的并行處理結(jié)構(gòu)。

2021-04-30 07:16:52

最近有一個項目,用FPGA作一個協(xié)處理器,這涉及到FPGA與CPU共享內(nèi)存的問題。平臺打算用DM6467或者DM81xx。

一直沒找到頭緒,不知道TI的專家們有什么好的建議?

2018-06-21 04:29:36

眾所周知,開博爾一直在高端HDMI線材研發(fā)領域穩(wěn)步前進且突破不斷。除了最為暢銷而經(jīng)典的ATL銅芯HDMI線以外,去年還連續(xù)上線兩款光纖HDMI線,更取得了不俗的成績。如今,開博爾將目光投向?qū)楦叨孙@示器游戲玩家所推崇的DP電競線材,一連推出了兩款電競DP線,分別是銅芯DP線1.2版和光纖DP線1.4版。今天我們主要來看一下開博爾這款支持8K60hz的光纖DP線。 光纖特性想必很多人都有所了解,光信號傳輸無輻射無屏蔽層,可以有效避免電磁干擾,在長距離傳輸上面比銅芯有一定優(yōu)勢。開博爾DP線采用造價更加昂貴的光纖線芯,且支持1.4版本,所以可以傳輸8K60hz,4k 144hz,2k165hz,最高帶寬能達到32Gbps,這樣的傳輸速率和帶寬配合光速傳輸?shù)墓饫w線芯,從理論上來說,已經(jīng)是最高標準了。我們可以看下開博爾光纖DP線的內(nèi)部結(jié)構(gòu),PVC外被加上高柔韌彈性外保護套還有各種加固和絕緣線芯,以及鍍金端子和鋅合金高檔烤漆外殼,開博爾光纖DP線真材實料一覽無遺。 DP線還有一點很重要,就是鎖扣部分。這個鎖扣一定要保證可以輕松按得動,否則特別容易傷害顯卡。開博爾光纖DP線按鈕有進行特殊設計,符合人體工程學,不用費力就能插進去,而且經(jīng)過廠商千百次測試,暫未發(fā)現(xiàn)異常情況。還需要注意的情況是,光纖線的光電轉(zhuǎn)換引擎的承接功能不同,因此,光纖DP接口具有方向性,其中source端會出現(xiàn)接信號源,display接顯示端。注意不要插反。 據(jù)悉,開博爾光纖DP線將于1月10日正式上市,目前可以參與預定10元抵100元活動,有興趣的朋友可以去了解一下。

2018-12-28 16:55:50

圖像處理FPGA 設計基本方法:1.陣列結(jié)構(gòu)結(jié)合流水線處理設計例如RGB圖像,包括三組數(shù)據(jù),處理時需要并行三通道后,每個通道進行分別的串行流水處理。2.緩存設計幀緩存 行緩存 列對齊3.資源分辨率 處理窗口 對資源影響成倍增加

2019-01-04 13:59:26

)、離散余弦變換(DCT)、小波變換、數(shù)字濾波器(有限脈沖響應(FIR)、無限脈沖響應(IIR)和自適應濾波器)以及數(shù)字上下變頻器。這些算法中,每一種都有一些結(jié)構(gòu)性的元件可以用并行方法實現(xiàn)。而FPGA

2021-12-15 06:30:00

將如何波動。采用并行工程(CE)技術(shù),可以為在項目中使用FPGA器件的開發(fā)團隊,提供一種快速方便地在當前設計的處理性能、材料清單(BOM)成本和效率之間尋找和實現(xiàn)最有效平衡的方法嗎?理解并行工程

2020-10-21 13:57:03

DSP芯片組成并行處理系統(tǒng)。另外,為充分發(fā)揮 DSP芯片在復雜算法處理上的優(yōu)勢及FPGA在大數(shù)據(jù)量的底層算法上的優(yōu)勢,設計了一種基于FPGA控制的多DSP并行處理系統(tǒng)。1 系統(tǒng)設計基于FPGA控制的多

2019-05-21 05:00:19

核心的微處理器,其性能直接影響整個系統(tǒng)的性能。為了提高CPU的效率和指令執(zhí)行的并行性,現(xiàn)代微處理器廣泛采用流水線設計,所以,CPU流水線的設計成為決定其性能的關(guān)鍵。

2019-10-12 09:31:50

傳統(tǒng)數(shù)字濾波器硬件的實現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號處理器(DSP)來實現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種結(jié)構(gòu)特別適用于并行處理結(jié)構(gòu),相對于傳統(tǒng)方法來說,其并行度和擴展性都很好,它逐漸成為構(gòu)造可編程高性能算法結(jié)構(gòu)的新選擇。

2019-10-22 07:14:04

我正在設計一個子板,上面有40個Artix 7(AC7A12T)設備。每臺設備都應具有相同的圖像。我不是一次編程鏈1中的每個器件的串行鏈,而是希望并行執(zhí)行任務,以便所有FPGA同時進行編程。我似乎

2020-05-14 07:01:03

CD4017以其優(yōu)越的性能“大行其道”,各種應用數(shù)不勝數(shù),本人因喜歡漂亮的彩燈,故想對CD4017的性能作一個應用的分析。

2021-05-06 07:57:35

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-10-23 07:04:22

本文提出了一個基于FPGA 的信息處理的實例:一個簡單的人工神經(jīng)網(wǎng)絡應用Verilog 語言描述,該數(shù)據(jù)流采用模塊化的程序設計,并考慮了模塊間數(shù)據(jù)傳輸信號同 步的問題,有效地解決了人工神經(jīng)網(wǎng)絡并行數(shù)據(jù)處理的問題。

2021-05-06 07:22:07

高檔MCU的不斷出現(xiàn),以MCU為核心的嵌入式語音交互系統(tǒng)會有非常好的應用前景。1 概述在現(xiàn)代社會,“懶人科技”大行其道。當面臨眾多繁瑣的按鍵操作和菜單選擇的時候,簡單地說出指令,是最具有人情味的人機操作...

2021-07-21 09:31:27

使用的java的屬于一個周期長和研發(fā)成本較高的工作,但是隨著技術(shù)的發(fā)展,某些前端語言技術(shù)在大行其道,所以使用JS進行一些簡單的對CPU負載要求低的工作可以使用,這樣前端的人員就會擴展到服務...

2021-11-05 06:05:51

等功能。FPGA進行的這種算子法處理是并行流水線算法,其延時是固定的,比如用3x3的算子進行處理其給出結(jié)果的延時是兩行圖像的時間。還有這個算子法和現(xiàn)在卷積神經(jīng)網(wǎng)絡中最前面的卷積層運算是類似

2023-06-08 15:55:34

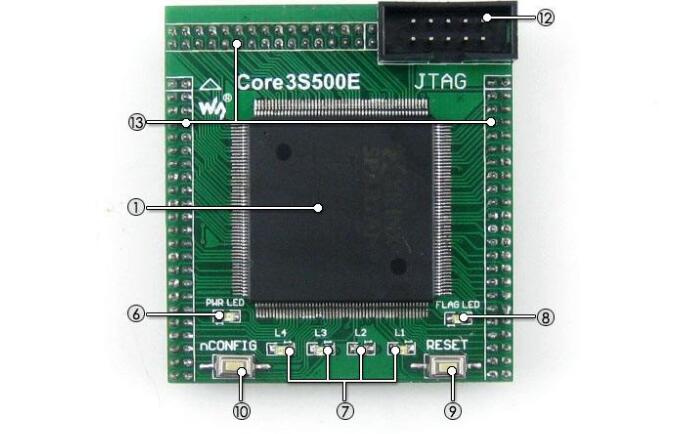

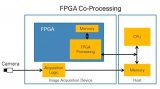

zynq如何實現(xiàn)cpu跟fpga協(xié)同處理?

2023-10-16 07:00:08

現(xiàn)在,各種開發(fā)板大行其道,樹莓派(Raspberry Pi)、Arduino,Beagleboard等等開源硬件讓眾多電子愛好者們深陷其中。然而,實際工作中或者DIY中,我們可能并沒有那么方便地去

2016-08-17 17:21:11

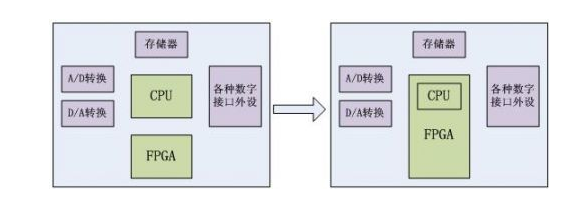

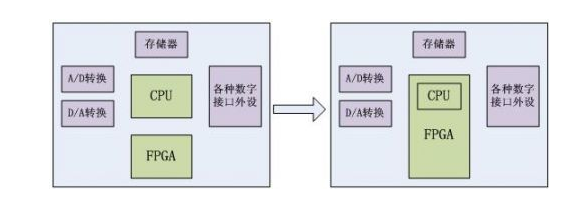

。 CPU+FPGA的并行處理將大行其道 目前,嵌入式系統(tǒng)設計中存在下述一些問題:IP復用;總體成本和占板面積;工藝;一味提高處理器時鐘速率,會使功耗大幅增加及散熱惡化,并增加設計人員解決這些

2011-07-21 10:52:00

針對基于SRAM 結(jié)構(gòu)的FPGA,詳細介紹了一種采用可在線升級的SST89V564RD微處理器對其進行上電PPA(被動并行異步)配置,不僅實現(xiàn)了FPGA 的在線配置,而且通過微處理器的IAP 技術(shù)

2009-09-15 16:27:50 23

23 Blackfin? 處理器系列已經(jīng)得到了進一步的擴充(增加了兩款新器件),以滿足大行其道的嵌入式網(wǎng)絡連接性不斷提升的需求。當與高性能的16/32位Blackfin嵌入式處理器內(nèi)核、靈活的高速

2023-07-07 13:26:13

Blackfin?處理器系列已經(jīng)得到了進一步的擴充(增加了兩款新器件),以滿足大行其道的嵌入式網(wǎng)絡連接性不斷提升的需求。當與高性能 16/32位Blackfin嵌入式處理器內(nèi)核、靈活

2023-07-07 13:28:39

描述 Blackfin?處理器系列已經(jīng)得到了進一步的擴充(增加了兩款新器件),以滿足大行其道的嵌入式網(wǎng)絡連接性不斷提升的需求。當與高性能16/32位Blackfin嵌入式處理器內(nèi)核、靈活

2023-12-28 15:34:05

描述 Blackfin?處理器系列已經(jīng)得到了進一步的擴充(增加了兩款新器件),以滿足大行其道的嵌入式網(wǎng)絡連接性不斷提升的需求。當與高性能16/32位Blackfin嵌入式處理器內(nèi)核、靈活

2023-12-28 15:44:28

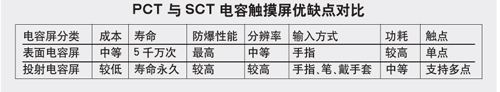

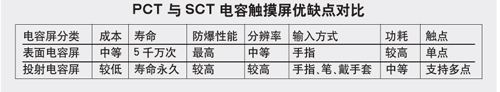

技術(shù)成熟成本下降 電容式觸控將大行其道

隨著iPhone觸控手機的廣受歡迎,電容式觸控這一專業(yè)的術(shù)語逐漸被人們所熟知。它帶來的嶄新使用體驗,都源于其技術(shù)與傳

2009-11-19 10:38:56 373

373

鍵鼠模式松動 多點觸控功能大行其道

2010-03-10 09:07:58 601

601 醫(yī)療產(chǎn)業(yè)模式從治療轉(zhuǎn)向保健,便攜醫(yī)療設備將大行其道

得益于中國政府新醫(yī)改的推動和人民大眾對健康保健的重視,以及家用與醫(yī)用市場的不同特性成就了中國便攜/

2010-01-04 10:58:08 753

753 借助FPGA協(xié)處理提升性能 設計人員能夠利用由FPGA架構(gòu)的并行性所帶來的使用靈活的特點,大幅提升DSP系統(tǒng)的性能。通常的設計示例包括(并不局限于)FIR濾波、FFT、數(shù)字下變頻和前向糾錯(FEC)模塊等。 Xilinx Virtex TM-4和Virtex-5架構(gòu)提供了多達512個并行乘

2011-02-28 12:50:41 46

46 本文介紹的基于PCI總線的FPGA計算平臺的系統(tǒng)實現(xiàn):通過在PC機上插入擴展PCI卡,對算法進行針對并行運算的設計,提升普通PC機對大計算量數(shù)字信號的處理速度。本設計采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

對FPGA技術(shù)來說,早期研發(fā)在5年前就已開始嘗試采用多核和硬件協(xié)處理加速技術(shù)朝系統(tǒng)并行化方向發(fā)展。在實際設計中,FPGA已經(jīng)成為CPU的硬件協(xié)加速器,很多芯片廠商采用了硬核或軟核CPU+FPGA的

2011-09-23 15:30:06 770

770 據(jù)結(jié)合的智能終端中都在采用這種方式,FPGA+CPU將會是未來基于大數(shù)據(jù)的終端的主要架構(gòu),改變整個處理器產(chǎn)業(yè)格局。

2016-07-28 14:28:00 3357

3357 基于FPGA的嵌入式多核處理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 隨著物聯(lián)網(wǎng)(IoT)的發(fā)展,諸如霧計算的去集中化分布式智能概念正大行其道,以滿足對更低延時、更高安全性、更低功耗和更高可靠性的要求。

2016-11-05 07:27:58 809

809

基于FPGA的ARM并行總線研究與仿真

2017-01-24 16:54:24 19

19 Jan Gray是在FPGA中集成32位RISC處理器的專家,他寫了一篇博客叫作FPGA CPU 新聞,副標題為 “使用FPGA開發(fā)并行計算機體系架構(gòu)”。

2017-02-10 08:55:03 1898

1898

并行處理在計算全息中的應用_簡獻忠

2017-03-19 11:28:02 0

0 本文介紹了FPGA電源設計并行工程的合理性,講解了并行工程(CE)技術(shù)及其作用,討論了FPGA電源系統(tǒng)設計的復雜性和不確定性。

2017-10-13 13:00:35 5

5 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 要求,因此,需采用專用的數(shù)字信號處理器(DSP)來進行高速運算。盡管當前的數(shù)字信號處理器已達到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達的性能要求,需要引入并行處理技術(shù),在本設計中使用4片DSP芯片組成并行處理

2017-10-31 09:58:04 0

0 并行輸入就是兩個或兩個以上的信號同時輸入。比如P0~P3口,都可以同時接受8路輸入信號,所以是并行輸入。快速輪流調(diào)用CPU使用權(quán),反正小于10MS的東西,你又看不見,人眼是不能識別刷新頻率小于

2017-11-16 10:56:12 12449

12449

多核處理器、FPGA和PCI Express正在改變現(xiàn)代PC機的版圖,并幫助LabVIEW圖形化編程根據(jù)工程師應用邏輯的數(shù)據(jù)流向,實現(xiàn)真正的并行化處理和并行化測量。利用NI TestStand軟件

2017-11-16 20:31:57 8828

8828

針對信號處理數(shù)據(jù)量大、實時性要求高的特點,從實際應用出發(fā),設計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2373

2373

Vviado-HLS基于Xilinx FPGA對C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構(gòu) 與處理器架構(gòu)相比,FPGA結(jié)構(gòu)具有更高的并行。Vivado-HLS對軟件C程序編譯時與處理器編譯是不一樣的執(zhí)行機制。

2017-11-18 12:23:09 2377

2377

)的并行處理特性,而且提供了完全支持向量操作指令和符合IEEE32位浮點格式的頂點處理能力和像素處理能力,已經(jīng)成為了一個強大的并行計算單元。研究人員將其應用于加速科學計算和可視化應用程序,取得了令人鼓舞的研究成果。 與CPU相比,GPU具有以下優(yōu)勢:強大的并行處理能力和高效率的數(shù)據(jù)傳輸能

2017-12-01 12:23:05 462

462

CPU+FPGA的并行處理是目前的發(fā)展趨勢這種處理方式將大行其道。

2018-01-02 15:54:07 15989

15989 因此在考慮誰更適合進行圖像處理時,CPU還是FPGA?答案是“視情況而定”。您需要了解應用的目標,才能使用最適合該設計的處理元件。但是,不管是什么應用,基于CPU或FPGA的架構(gòu)及其固有的優(yōu)勢都可以將機器視覺應用的性能提升一個等級。

2018-01-16 11:49:00 7173

7173

處理能力。隨著處理器的性能以每兩年翻一番的速度不斷提升,以及多核CPU和FPGA等并行處理技術(shù)日益受到關(guān)注,視覺系統(tǒng)設計人員現(xiàn)在可以應用復雜的算法來可視化數(shù)據(jù),并創(chuàng)建出更加智能的系統(tǒng)。 性能的提高意味著設計人員可以獲

2018-01-25 22:34:12 465

465

FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動 基于FPGA灰度圖像高斯濾波算法的實現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:49:00 1479

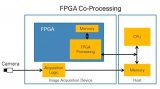

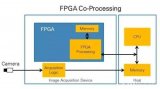

1479 如下圖,FPGA作為協(xié)處理器,CPU把指令寫入內(nèi)存,FPGA從內(nèi)存讀取指令執(zhí)行,并把計算結(jié)果寫入內(nèi)存。這種模式的優(yōu)點是簡單易行,協(xié)處理器和CPU分離。瓶頸在于共享內(nèi)存,限制了性能,同時由于通過內(nèi)存

2018-06-20 15:17:10 12724

12724 近年來高分辨率視訊大行其道,從DVD開始,到目前的HD DVD以及BD,在搭配適當?shù)挠跋窬幋a以及加大串流流量以后,肉眼可見雜訊或方塊現(xiàn)象已經(jīng)微乎其微,過去在傳統(tǒng)電視大行其道的視訊濾波處理似乎已經(jīng)失去了舞臺?

2019-07-15 08:00:00 1653

1653

4分鐘的FPGA簡單入門介紹,主要介紹了邏輯塊、相對于處理器的并行操作。搬運于YouTube,字幕自制。

2019-08-29 06:05:00 2341

2341 “使用FPGA的好處在于,它基本上是由軟件定義的硬件。因此,系統(tǒng)設計人員可以在軟件芯片中編程,并且當該軟件下載到FPGA,代碼變成可根據(jù)需要重新編程的實際硬件。由于FPGA實際是并行設備,使用FPGA進行圖像處理特別有利。

2019-07-23 10:04:42 2418

2418

在數(shù)字系統(tǒng)的設計中,FPGA+ARM 的系統(tǒng)架構(gòu)得到了越來越廣泛的應用,FPGA主要實現(xiàn)高速數(shù)據(jù)的處理;ARM 主要實現(xiàn)系統(tǒng)的流程控制.人機交互.外部通信以及FPGA 控制等功能.I2C.SPI

2019-08-08 15:37:50 5863

5863

基于FPGA的CPU集成將帶來的一些潛在優(yōu)勢包括:更易于滿足大多數(shù)系統(tǒng)的功能性需求;潛在的改善了系統(tǒng)的性能;在某些應用中的靈活性和可升級性大大提高。

2019-09-16 17:44:06 1137

1137

在異構(gòu)計算大行其道的當下,如果計算設備“不說同一種語言”的話,計算的效果無法達到最佳,“巴別塔”的效果仍然存在。

2019-10-09 15:49:07 694

694 的必要性、當前實際的圖片解決方案與部署方式以及如何通過 FPGA+CPU 異構(gòu)計算的方案維護用戶體驗與服務成本新平衡。 1. ?為什么需要圖片加速? 目前,圖片處理的需求正在快速成長,即源于用戶生成內(nèi)容,視頻圖片抓取等方式的圖片縮略圖生

2020-10-30 12:52:32 188

188 出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設計并建立了FPGA驗證平臺.為了對多核處理器平臺性能進行評測,提出了基于OpenMP的3種可行的圖像處理領域的經(jīng)典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 及布局布線,并用ModelSim和Matlab對設計作了聯(lián)合仿真。結(jié)果表明,通過利用FPGA器件中大量的乘法器、邏輯單元及存儲器等硬件資源,采用全并行加流水結(jié)構(gòu),可在一個時鐘節(jié)拍內(nèi)完成32點FFT運算的功能,設計最高運算速度可達11 ns,可實現(xiàn)對高速A/D采樣數(shù)據(jù)的實時處理.

2021-03-31 15:22:00 11

11 主頻只是影響計算速度的一個因素,并不是全部。在執(zhí)行一些計算密集型的任務場景中,FPGA的計算速度是更快的,目前FPGA作為CPU的協(xié)處理器已經(jīng)廣泛應用在Intel、AMD等公司的產(chǎn)品中。 CPU

2021-06-30 10:57:54 2037

2037 ADC和DAC是FPGA與外部信號的接口,從數(shù)據(jù)接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經(jīng)常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅(qū)動并行ADC和并行DAC芯片。

2022-04-21 08:55:22 5774

5774 OpenVPX 將高速并行處理 FPGA 與 CPU 的軟件功能結(jié)合在一起,以滿足無人平臺最具挑戰(zhàn)性的傳感器處理應用。

2022-10-28 10:10:01 1668

1668

1.8V2.5V3.3V信號大行其道,如何設計選型ESD,看這篇就夠了目前像自動駕駛、遠程醫(yī)療、智慧城市等領域所涉及的電子設備的主要芯片(如DSP、CUP、MCU、ARM、DDR...)都會有多路

2022-05-06 17:26:08 761

761

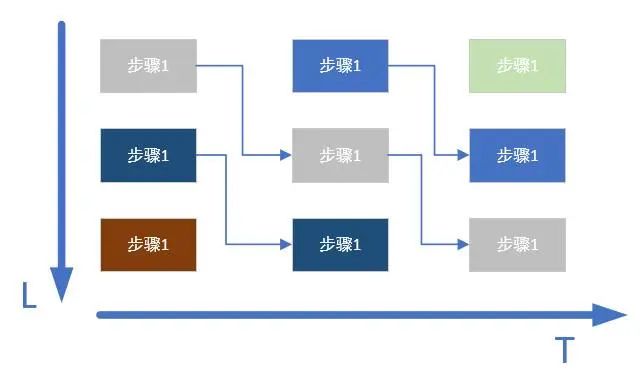

將圖像處理的算法轉(zhuǎn)換為FPGA系統(tǒng)設計的過程稱為算法映射,CPU并行算法的實現(xiàn)與FPGA并行算法的實現(xiàn)是有一定區(qū)別的。1.算法系統(tǒng)結(jié)構(gòu) 圖像處理算法主要有兩種設計結(jié)構(gòu):流水線結(jié)構(gòu)和并行陣列結(jié)構(gòu)

2023-09-11 10:45:02 266

266

電子發(fā)燒友網(wǎng)站提供《無與倫比的并行處理—FPGA加速的根本基石.pdf》資料免費下載

2023-09-15 14:57:19 0

0 電子發(fā)燒友網(wǎng)站提供《基于FPGA的ARM并行總線設計原理.pdf》資料免費下載

2023-10-10 09:31:31 0

0 CPU core:分為2種,軟core和硬core.軟core是用邏輯代碼寫的CPU模塊,可以在任何資源足夠的FPGA中實現(xiàn),使用非常靈活。而且在大容量的FPGA中還可以集成多個軟core,實現(xiàn)多核并行處理。

2024-03-14 11:36:34 79

79

電子發(fā)燒友App

電子發(fā)燒友App

評論