基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)綜述

-FPGA驗(yàn)證技術(shù)-

作者簡(jiǎn)介:

尤靜,女,西安電子科技大學(xué),計(jì)算機(jī)科學(xué)與技術(shù)專業(yè),碩士,工程師。從事FPGA方向開發(fā)及驗(yàn)證工作十余年,曾負(fù)責(zé)探月工程、導(dǎo)航、高分等多個(gè)國(guó)家重點(diǎn)工程航天器軟件的第三方FPGA軟件評(píng)測(cè)。

摘要:在調(diào)研近幾年基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)相關(guān)工具及工程應(yīng)用情況的基礎(chǔ)上,從HDL代碼自動(dòng)生成的技術(shù)角度分析了基于模型設(shè)計(jì)的應(yīng)用需求及現(xiàn)狀,分析了基于模型的設(shè)計(jì)自動(dòng)生成HDL代碼和傳統(tǒng)手動(dòng)編寫HDL代碼的效率、優(yōu)勢(shì),介紹了幾種HDL代碼自動(dòng)生成方法和工具,總結(jié)了基于Matlab/Simulink的HDL代碼自動(dòng)生成的工程應(yīng)用情況,為航天型號(hào)系統(tǒng)開發(fā)設(shè)計(jì)、驗(yàn)證人員開展相關(guān)工作提供參考。

關(guān)鍵詞:基于模型的設(shè)計(jì);現(xiàn)場(chǎng)可編程門陣列;HDL代碼自動(dòng)生成

引 言

面對(duì)我國(guó)航天型號(hào)任務(wù)發(fā)展與需求的快速變化,空間站、深空探測(cè)、北斗導(dǎo)航等軟件密集型系統(tǒng)迅速擴(kuò)大,智能化、網(wǎng)絡(luò)化需求越來越多。由于系統(tǒng)復(fù)雜度提高,設(shè)計(jì)難度變大、周期變長(zhǎng)、文檔復(fù)雜度提高,代碼規(guī)模的快速膨脹給設(shè)計(jì)和驗(yàn)證都帶來了巨大的挑戰(zhàn)。通常意義的軟件又可以分為應(yīng)用軟件、嵌入式軟件和可編程邏輯代碼,現(xiàn)場(chǎng)可編程門陣列(FPGA)即是可編程邏輯代碼的載體,F(xiàn)PGA因其設(shè)計(jì)周期短、并行處理能力強(qiáng)、穩(wěn)定性好等優(yōu)勢(shì),在系統(tǒng)中承擔(dān)了越來越多的控制、算法、處理任務(wù),相應(yīng)的硬件描述語言HDL代碼量也成倍甚至指數(shù)級(jí)增長(zhǎng)。使用編程語言直接建模存在代碼冗長(zhǎng)和在不同設(shè)計(jì)階段重新利用模型時(shí)很難更改的問題,在團(tuán)隊(duì)間用于交流的需求、技術(shù)規(guī)范、測(cè)試等其他文檔也可能引起歧義和誤解。

基于高層次抽象的建模和可綜合的邏輯代碼自動(dòng)生成技術(shù)成為被重點(diǎn)關(guān)注和研究的領(lǐng)域。基于模型的設(shè)計(jì)方法從設(shè)計(jì)階段進(jìn)行系統(tǒng)建模,自頂而下展開設(shè)計(jì),開發(fā)過程中迭代驗(yàn)證并通過工具實(shí)現(xiàn)代碼自動(dòng)生成,國(guó)外相關(guān)領(lǐng)域在上個(gè)世紀(jì)八十年代開始相關(guān)研究,相應(yīng)的陸續(xù)有成熟的應(yīng)用案例產(chǎn)生,涉及到航天、汽車、通信、醫(yī)療、大數(shù)據(jù)等各個(gè)領(lǐng)域,國(guó)內(nèi)在近十年也開始開展基于模型的設(shè)計(jì)方法的理論研究和工程實(shí)踐,但目前較多的成熟應(yīng)用都是基于模型設(shè)計(jì)后自動(dòng)生成C代碼等嵌入式軟件方面,由于現(xiàn)場(chǎng)可編程門陣列的特殊性,導(dǎo)致對(duì)自動(dòng)代碼生成有可綜合性的要求,因此在自動(dòng)生成HDL代碼方面的應(yīng)用還很有限。本文分析了國(guó)內(nèi)外近幾年基于模型的設(shè)計(jì)及HDL代碼自動(dòng)生成技術(shù)使用到的工具及工程應(yīng)用情況,在調(diào)研了大量的理論、應(yīng)用案例的基礎(chǔ)上,總結(jié)了基于模型的設(shè)計(jì)自動(dòng)生成的HDL代碼和傳統(tǒng)手動(dòng)編寫HDL代碼的效率、優(yōu)勢(shì),比較了較成熟的工具和方法,闡述了HDL代碼自動(dòng)生成的應(yīng)用需求和現(xiàn)狀,為航天型號(hào)系統(tǒng)開發(fā)設(shè)計(jì)人員開展相關(guān)工作提供參考。

01

基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)應(yīng)用需求

近年來,現(xiàn)場(chǎng)可編程門陣列(FPGA)被廣泛應(yīng)用于航空航天、汽車、通信、工業(yè)自動(dòng)化、電機(jī)控制、醫(yī)學(xué)成像等嵌入式應(yīng)用領(lǐng)域。傳統(tǒng)的FPGA上的數(shù)字設(shè)計(jì)實(shí)現(xiàn)依賴于硬件描述語言(VHDL和Verilog),并使用相應(yīng)的工具生成FPGA目標(biāo)代碼。這種方法仍然是當(dāng)今各行業(yè)應(yīng)用中使用最廣泛的方法。然而隨著半導(dǎo)體技術(shù)的進(jìn)步和系統(tǒng)復(fù)雜性的不斷增加,代碼規(guī)模指數(shù)級(jí)增長(zhǎng),給開發(fā)和驗(yàn)證工作都帶來了巨大的挑戰(zhàn),基于模型的系統(tǒng)級(jí)設(shè)計(jì)方法成為更理想的選擇。

傳統(tǒng)的FPGA軟件開發(fā)方法為算法工程師編寫算法文檔,程序員根據(jù)算法文檔手寫代碼,代碼完成之后下載到硬件中驗(yàn)證算法、軟件是否正確,根據(jù)相關(guān)文獻(xiàn)報(bào)道,有60%的錯(cuò)誤是在編制技術(shù)規(guī)范階段引入的,而這時(shí)能夠發(fā)現(xiàn)的錯(cuò)誤僅有8%,大部分的錯(cuò)誤需要到測(cè)試階段才能發(fā)現(xiàn)。系統(tǒng)設(shè)計(jì)過程中分為若干個(gè)階段,每個(gè)階段都會(huì)有對(duì)應(yīng)的工程師,每個(gè)工程師在開發(fā)過程中會(huì)針對(duì)性地解決某幾個(gè)關(guān)鍵的技術(shù)問題,當(dāng)前系統(tǒng)的開發(fā)主要有以下幾個(gè)方面的問題主要存在以下幾方面問題:

1) 開發(fā)的盲目性:對(duì)系統(tǒng)實(shí)現(xiàn)細(xì)節(jié)缺乏把握的情況下已經(jīng)完成的硬件電路的設(shè)計(jì),此階段無法明確先前的設(shè)計(jì)能否滿足實(shí)際應(yīng)用需求,而此時(shí)已經(jīng)投入了較大的硬件成本。

2) 不同開發(fā)環(huán)節(jié)對(duì)文檔的描述和理解的偏差問題:在設(shè)計(jì)開發(fā)過程中會(huì)涉及到大量用文字描述的文檔。文字本身就是人對(duì)于一種事物,一個(gè)概念的抽象,難免不同工程師對(duì)于文字的理解出現(xiàn)差錯(cuò),造成工程師之間產(chǎn)生分歧,從而導(dǎo)致整個(gè)系統(tǒng)的功能與實(shí)際目標(biāo)功能出現(xiàn)偏差。

3) 手工編程會(huì)產(chǎn)生代碼不可靠的問題:在設(shè)計(jì)后期集中測(cè)試過程中一旦測(cè)出問題,就很難排查是方案不理想還是軟件代碼編寫的錯(cuò)誤。手工編程費(fèi)時(shí)費(fèi)力,調(diào)試周期較長(zhǎng),開發(fā)風(fēng)險(xiǎn)很高;即使軟件編程不存在問題,如果想要在后期修改方案,則又要開始新的一輪改進(jìn)工作將耗費(fèi)時(shí)間在軟件的手工修改和調(diào)試上。

4) 設(shè)計(jì)缺陷發(fā)現(xiàn)過晚而產(chǎn)生重大損失的問題:設(shè)計(jì)過程中的缺陷發(fā)現(xiàn)得越早,則修正的難度越低,花費(fèi)的成本越少。比如汽車的設(shè)計(jì)缺陷有可能給公司帶來幾億甚至與上百億美元的損失,而在汽車投放市場(chǎng)之前即可修正各種缺陷,那么可以將損失降低到最小。

5) 真實(shí)樣件測(cè)試的高成本和低效率:成功開發(fā)一個(gè)產(chǎn)品必然要經(jīng)過大量的測(cè)試和實(shí)驗(yàn),需要大量的實(shí)驗(yàn)臺(tái)架,而這些工作必然會(huì)花費(fèi)大量的人力和金錢。產(chǎn)品中存在錯(cuò)誤和缺陷往往是測(cè)試的不充分,因?yàn)橛行┣闆r在系統(tǒng)的實(shí)際工作中沒有出現(xiàn),出現(xiàn)了就是災(zāi)難性的,要在實(shí)驗(yàn)室條件下完成這些極端條件的測(cè)試,使得實(shí)驗(yàn)測(cè)試費(fèi)用異常的昂貴,甚至于高達(dá)上億美元。

為了很好的解決上述開發(fā)過程中遇到的問題,先進(jìn)完善的開發(fā)流程起到了關(guān)鍵的作用。國(guó)外的控制系統(tǒng)開發(fā)的主流模式已由上世紀(jì)六七十年代的“瀑布式”開發(fā)流程過渡到了自上世紀(jì)八十年代才開始的“基于模型”的開發(fā)流程,且在各個(gè)行業(yè)推廣開來。本世紀(jì)初,應(yīng)用實(shí)施仿真系統(tǒng)運(yùn)行大規(guī)模系統(tǒng)模型的開發(fā)測(cè)試模式開始普及,而國(guó)內(nèi)的“基于模型”的開發(fā)模式和實(shí)施仿真技術(shù)同時(shí)自本世紀(jì)初開始起步,經(jīng)過了十余年的推廣,也被廣大的企業(yè)和科研院所接受[9]。基于模型的設(shè)計(jì)通過早期驗(yàn)證,消除了在測(cè)試中發(fā)現(xiàn)的問題并回歸修正,在開發(fā)的過程中進(jìn)行持續(xù)驗(yàn)證,降低了最后系統(tǒng)集成后再進(jìn)行測(cè)試的復(fù)雜性。當(dāng)模型發(fā)生變化時(shí),可以通過模型比對(duì)進(jìn)行分析,提升了對(duì)需求變更的適應(yīng)性,同時(shí)使變更點(diǎn)易于比對(duì),降低了設(shè)計(jì)遺漏的可能性。

02

基于模型的設(shè)計(jì)

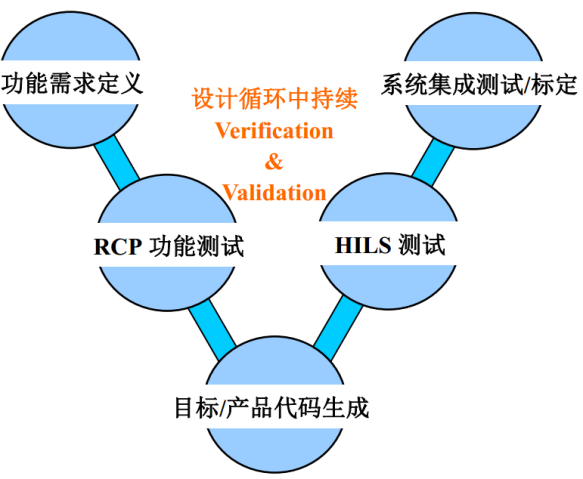

基于模型的設(shè)計(jì)流程,亦稱為“V”模式,依托計(jì)算機(jī)輔助控制系統(tǒng)設(shè)計(jì)(CACSD:

Computer-Aided Control System Design),將計(jì)算機(jī)支持工具貫穿于控制系統(tǒng)開發(fā)測(cè)試的全過程。該流程以模型為核心,流程中每一個(gè)步驟的開展都依賴于模型,其中“V”代表著“Verification”(驗(yàn)證)和“Validation”(確認(rèn))。這樣一套完整的系統(tǒng)開發(fā)流程,一般包含幾個(gè)步驟:

圖2-1 V流程設(shè)計(jì)步驟

從整個(gè)基于模型的現(xiàn)代控制系統(tǒng)設(shè)計(jì)開發(fā)流程看,主要有兩大特點(diǎn):

第一,以系統(tǒng)數(shù)學(xué)模型為核心,充分發(fā)揮仿真技術(shù)的優(yōu)勢(shì)。該流程可以分為離線仿真 → 快速原型 → 代碼生成 → 半實(shí)物測(cè)試 → 標(biāo)定,每一個(gè)步驟都依賴于系統(tǒng)模型。由于采用了仿真技術(shù),控制器在實(shí)物測(cè)試之前所有的開發(fā)測(cè)試工作均可在虛擬環(huán)境下進(jìn)行,在實(shí)驗(yàn)室條件下完成關(guān)鍵的開發(fā)測(cè)試工作。

第二,設(shè)計(jì)和確認(rèn)至始至終貫穿于整個(gè)開發(fā)流程。該流程的每一個(gè)步驟中,開發(fā)和測(cè)試是并重的。每一個(gè)步驟中的開發(fā)成果只有經(jīng)過完整可靠的測(cè)試才能進(jìn)入下一步,將各種錯(cuò)誤缺陷盡可能多的在早期發(fā)現(xiàn),避免帶入后期的開發(fā)環(huán)節(jié)。

其基本思想是讓具體開發(fā)工作從編程轉(zhuǎn)移到高級(jí)別的模型抽象中去,模型本身就是一個(gè)可執(zhí)行的規(guī)格書,開發(fā)人員修改優(yōu)化模型就是對(duì)設(shè)計(jì)的修改完善,同時(shí)可以開展設(shè)計(jì)驗(yàn)證,無須到編碼實(shí)現(xiàn)之后再通過測(cè)試進(jìn)行系統(tǒng)驗(yàn)證。由于具有圖形化設(shè)計(jì)、早期驗(yàn)證、代碼自動(dòng)生成、文檔自動(dòng)化等優(yōu)勢(shì),成為解決FPGA代碼規(guī)模快速膨脹問題的手段。利用開發(fā)驗(yàn)證一體化套件及兼容的第三方工具能夠完成基于模型的產(chǎn)品開發(fā)流程,包括建立基于需求的系統(tǒng)模型,并通過仿真驗(yàn)證和系統(tǒng)的設(shè)計(jì),然后自動(dòng)將模型生成代碼,進(jìn)行代碼測(cè)試和軟硬件集成后的系統(tǒng)級(jí)測(cè)試和驗(yàn)證。

03

HDL代碼自動(dòng)生成

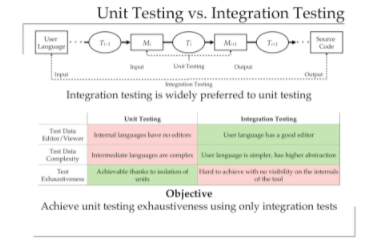

通過對(duì)基于模型設(shè)計(jì)方法的分析,可以看到該方法中的重要一環(huán)就是將模型直接轉(zhuǎn)換為可執(zhí)行代碼,把高級(jí)抽象語言描述的系統(tǒng)轉(zhuǎn)換為可綜合的邏輯代碼是近年來被廣泛研究的一個(gè)領(lǐng)域,目前有很多工具能夠?qū)/C++和Matlab描述的模型或代碼轉(zhuǎn)換為VHDL和Verilog代碼,工程師們可以很容易的通過這些工具從更高抽象層次的系統(tǒng)層面進(jìn)行模型的設(shè)計(jì)和仿真,并生成代碼。通過工具對(duì)模型的翻譯自動(dòng)生成代碼有效的減少了人為引入的理解誤差及錯(cuò)誤實(shí)現(xiàn)的可能性,同時(shí)自動(dòng)化的驗(yàn)證和確認(rèn)使測(cè)試工程師能夠開發(fā)完整的、基于需求并可在自動(dòng)產(chǎn)生的代碼上重用的測(cè)試用例。產(chǎn)品的代碼生成和驗(yàn)證過程留給工具軟件自動(dòng)完成,可以大大縮短開發(fā)周期和成本,降低開發(fā)難度,并且軟件的一致性好,軟硬件整合簡(jiǎn)單,可靠性高。

目前市場(chǎng)上,建模工具和代碼生成工具都很多,但能夠提供一體化建模、仿真和代碼生成解決方案的很少,能夠生成FPGA可用的可綜合邏輯代碼的更少[6]。目前,HDL代碼自動(dòng)生成,常用的工具包括Catapult CSPARK、ROCCC and DWARV(C to VHDL)、Xilinx為MATLAB定制的System Generator、AccelDSP 等。這些方法非常受系統(tǒng)工程師的青睞,因?yàn)樗麄儾槐厣钊雽?shí)際的硬件描述細(xì)節(jié),可以從高級(jí)規(guī)范開始構(gòu)建系統(tǒng),把關(guān)注點(diǎn)更多的投入到系統(tǒng)設(shè)計(jì)上。

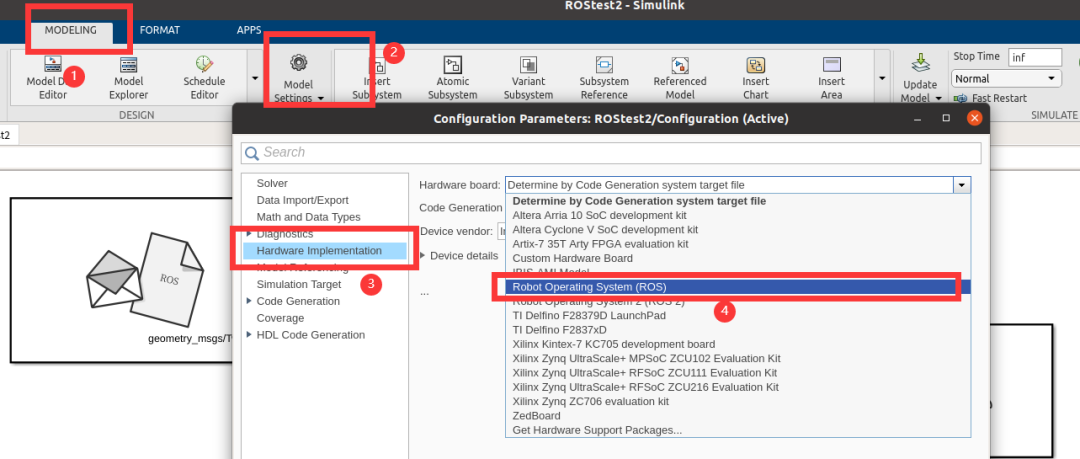

3.1 基于Matlab/Simulink的HDL代碼自動(dòng)生成

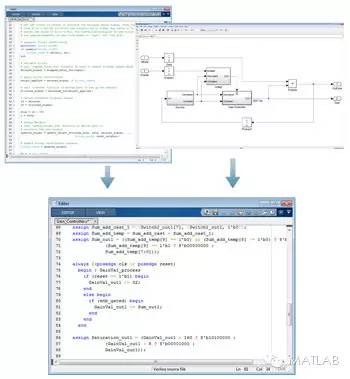

二十一世紀(jì)以來隨著應(yīng)用的不斷深入,高速?gòu)?fù)雜控制系統(tǒng)開發(fā)的需求日益增大,因此FPGA和“模型”的聯(lián)系越來越緊密。本世紀(jì)初Matlab便已應(yīng)用于控制器的開發(fā),利用模型的離線仿真來保證控制算法在設(shè)計(jì)初期就有較好的正確性[10]。之后Matlab工具軟件對(duì)FPGA的支持力度日益增強(qiáng),Mathworks和各大FPGA生產(chǎn)商合作推出了直接利用模型生成FPGA代碼的System Generator(支持Xilinx公司FPGA)和DSP Builder(支持Ahera 公司 FPGA)等工具包很大程度上推進(jìn)了FPGA在基于模型的設(shè)計(jì)流程中的使用率。從 2007年的Matlab2007a開始,Mathwork 提供了一個(gè) Simulink 工具HDL Coder,可以實(shí)現(xiàn)從Simulink 模型生成可綜合的HDL代碼,并提供從模型到具體變量的追蹤,實(shí)現(xiàn)代碼控制,HDL Coder技術(shù)使FPGA和Matlab的配合使用更加廣泛 ,相對(duì)于前面兩種工具包,它擺脫了FPGA制造廠商的束縛,使軟硬件接口更加通用化。

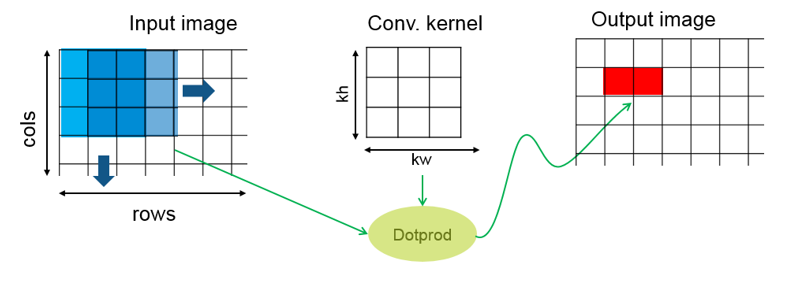

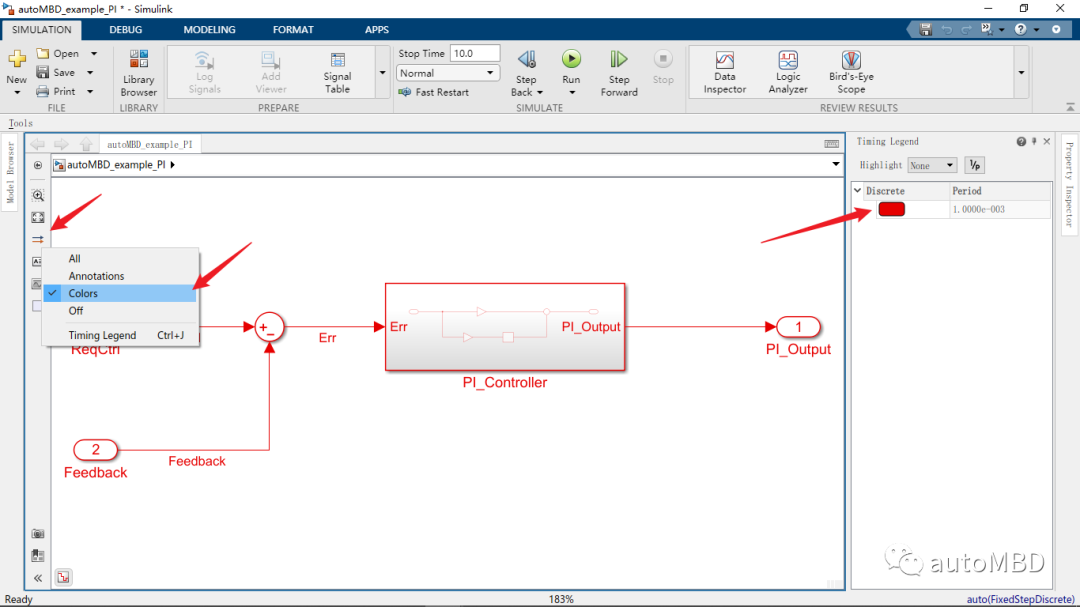

Matlab/Simulink基于模型設(shè)計(jì)的工具流程系統(tǒng)框圖如圖3-1所示。

圖3-1 Matlab/Simulink基于模型的設(shè)計(jì)流程圖

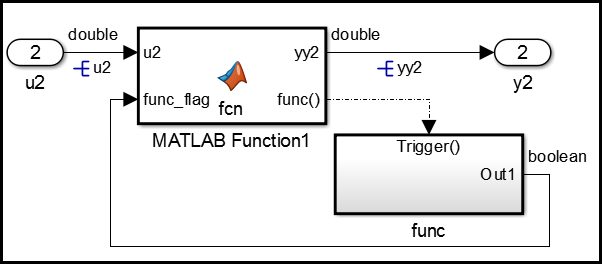

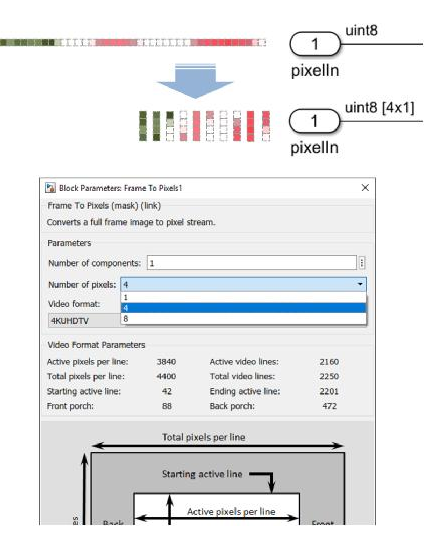

Simulink是建立在Matlab之上的系統(tǒng)級(jí)建模仿真基本環(huán)境,是一個(gè)圖形化的建模工具,從某種意義上講,凡是能夠用數(shù)學(xué)方式描述的系統(tǒng),都可以用Simulink建模,容易搭建的包括:通信系統(tǒng)物理層和數(shù)據(jù)鏈路層,控制系統(tǒng),數(shù)字信號(hào)處理系統(tǒng),動(dòng)力學(xué)系統(tǒng)。Real-Time Workshop(RTW)是基于Simulink的目標(biāo)代碼生成工具。HDL Verifier是用于驗(yàn)證的工具套件,提供的驗(yàn)證功能主要關(guān)注在模型仿真與生成HDL代碼的仿真結(jié)果一致性比對(duì)。在MATLAB開發(fā)環(huán)境中,要自動(dòng)生成面向FPGA的目標(biāo)代碼,需要使用simulink搭建算法或者系統(tǒng)的模型,然后通過RTW或者RTW提供給第三方代碼自動(dòng)生成工具(如HDL Coder、Xilinx System Generator、Altera DSP Builder等)的開放接口。

3.2 基于UML/MARTE模型的VHDL代碼生成方法

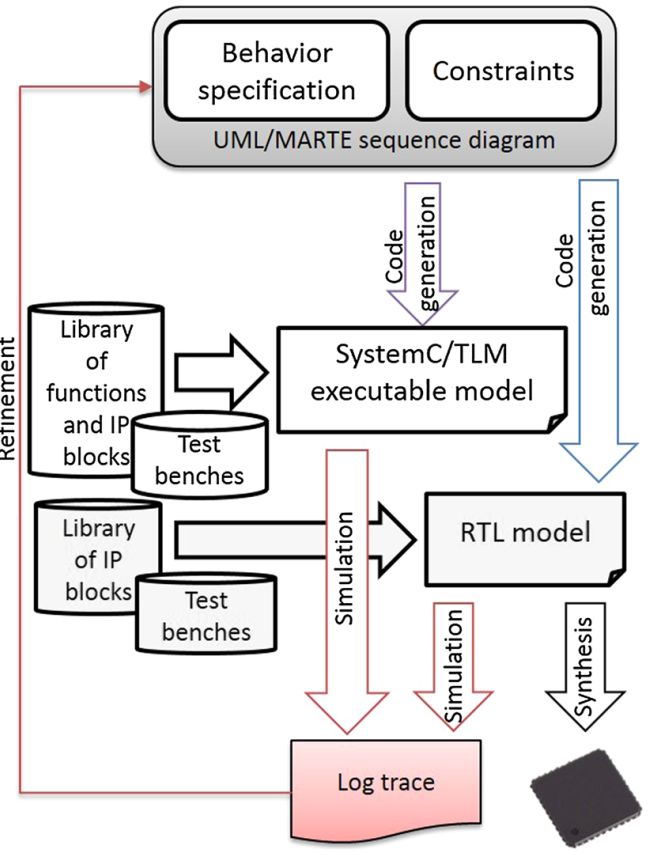

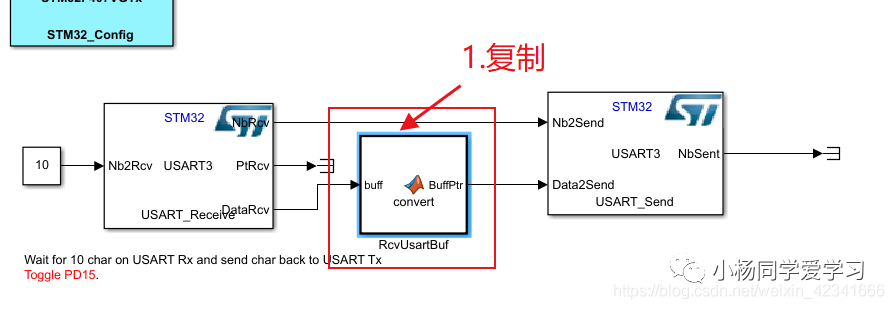

近年來,模型驅(qū)動(dòng)設(shè)計(jì)和統(tǒng)一建模語言(UML :Unified Modeling Language)作為一種與平臺(tái)無關(guān)的建模方法,在電子系統(tǒng)設(shè)計(jì)中得到了廣泛的關(guān)注。現(xiàn)存的幾種UML配置文件在UML級(jí)別建模硬件組件,并自動(dòng)生成代碼。其中實(shí)時(shí)和嵌入式系統(tǒng)的建模和分析[15](MARTE:Modeling and Analysis of Real-time and Embedded Systems),在UML圖中使用了時(shí)序的屬性。在實(shí)時(shí)嵌入式系統(tǒng)建模中最常用的UML圖之一是序列圖。序列圖表示應(yīng)用程序功能、不同組件之間的交互,并允許指定“時(shí)間不變量”。圖3-2中為基于UML/MARTE建模、驗(yàn)證和代碼生成流程。起點(diǎn)是UML/MARTE序列圖,它描述了系統(tǒng)的行為(在組件之間的數(shù)據(jù)交換)和時(shí)序約束。從這個(gè)描述中,生成了SystemC/TLM和VHDL模型,包含檢查約束的斷言調(diào)用。因?yàn)樾蛄袌D指定實(shí)體之間的數(shù)據(jù)交換,但不指定實(shí)體內(nèi)部的處理代碼;因此,生成的代碼要用于仿真還需要鏈接到可用的知識(shí)產(chǎn)權(quán)(IP)核心庫(kù)。仿真輸入一組合適的測(cè)試臺(tái),并生成一個(gè)約束報(bào)告。驗(yàn)證過程產(chǎn)生的結(jié)果,一方面,將仿真中獲得的新的信息反饋,用于細(xì)化UML模型及其約束。另一方面,將生成的VHDL代碼合成為硬件組件(如FPGA),從而獲得UML應(yīng)用的實(shí)際實(shí)現(xiàn)。GenERTiCA工具支持從UML模型自動(dòng)生成VHDL代碼[6]。

圖3-2 基于UML/MARTE建模、驗(yàn)證和代碼生成流程

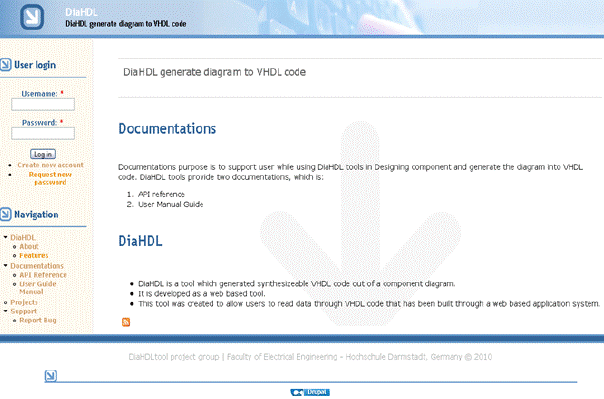

3.3 基于Web的VHDL代碼自動(dòng)生成工具DiaHDL[5]

DiaHDL是一款基于Web的VHDL代碼自動(dòng)生成工具,旨在尋找一種快速的直接方法,基于Web將可視化設(shè)計(jì)轉(zhuǎn)換為可綜合的VHDL代碼,設(shè)計(jì)實(shí)現(xiàn)了特殊圖形用戶界面(GUI),允許用戶選擇數(shù)字組建、定制參數(shù)并生成VHDL代碼,基于GUI的庫(kù)包含基本數(shù)字器件,基本的門電路,也包括復(fù)雜的FIR濾波器和DCT,同時(shí)支持用戶自定義的復(fù)雜電路系統(tǒng)。軟件通過JAVA腳本提取VHDL代碼參數(shù)。成功的案例包括圖像的JPEG編碼器等,完成從組件到比特文件的完整設(shè)計(jì)流程。圖3-3是工具的用戶界面截圖。

圖3-3 DiaHDL用戶界面

04

基于Matlab/Simulink的建模和HDL代碼自動(dòng)生成應(yīng)用現(xiàn)狀

Matlab/Simulink是目前在對(duì)全流程支持最完整的一套工具,能夠提供高性能動(dòng)態(tài)系統(tǒng)的仿真、分析和測(cè)試,并能夠完成從模型到代碼的轉(zhuǎn)換。通過圖形界面和基于語言的方法,使系統(tǒng)設(shè)計(jì)變得靈活易懂,易于開發(fā)和測(cè)試人員設(shè)計(jì)和調(diào)試,在國(guó)內(nèi)也有大量的技術(shù)支持并提供解決方案,因此本章節(jié)重點(diǎn)介紹基于Matlab/Simulink的建模和HDL代碼自動(dòng)生成應(yīng)用技術(shù)。目前,基于Matlab/Simulink的模型驅(qū)動(dòng)開發(fā)和HDL代碼生成技術(shù)已成功應(yīng)用于航天、航空、航海、醫(yī)療、電力、紅外成像、固態(tài)存儲(chǔ)、機(jī)器人控制等眾多領(lǐng)域,具體應(yīng)用包括無線數(shù)字收發(fā)器、音視頻處理、編解碼器、雷達(dá)信號(hào)處理、閃存控制器等,從原型設(shè)計(jì)到代碼實(shí)現(xiàn)平均開發(fā)時(shí)間縮短50%,典型的成功應(yīng)用情況如下:

1) Reutech 雷達(dá)系統(tǒng)公司采用基于模型的設(shè)計(jì)流程,開發(fā)艦載海空搜索雷達(dá)核心信號(hào)處理子系統(tǒng),完成系統(tǒng)級(jí)的仿真,自動(dòng)生成75,000多行HDL代碼,節(jié)省了兩個(gè)工程師人年,該雷達(dá)系統(tǒng)最后完成了探索性的海上試驗(yàn)。

2)美國(guó)的紅外熱成像技術(shù)領(lǐng)導(dǎo)企業(yè)FLIR在紅外攝像機(jī)的熱成像算法中應(yīng)用了模型驅(qū)動(dòng)開發(fā)的方法,從概念到現(xiàn)場(chǎng)可測(cè)試原型的時(shí)間減少了60%,重大算法更改從重新部署到代碼實(shí)現(xiàn),由幾周縮短為幾小時(shí),HDL代碼重用從零增加到30%。

3) Semtech通過基于模型的設(shè)計(jì)生成VHDL代碼,加快了無線RF設(shè)備優(yōu)化的數(shù)字接收器鏈的開發(fā),驗(yàn)證時(shí)間從數(shù)周縮短為幾天,并且最終交付的代碼性能更佳。

4)日本半導(dǎo)體生產(chǎn)商Siglead使用HDL Coder從定點(diǎn)Simulink模型生成VHDL代碼,并將其部署在Xilinx Spartan-6FPGA上,開發(fā)時(shí)間由4個(gè)月變?yōu)?個(gè)月,縮短了75%,設(shè)計(jì)迭代修改從三天變?yōu)槿齻€(gè)多小時(shí),設(shè)計(jì)人員能夠把更多的時(shí)間花在富有成效的算法開發(fā)和探索優(yōu)化設(shè)計(jì)上。

5)為了幫助心臟病學(xué)家檢測(cè)脂質(zhì)核心斑塊LCP(患有LCP更容易罹患冠心病),紅外線公司開發(fā)了TVC成像系統(tǒng)。美國(guó)的Infraredx使用Matlab/Simulink和HDL編碼器加速TVC成像系統(tǒng)中IVUS信號(hào)和圖像處理算法的開發(fā)和FPGA實(shí)現(xiàn),自動(dòng)生成的代碼與手寫的代碼使用了相同數(shù)量的乘法器,同時(shí)使用的邏輯減少了9%,使用的內(nèi)存減少了3%。

6) Philips Healthcare的工程師使用Simulink來建模由數(shù)字RF接收機(jī)、比較器、RF波形發(fā)生器和放大器組成的架構(gòu)。引入基于模型的設(shè)計(jì)方案后,使設(shè)計(jì)問題能夠早發(fā)現(xiàn)早解決,由于HDL Coder生成代碼具有很好的規(guī)范性,使代碼生成相對(duì)于手工編寫代碼的不一致性風(fēng)險(xiǎn)降低。

7)Renesas半導(dǎo)體的工程師為圖像處理算法開發(fā)和實(shí)施采用了基于模型的設(shè)計(jì),探索了多個(gè)設(shè)計(jì)優(yōu)化和替代方案并生成了高效的HDL代碼,該公司的工程師稱:“在進(jìn)行優(yōu)化后,自動(dòng)生成的代碼與我們最好的手工編寫代碼相比,基本上具有相同的區(qū)域和速度特性。由 HDL Coder生成的HDL代碼與手工編寫的同等HDL代碼相比,在120 MHz和275 MHz目標(biāo)時(shí)鐘頻率上使用的資源稍微少一些。并且,通過使用Simulink和HDL Coder,早前沒有硬件經(jīng)驗(yàn)的工程師在大概六個(gè)月內(nèi)學(xué)會(huì)了RTL設(shè)計(jì)。”

05

結(jié)論與展望

基于模型設(shè)計(jì)的HDL代碼生成技術(shù)目前還有很多有待研究和解決的技術(shù)問題,包括模型的建立、與系統(tǒng)代碼的融合、模型和自動(dòng)生成代碼的驗(yàn)證等等,雖然目前相關(guān)的方法和工具很多,比如Matlab/Simulink作為一套流程相對(duì)完整、友好的工具套件,已經(jīng)在各個(gè)領(lǐng)域有了成功的應(yīng)用案例,但是目前還存在很多應(yīng)用的局限性,相信通過不斷的學(xué)習(xí)和探索,并結(jié)合實(shí)際應(yīng)用進(jìn)行研究,一定能夠基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)使得到更廣闊、深入的應(yīng)用。

原文標(biāo)題:技術(shù)干貨分享-基于模型設(shè)計(jì)的HDL代碼自動(dòng)生成技術(shù)綜述

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論