PLL(phase-locked loop),即鎖相環。是FPGA中的重要資源。由于一個復雜的FPGA系統往往需要多個不同頻率,相位的時鐘信號。所以,一個FPGA芯片中PLL的數量是衡量FPGA芯片

2021-01-22 09:41:11 4667

4667

很多初學者看到板上只有一個50Mhz時鐘輸入的時候都產生疑惑,時鐘怎么才50Mhz?如果要工作在100Mhz、150Mhz怎么辦?在很多FPGA芯片內部都集成了PLL,其他廠商可能不叫PLL,但是

2021-02-04 13:22:00 6661

6661

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

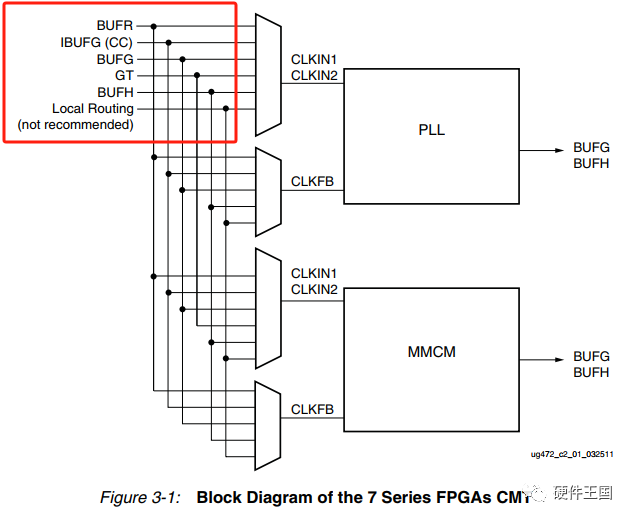

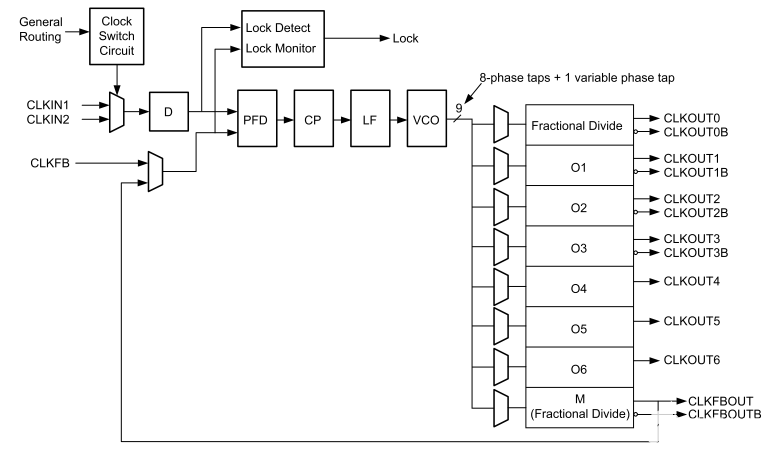

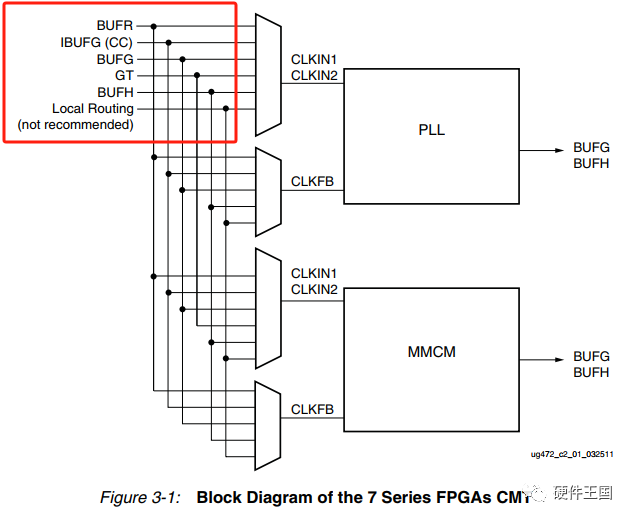

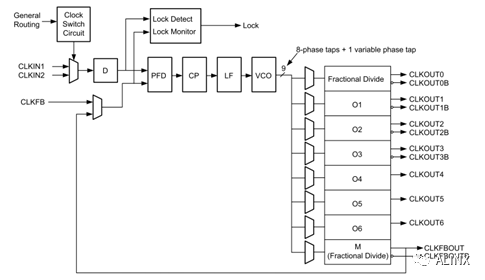

7系列FPGA包含最多24個CMT塊,CMT具體的分布和與其他時鐘資源的關系請參考本合集(FPGA應用開發)的上一篇文章。本文主要介紹CMT內部MMCM和PLL的區別以及在實際開發中怎么使用CMT,怎么實現跨時鐘區域,第一次讀者最好先閱讀上一篇文章——解剖時鐘結構篇。

2023-11-17 17:08:11 1347

1347

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

如題,這樣一來,pwm的時鐘哪怕是來自HCLK(029不支持PLL作為pwm時鐘)最高50MHZ,經預分頻器最少2分頻的話,時鐘最高只有25Mhz了?M0518pwm的預分頻器可以設為0,不分頻,并且可以用PLL作為時鐘,最高頻率可以達到100Mhz,相差4倍?

2023-06-19 08:14:45

我的用的FPGA是Cyclone Iv。其中PLL的數字電源是1.2v,模擬電源是2.5v。 我想用PLL輸出一個差分的時鐘信號作為前端AD的采樣時鐘,只是現在不知道pll 輸出的時鐘信號電壓是多少

2014-11-06 23:20:06

初學FPGA,聽說分頻貌似挺重要,是必備的基礎技能。小白的我今天就從奇偶分頻開始我的FPGA學習成長之路偶數分頻很簡單的哈,打字蠻累的,直接上代碼/*************6分頻

2016-03-30 11:35:51

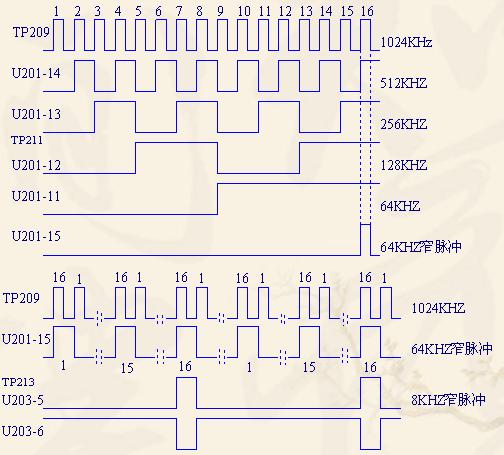

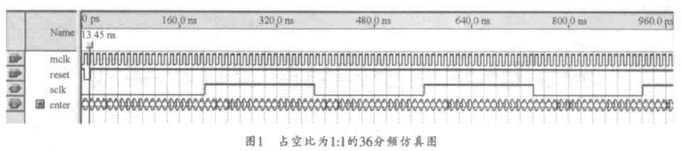

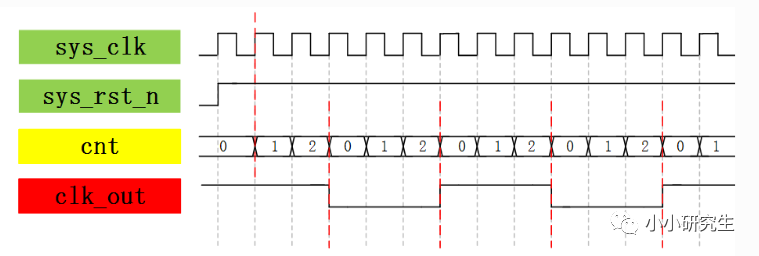

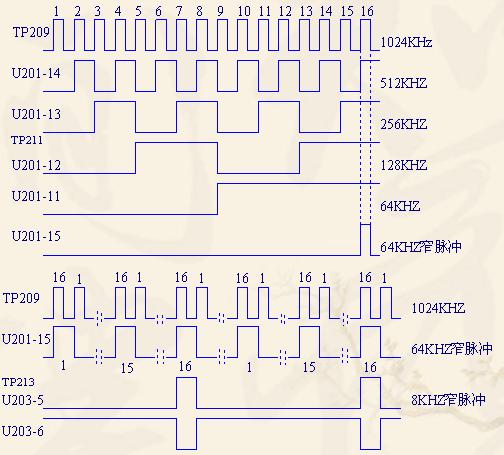

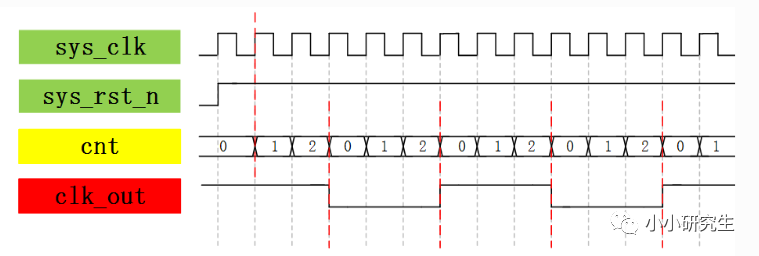

分頻器模塊實現的基本原理就是設計一個工作在系統時鐘下的計數器,循環地遞減或者遞加計數,在某個計數的固定值將輸出翻轉,即可實現時鐘分頻的功能。例如,實驗板上的系統時鐘是 50MHz,而所需的讀寫周期

2018-11-15 09:25:35

學習高手的FPGA編程程序,發現他寫的程序怎么這么冗余呢?懷著疑問,直到第二次閱讀另一高手的FPGA程序,才開始懷疑是自己錯了,原來使用時鐘使能而不直接使用分頻時鐘是原因的。查閱相關資料整理了一下

2018-08-08 11:13:26

誰幫忙設計一下模數轉換芯片ADC0809以及串行通信部分均需要有相應的時鐘驅動。而此次選擇的Altera CycloneⅡ系列FPGA中的EP2C5T144C8的系統時鐘為20MHz,因此根據需要

2014-05-09 11:53:23

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

分頻。讓我們來看一個例子:假如主時鐘50M,UART通信的波特率為9600,我們以16倍的波特率采樣,以保證數據準確,我們需要計50M/(9600*16)個主時鐘,即大約326個主時鐘才輸出一個分頻時鐘

2017-04-07 21:03:07

時鐘分頻電路實現精講

2013-04-18 12:07:20

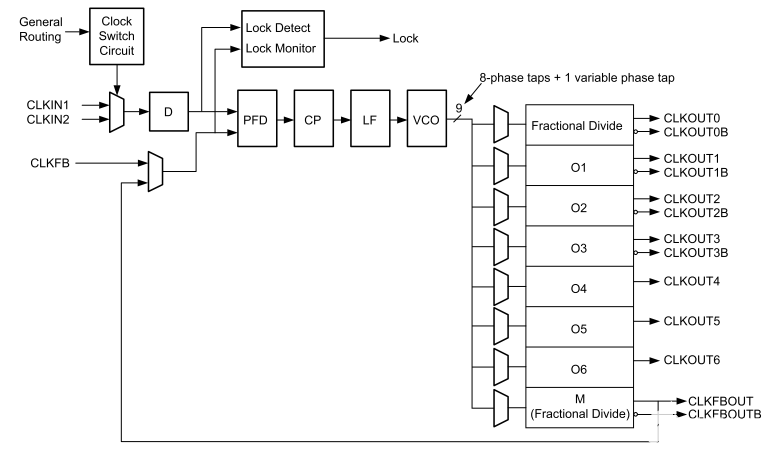

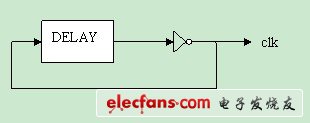

是基于一個外部的晶振時鐘,能夠先對晶振進行整數倍R分頻處理,作為PLL內部的基準時鐘,內部的環路可以對這個基準時鐘進行N倍的倍頻,因此可以得到外接晶振頻率F的N/R倍的頻率。鎖相環PLL的工作原理框圖

2019-06-06 04:20:03

應用系統的子系統,例如處理器、FPGA、數據轉換器等。此類復雜系統需要動態更新參考時鐘的頻率,以實現 PCIe 和以太網等其它諸多協議。時鐘 IC 屬于 I2C 從器件,需要主控制器來配置內部 PLL

2021-06-29 07:00:00

Actel FPGA PLL鎖相環的最大能達到幾倍頻幾分頻?我在網上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊里面找到資料,想要確認一下。

2014-12-04 11:25:15

16m*15倍頻,然后使用usb的時候需要設置五分頻,但是現在的問題是,我已經開到了16m*15倍頻,但是不置位11的話,pll的實際時鐘只有120m,到不了240m。

2022-10-18 06:33:13

作為一個新的系統時鐘,所有的設計都是基于這個時鐘來設計呢在編譯時候會出現警告,是一個關于buff的警告并且仿真時正確的,但是下載到硬件發現不是很符合設計要求查閱資料說有的CPLD里面會有PLL模塊,可是有的么有。沒有的用時鐘分頻后的信號作為新的時鐘觸發是不科學的,所以在此詢問各位大神。給個經驗說法吧

2013-04-25 09:39:35

不多說,上貨。IP CORE 之 PLL- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。Xilinx

2023-04-06 16:04:21

選擇位6 RTC時鐘選擇位7 PLL1分頻數寄存器8 PLL1倍頻寄存器9 系統時鐘選擇位10USB分頻寄存器11AHB分頻寄存器12APB1分頻寄存器13AHB總線14APB1外設總線15APB2分頻

2013-05-15 22:21:21

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2016-06-18 09:21:59

(RCC_HCLK_Div2); //設置APB1時鐘二分頻RCC_ADCCLKConfig(RCC_PCLK2_Div6); //設置ADC時鐘六分頻//設置PLL時鐘將8M時鐘9倍頻到72M

2018-07-19 03:40:25

STM32外部時鐘是怎樣通過PLL分頻得到PLLCLK的整個流程的?

2021-11-24 07:32:37

EG_PHY_PLL 是 FPGA 內部的時鐘鎖相環硬核 IP 模塊,Eagle 系列 FPGA 內嵌 4 個多功能鎖相環(PLL0~PLL3),分布在器件四角,可實現高性能時鐘管理功能。每個

2022-10-27 07:45:54

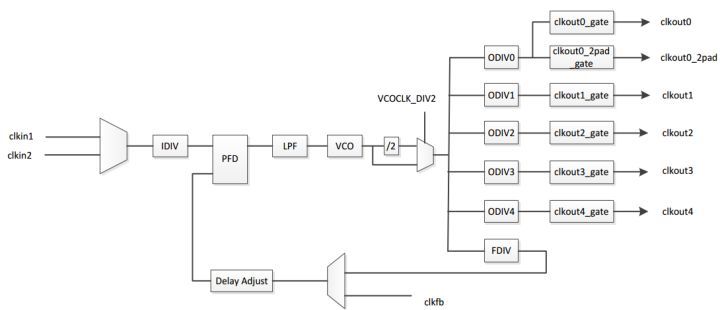

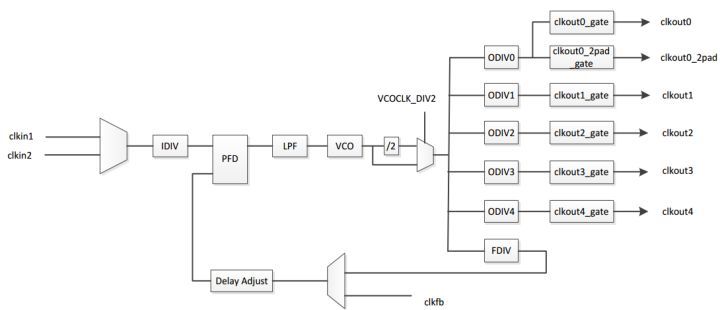

ELF2 系列 FPGA 內嵌 1 個多功能鎖相環(PLL),可實現高性能時鐘管理功能。可以實現時鐘分頻、倍頻、展頻、小數分頻、占空比調整、輸入和反饋時鐘對準、多相位時鐘輸出等功能。PLL 參考時鐘

2022-10-28 06:29:54

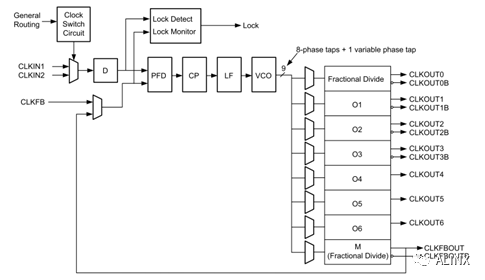

EF3 FPGA 內嵌 2 個多功能鎖相環(PLL),可以實現時鐘分頻、倍頻、占空比調整、輸入和反饋時鐘對準、多相位時鐘輸出等功能。PLL 的架構如圖 1 所示,包含鑒頻鑒相器(PFD)、壓控振蕩器(VCO)、低通濾波器(LPF)等基本電路。

2022-10-27 09:07:03

鎖相環路就可以實現這個目的。而我們在這里所說的PLL,沒有上面一段定義那么晦澀難懂,大家記住PLL一個最主要的功能,即能夠對輸入的基準時鐘信號進行一定范圍內的分頻或者倍頻,從而產生多個輸出時鐘信號供芯片

2015-11-10 08:44:06

進行調節,還可以對同一PLL生成的多個時鐘的相位進行控制,以保證兩個時鐘域的邏輯工作時有確定的時間差。具體鎖相環是通過何種方式實現對時鐘信號的分頻和倍頻的,這里我們不做講解,有興趣的朋友可以自己查閱相關

2017-01-05 00:00:52

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。FPGA中有若干個鎖相環PLL,這些鎖相環能夠對外部輸入的時鐘信號進行分頻倍頻,以得到比輸入

2020-02-20 14:32:13

在FPGA的設計中一直都擔任著很重要的角色,而說到分頻,我相信很多人都已經想到了利用計數器計數來得到想要的時鐘頻率,但問題是僅僅利用計數器來分頻,只可以實現偶數分頻,而如果需要三分頻、五分頻、七分頻

2019-12-11 10:15:33

有些朋友不理解為什么STM32時鐘要先倍頻N倍,再分頻?你會擔心這個值太大嗎?1寫在前面STM32時鐘的功能,可以說是越來越強大了。從各個系列的時鐘樹可以看得出來,最早F1系列的時鐘功能相對

2020-05-18 07:00:00

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2020-04-25 07:00:00

PLL唄。當然了,我們的FPGA里面定義的PLL,可不是僅僅只有一個反饋調整功能,它還有倍頻和分頻等功能集成其中。嚴格一點講,我覺得這個PLL實際上應該算是一個FPGA內部的時鐘管理模塊了。不多說,如圖

2016-09-12 17:31:43

AD9522-4 / PCBZ,用于AD9522-4的評估板是一款超低噪聲PLL時鐘合成器,具有集成VCO,時鐘分頻器和多達24個輸出。 AD9522具有自動保持功能和靈活的參考輸入電路,可實現非常

2019-02-22 09:35:23

較熟悉的分頻,通過計數器計數是完全可以實現的。如進行N倍偶數分頻,那么可以通過由待分頻的時鐘觸發計數器計數,當計數器從0計數到N/2-1時,輸出時鐘進行翻轉,并給計數器一個復位信號,使得下一個時鐘

2019-06-14 06:30:00

里面定義的PLL,可不是僅僅只有一個反饋調整功能,它還有倍頻和分頻等功能集成其中。嚴格一點講,我覺得這個PLL實際上應該算是一個FPGA內部的時鐘管理模塊了。不多說,如圖8.16所示,大家看看PLL內部

2018-04-10 21:57:51

`勇敢的芯伴你玩轉Altera FPGA連載62:基于PLL分頻計數的LED閃爍實例特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 如圖

2018-04-19 19:00:56

Altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求不太嚴格的設計,通過自主設計進行時鐘分頻的實現方法仍然非常流行。首先這種方法可以節省鎖相環資源,再者

2014-06-19 16:15:28

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數

2019-10-08 10:08:10

較熟悉的分頻,通過計數器計數是完全可以實現的。如進行N倍偶數分頻,那么可以通過由待分頻的時鐘觸發計數器計數,當計數器從0計數到N/2-1時,輸出時鐘進行翻轉,并給計數器一個復位信號,使得下一個時鐘

2019-07-09 09:11:47

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2017-04-15 11:56:58

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2017-05-05 14:34:19

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2018-09-25 11:38:18

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2014-05-13 10:10:50

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2016-05-23 10:27:23

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2016-08-23 10:31:08

從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。另外,STM32還可以選擇一個時鐘信號輸出到MCO腳

2016-08-25 09:40:03

基于特定的開發板上的時鐘策略:倍頻/分頻系數需要在使能 PLL 之前進行配置,所以需要在 Open PLL 之前將所有系統的時鐘分頻器系數以及PLL的倍頻系數配置好。整個時鐘的配置流程如下所示:(1

2021-08-23 09:12:44

10Gbps的serdes,它應該使用那個速度的PLL。正常,PLL速度固定為P(預分頻器,主分頻器和S),我想掃描窄,所以我應該使用小數N分頻PLL。無論如何,我找不到documnet PLL如何在FPGA中工作。有誰知道嗎?

2020-06-16 15:27:36

是否有評估板的外部(FPGA外部)時鐘分頻器而不是使用DCM或PLL?問候,半

2020-03-16 09:11:44

你們好,

我們正在使用AD9779A進行設計,有如下疑問:

(1) 使用AD9779A的數據時鐘信號(DATACLK)作為FPGA內部PLL的參考時鐘,再用FPGA PLL產生的時鐘信號把數據

2023-12-20 07:12:27

請問,想通過FPGA的PLL倍頻產生個500MHz的時鐘來使用,以此時鐘來做定時精密延遲,不知道PLL倍頻倍數有什么要求,比如好像有的器件支持不到500MHz,有沒有可推薦的器件呢

補充內容 (2017-1-4 09:26):

或者有大神用過類似能到500MHz的FPGA推薦么

2017-01-03 17:04:23

在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

78 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 摘要:介紹了為PET(正電子發射斷層掃描儀)的前端電子學模塊提供時間基準而設計的一種新型高頻時鐘扇出電路。該電路利用FPGA芯片來實現對高頻時鐘的分頻

2009-06-20 12:41:04 1238

1238

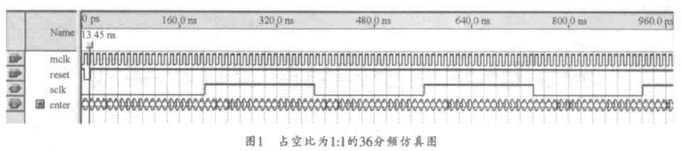

摘 要: 本文通過在QuartursⅡ開發平臺下,一種能夠實現等占空比、非等占空比整數分頻及半整數分頻的通用分頻器的FPGA設計與實現,介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

時鐘分頻及定時變換電路

2009-10-11 10:35:51 2033

2033

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1139

1139

為利用簡單的線纜收發器,實現中等數據率的串行數據傳輸,提出了一種基于電荷泵式PLL的時鐘數據恢復的方法。鑒相器由FPGA實現,用固定延時單元構成一條等間隔的延時鏈,將輸入信號經過每級延時單元后的多個輸出用本地的VCO時鐘鎖存,輸入信號的沿變在延時鏈

2011-03-15 12:39:34 90

90 該電路是低噪聲微波小數N分頻PLL的完整實現方案,以 ADF4156 作為核心的小數N分頻PLL器件。使用 ADF5001 外部預分頻器將PLL頻率范圍擴展至18 GHz。

2011-10-26 15:02:22 1333

1333

提出了一種基于FPGA的小數分頻實現方法,介紹了現有分頻方法的局限性,提出一種新的基于兩級計數器的分頻實現方法,給出了該設計方法的設計原理以及實現框圖

2011-11-09 09:36:22 121

121 給出了一種基于FPGA的分頻電路的設計方法.根據FPGA器件的特點和應用范圍,提出了基于Verilog的分頻方法.該方法時于在FPGA硬件平臺上設計常用的任意偶數分頻、奇數分頻、半整數分頻

2011-11-09 09:49:33 355

355 介紹了一種基于FPGA的雙模前置小數分頻器的分頻原理及電路設計,并用VHDL編程實現分頻器的仿真.

2011-11-29 16:43:06 48

48 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 178

178 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 普通IO可以通過BUFG再連到PLL的時鐘輸入上,但要修改PLL的設置 input clk的選項中要選擇"No Buffer";

2017-02-09 12:54:11 6825

6825

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。

2017-02-11 12:33:40 10916

10916 分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠家集成的鎖相環資源,如賽靈思(Xilinx)的DLL.來進行時鐘的分頻,倍頻以及相移。

2017-02-11 13:36:36 12409

12409

STM32中有一個全速功能的USB模塊,其串行接口引擎需要一個頻率為48MHz的時鐘源。該時鐘源只能從PLL輸出端獲取,可以選擇為1.5分頻或者1分頻,也就是,當需要使用USB模塊時,PLL必須使能,并且時鐘頻率配置為48MHz或72MHz。

2017-11-30 09:14:18 6833

6833

輸入FPGA引腳上的25MHz時鐘,配置PLL使其輸出4路分別為12.5MHz、25MHz、50MHz和100MHz的時鐘信號,這4路時鐘信號又分別驅動4個不同位寬的計數器不停的計數工作,這些計數器

2018-04-24 11:20:01 4012

4012

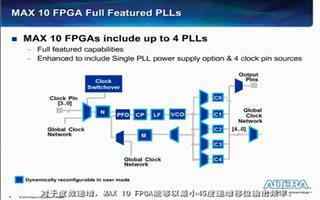

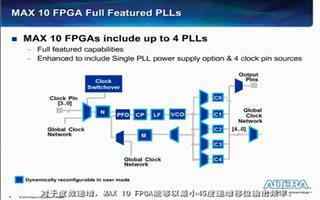

MAX 10 FPGA PLL和時鐘培訓,此次培訓涉及到器件系列的時鐘特性和選項。有20個全局時鐘網絡,全局CLK輸入引腳數量也可以加倍,用作通用IO引腳。并且采用動態用戶控制進行各種選擇和電源控制,構建魯棒的時鐘網絡源。它所有4個PLL都是全功能的。

2018-06-20 08:00:00 2325

2325

分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求

2019-08-07 08:00:00 9033

9033

先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 2456

2456

通常情況下,時鐘的分頻在FPGA設計中占有重要的地位,在此就簡單列出分頻電路設計的思考思路。

2020-07-10 17:18:03 2192

2192 PLL 是一種用來同步輸入信號和輸出信號頻率和相位的相位同步電路,也可用來實現時鐘信號的倍頻(產生輸入時鐘整數倍頻率的時鐘)。在 FPGA 芯片上,PLL 用來實現對主時鐘的倍頻和分頻,并且 PLL

2020-11-16 17:04:44 3292

3292 Cyclone FPGA 具有鎖相環(PLL)和全局時鐘網絡,提供完整的時鐘管理方案。Cyclone PLL 具有時鐘倍頻和分頻、相位偏移、可編程 占空比和外部時鐘輸出,進行系統級的時鐘管理和偏移

2021-01-15 14:38:00 24

24 很多初學者看到板上只有一個25Mhz時鐘輸入的時候都產生疑惑,時鐘怎么是25Mhz?如果要工作在100Mhz、150Mhz怎么辦?其實在很多FPGA芯片內部都集成了PLL,其他廠商可能不叫PLL

2022-02-08 15:13:17 3306

3306

很多初學者看到板上只有一個25Mhz時鐘輸入的時候都產生疑惑,時鐘怎么是25Mhz?如果要工作在100Mhz、150Mhz怎么辦?其實在很多FPGA芯片內部都集成了PLL,其他廠商可能不叫PLL

2021-01-29 09:30:52 7

7 程序實現對輸入時鐘信號的7分頻介紹。

2021-03-17 14:59:23 11

11 AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

2021-03-21 15:32:58 11

11 AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

2021-05-08 20:05:05 5

5 一種基于FPGA的分頻器的實現說明。

2021-05-25 16:57:08 16

16 外部晶振+內部時鐘震蕩器+內部PLL +內部分頻器產生時鐘,性能高一點的MCU基本都采用這種方案。

2022-08-31 18:04:08 864

864 ,但 FPGA 由于器件本身和工具的限制,分頻時鐘和源時鐘的Skew不容易控制(使用鎖相環分頻是個例外),難以保證分頻時鐘和源時鐘同相,因此推薦的方法是使用時鐘使能,通過使用時鐘使能可以避免時鐘“滿天飛”的情況,進而避免了不必要的亞穩態發

2023-01-05 14:00:07 949

949 板載晶振提供的時鐘信號頻率是固定的,不一定滿足需求,因此需要對基準時鐘進行分頻。要得到更慢的時鐘頻率可以 分頻 ,要得到更快的時鐘頻率可以 倍頻 。我們有兩種方式可以改變頻率,一種是 鎖相環 (PLL,后面章節會講解),另一種是用 Verilog代碼描述。

2023-06-23 16:52:00 1149

1149

基于FPGA的高頻時鐘的分頻和分頻設計

2023-08-16 11:42:47 0

0 用FPGA的鎖相環PLL給外圍芯片提供時鐘 FPGA鎖相環PLL(Phase-Locked Loop)是一種廣泛使用的時鐘管理電路,可以對輸入時鐘信號進行精確控制和提高穩定性,以滿足各種應用場

2023-09-02 15:12:34 1319

1319 為什么單片機內置時鐘源不經過pll也可以分頻?? 單片機內置時鐘源不經過PLL也可以實現分頻,原因在于單片機內置時鐘源自帶分頻器,可以通過軟件設置分頻系數來控制內部時鐘頻率。 在單片機內部,通常會

2023-09-02 15:12:45 597

597 是接受外部時鐘信號。這些時鐘信號是非常重要的,因為它們可以幫助FPGA的內部邏輯和時序同步,并保證系統的穩定性和正確性。 對于這些專用管腳進入的時鐘信號,Altera的FPGA提供了一種特殊的電路,即鎖相環(PLL)。PLL是一種電路,它可以將輸入的時鐘信號倍頻、分頻或者頻率變化。 要接入固定的

2023-10-13 17:40:00 297

297 分頻器設計 一:分頻器概念 板載時鐘往往 是 有限個( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在設計中需要其他時鐘時,板載時鐘不滿足時,需要對板載時鐘進行分頻 / 倍頻,目的

2023-11-03 15:55:02 471

471

其實這個分頻時鐘切換很簡單,根本不需要額外的切換電路。一個共用的計數器,加一點控制邏輯,就可以了,而且可以實現2到16任意整數分頻率之間的無縫切換。

2023-12-14 15:28:56 257

257

鎖相環整數分頻和小數分頻的區別是什么? 鎖相環(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進行同步,并生成輸出信號的一種技術。在PLL中,分頻器模塊起到關鍵作用,可以實現整數分頻

2024-01-31 15:24:48 312

312

電子發燒友App

電子發燒友App

評論