摘要: SoC是超大規模集成電路的發展趨勢和新世紀集成電路的主流[1]。其復雜性以及快速完成設計、降低成本等要求,決定了系統級芯片的設計必須采用IP(Intellectual Property)復用的方法。本文介紹以可復用IP設計方法,設計串行外設接口SPI(Serial Peripheral Interface)模塊IP核的思路,用Verilog語言實現,并經FPGA驗證,通過TSMC(***集成電路制造公司)的0.25μm工藝生產線流水實現,完成預期功能。

關鍵詞: SoC 可復用IP SPI AMBA總線

引 言

??隨著集成電路設計技術和深亞微米制造技術的飛速發展,集成電路的規模越來越大,出現了片上系統SoC(System on Chip,又稱之為系統級芯片)。由于其在速度、功耗和成本方面的優勢,發展勢頭迅猛。SoC芯片是一個復雜的系統,為了在規定時間完成設計,并提高設計的可靠性,只有依賴基于IP復用的SoC設計方法。如何為SoC設計提供可復用的IP核,成為SoC設計的基礎和難點。

東南大學ASIC系統工程技術研究中心針對AMBA(Advanced Microcontroller Bus Architecutre,先進微控制器)總線規范開發了一款代號為Garfield的嵌入式微處理器。此微處理器除采用ARM公司ARM7TDMI內核的硬IP外,其余模塊采用了自己開發的軟IP。本文以串行外設接口SPI為例,介紹基于復用的IP設計與驗證的一些經驗。此SPI模塊基于AMBA的APB(Advanced Peripheral Bus,先進外設總線)規范,可以不作修改地應用在任何符合AMBA總線規范的微處理器設計中。

Garfield的總體架構及SPI模塊在系統中所處的位置如圖1所示。

1 可復用IP核的SoC設計方法

系統級芯片設計中,IP特指經過驗證的各種超級宏單元模塊電路。VSIA(虛擬器件接口聯盟)根據設計層次,將IP劃分為三個層次:硬IP、軟IP和介于兩者之間的固IP。硬IP性能最優但適應性較差,軟IP靈活性大、可移植性好。IP核必須具有以下特征[2]:①可讀性;②設計的衍展性和工藝適應性;③可測性;④端口定義標準化;⑤版權保護。

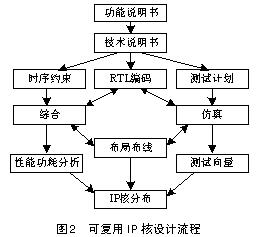

代碼編寫規則和可綜合的書寫規范是實現IP核的基礎,可保證IP軟核在任何EDA工具下編譯和綜合的正確性。為SoC集成時消除綜合產生的風險,我們制定了Verilog代碼的書寫規范,并要求有詳細的注釋,易于他人理解和修改。可復用IP設計流程如圖2所示[3]。

為了容易地將IP集成到芯片中,需要標準化的接口或片上總線,VSIA在這方面作了一定的工作。另外,設計中要盡量將IP核接口部分與功能部分分開,單獨作為一模塊進行設計,當需要集成到其它互連協議中時,只需修改接口部分。為盡可能地提供靈活性,允許綜合時設置多個參數。

在最終面向用戶的產品發布中,用戶手冊是非常重要的部分。這部分文檔將被用于IP核的選擇、集成和驗證,是一種非常專業化的文檔。它主要包括模塊系統結構、功能框圖、輸入/輸出口、時序圖、調用方式、設計流程、測試指導、推薦使用的軟件編譯器和驅動程序、系統驗證指導、調試指導和該IP核版本歷史等。在可重用IP核產品發布中,還應包含該IP核的多種仿真模型,以便用戶在進行評估、設計和系統測試時使用。IP核的仿真模型一般可分為3個層次:①行為級模型,能夠仿真該IP核的全部功能,包括在算法級和指令集上的功能;②硬件級模型,能夠精確提供該IP核的功能和時序的仿真;③門級模型,提供硬核的帶有時序反標注信息的仿真模型。

在實踐中,我們摸索出一套基于CVS(協作版本管理系統)的版本管理和設計、驗證人員協同工作的制度流程,對RTL代碼作了盡可能全面的仿真,提供完備的測試矢量,保證了最終IP核的質量,并按要求建立了標準、規范的文檔。

2 SPI模塊IP核的設計

串行外圍設備接口SPI(Serial Peripheral Interface)總線技術是Motorola公司推出的多種微處理器、微控制器以及外設間的一種全雙工、同步、串行數據接口標準[4]。SPI總線是一種三線總線,因其硬件功能很強,所以,與SPI有關的軟件就相當簡單,使CPU有更多的時間處理其它事務。

2.1 SPI模塊的接口信號及時序要求

(1)內部總線接口

AMBA規范是由ARM公司制定的片上總線規范,為SoC的設計提供了以下優點:較好的可移植和可復用設計、低功耗設計、高性能和結構可移植的系統設計以及較好的可測性設計[5]。SPI是APB總線上的Slave模塊。APB總線時序比較簡單,有興趣的讀者可以查閱ARM公司的《AMBA Specification》(Rev 2.0)。因為此SPI模塊支持3種DMA操作,所以除標準APB信號線外,還有3根與DMA模塊連接的請求信號線。

(2)SPI總線接口及時序

SPI總線包括1根串行同步時鐘信號線以及2根數據線。

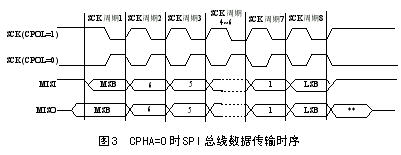

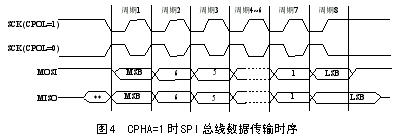

SPI模塊為了和外設進行數據交換,根據外設工作要求,其輸出串行同步時鐘極性和相位可以進行配置,時鐘極性(CPOL)對傳輸協議沒有重大的影響。如果CPOL=0,串行同步時鐘的空閑狀態為低電平;如果CPOL=1,串行同步時鐘的空閑狀態為高電平。時鐘相位(CPHA)能夠配置用于選擇兩種不同的傳輸協議之一進行數據傳輸。如果CPHA=0,在串行同步時鐘的第一個跳變沿(上升或下降)數據被采樣;如果CPHA=1,在串行同步時鐘的第二個跳變沿(上升或下降)數據被采樣。SPI主模塊和與之通信的外設間時鐘相位和極性應該一致。SPI接口時序如圖3、圖4所示[4]。

2.2 SPI模塊功能設計

根據功能定義及SPI的工作原理,將整個IP分為8個子模塊:APB接口模塊、時鐘分頻模塊、發送數據FIFO模塊、接收數據FIFO模塊、狀態機模塊、發送數據邏輯模塊、接收數據邏輯模塊以及中斷形成模塊。

深入分析SPI的四種傳輸協議可以發現,根據一種協議,只要對串行同步時鐘進行轉換,就能得到其余的三種協議。為了簡化設計規定,如果要連續傳輸多個數據,在兩個數據傳輸之間插入一個串行時鐘的空閑等待,這樣狀態機只需兩種狀態(空閑和工作)就能正常工作。相比其它設計,在基本不降低性能的前提下,思路比較精煉、清晰。

此SPI模塊有兩種工作方式:查詢方式和DMA方式。查詢方式通過處理器核監視SPI的狀態寄存器來獲知其所處的狀態,從而決定下一步動作。DMA方式由DMA模塊控制數據在內存和SPI間的交換,而不需要處理器核的參與,有效提高了總線利用率。

3 EDA軟件仿真與FPGA驗證

為了保證設計的魯棒性,運用多種方法對此IP的功能進行了全面的仿真和驗證。

首先進行EDA軟件仿真驗證。這種仿真包括RTL級和門級仿真驗證。RTL級仿真只是將代碼文件調入硬件描述語言的仿真軟件進行功能仿真,檢查邏輯功能是否正確。門級仿真包括布局布線前和布局布線后仿真。布局布線后仿真,可以獲得比較精確的時延參數,能夠比較真實地反映芯片制造完成后,模塊在實際工作中的行為與性能,所以通過了此類仿真就認為模塊設計成功,可以進行流片。將RTL級代碼轉換成門級網表,使用的是Synopsys公司的綜合工具DC(Design Compiler)以及***集成電路制造公司(TSMC)的0.25μm標準單元庫。

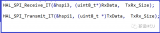

在傳統的設計流程中進行功能驗證,首先需要通過寫測試矢量的方式給需要進行功能測試的模塊加激勵,然后通過觀察模塊的輸出結果,判斷模塊的功能是否正確。但是在寫測試矢量時,測試工程師是在自己對模塊功能理解的基礎上進行的。這樣就存在一個問題,測試矢量對模塊的激勵有可能是不完備的,還有可能是錯誤的。由此有可能模塊的功能是錯誤的,但測試矢量的激勵并沒有使錯誤體現出來;也有可能模塊的功能是正確的,誤報錯誤使驗證過程變得非常低效[5]。為避免以上問題,在模塊的功能驗證中,采用系統級驗證環境。該環境由IP 總線、驅動器、監視器、外部模塊和協調它們工作的腳本組成。組成系統的各模塊可以按需要加入環境。每次驗證過程就是相應的激勵作用于環境的過程。驗證結果由環境產生、檢驗和輸出。該驗證環境在SOLARIS5.8操作系統下,仿真器采用Synopsys公司的VCS,支持C/C++、Verilog和VHDL協同仿真,可以直接將SPI模塊掛在驗證環境中,通過Verilog的$readmemh任務讀入軟件激勵進行驗證。

在系統時鐘為66MHz,CPOL=1、CPHA=0下收發6字節數據的仿真結果如圖5、6所示。

SPI模塊的典型應用是:通過與帶SPI接口的觸摸屏控制芯片連接,提供對觸摸屏的支持。針對此目標,將SPI模塊及其它必要模塊加載到FPGA中進行硬件、軟件聯合調試,對實際電路進行驗證。我們選用了最常見的四線式電阻式觸摸屏,而觸摸屏控制芯片采用ADS7843。ADS7843是一個內置12位模數轉換、低導通電阻模擬開關的串行接口芯片,支持8和12位的A/D轉換精度。為了完成一次電極電壓切換和A/D轉換,微處理器需要先通過SPI接口往ADS7843發送控制字,轉換完成后再通過SPI接口讀出電壓轉換值。標準的一次轉換需要24個時鐘周期[6]。典型的應用電路如圖7所示。

SPI的FPGA驗證平臺包括ARM公司提供的Intergrator/LM-EP20K1000E和Intergrator/CM7TDMI開發驗證板以及Garfield II驗證電路板(自行設計)。其中Intergrator/CM7TDMI上的ARM7TDMI微處理器內核作為整個開發系統的CPU。通過ARM Multi-ICE,將驗證必需的包括SPI在內的所有模塊由JTAG口加載到Intergrator/LM-EP20K1000E板上Altera APEX20KE系列的EP20K1000EFC672中。外圍電路由Garfield II驗證電路板(包含ADS7843)以及觸摸屏組成。在FPGA上通過軟硬件協同驗證,通過邏輯分析儀觀測SPI總線信號,也證明此SPI模塊性能良好。

另外,通過***集成電路制造公司(TSMC),采用其0.25μm標準單元庫對該設計多次進行流水驗證,獲得的實際IP電路在樣機中工作十分穩定。至此,IP的設計十分成功。當設計相似架構的SoC芯片時,可根據需要配置相應參數后直接進行復用。

結 語

建立經過充分驗證的功能正確、性能良好的可復用IP模塊庫,是快速進行SoC設計的基礎和要求。設計可復用的IP,需要遵守一定的設計方法:完整、清晰的文檔;良好的代碼風格;詳細的注釋;精心設計的校驗環境;極高代碼覆蓋率的測試向量等。本文以SPI模塊IP為例,按照規范的流程和要求,進行了初步的嘗試,得到了較好的結果。

參考文獻

1 魏少軍.SoC設計方法學.電子產品世界,2001(5):36~38

2 陳嵐,等. 單片系統(SoC) 設計技術. 計算機研究與發展,2002, l39(1):11

3 沈戈,等. 基于可重用IP的SOC設計方法學的研究. 西安石油學院學報(自然科學版),2003,l18:72

4 Xilinx Limited. CoolRunner-II Serial Peripheral Interface Master. 2002

5 宋紅東.基于嵌入式微處理器的系統級驗證方法研究與多媒體加速模塊的實現[D]. [碩士學位論文]. 南京:東南大學,2003

6 Burr-Brown Limited. Touch Screen Controller ADS7843

7 David Flynn. AMBA:Enabling Reusable On-Chip Design. IEEE Micro. July/August 1997

電子發燒友App

電子發燒友App

評論