引言

LCD因具有工作電壓低、功耗小、顯示信息量大、壽命長、易集成、方便攜帶和電磁輻射污染小等優點,在顯示技術中異軍突起,被廣泛應用于手機、PDA產品、手持式儀器儀表等便攜式電子產品與設備中。

LCD驅動電路是液晶顯示系統的重要組成部分,是一種計算機(或MCU)和液晶屏之間的接口電路,其主要功能是通過調制輸出到液晶顯示器件電極上的電位信號的相位、峰值、頻率等參數來建立交流驅動電場。由于LCD的規格相差較大,常規的方法是針對每一種LCD開發專門的驅動電路,這樣的設計浪費時間,而且復用性較差。為此,設計一種可用于多數小規模LCD驅動電路的IP核,通過復用該IP核來解決這個問題是非常必要的。目前,國際上只有I-Shou大學的Yu-Jung Huang等人設計了可驅動不同規模LCD的驅動電路IP核,通過在系統中植入嵌入式微處理器來實現這一功能。但是,這種嵌入式微處理器使系統更復雜,而且成本更高。本文設計的可驅動不同規模LCD的驅動電路IP核是采用FPGA來實現的,能有效克服電路系統復雜和高成本這兩個缺點。

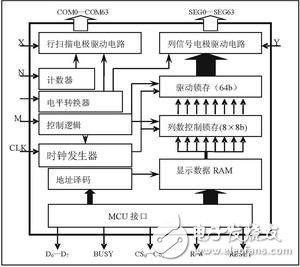

圖1 IP核系統結構

圖2 IP核級聯排列圖

圖3 行控制功能仿真結果

圖4 列控制功能仿真結果

設計規范

為了滿足當今大多數較小規模的LCD顯示應用的實際需要,本文所設計的LCD驅動電路IP核芯片具有64個COM(行)和64個SEG(列)輸出,有高速的8位并行MCU接口及串行接口,芯片內含有存儲顯示數據的RAM,并專門設計了10個控制端,可以方便靈活地進行控制。它主要有以下幾個主要功能:

1、為液晶顯示屏提供掃描時序信號和顯示信號數據;

2、支持以總線形式直接與MCU相連;

3、可驅動不同規模的LCD(n×m),n可以連續取值(n=0~63),m只可取8的倍數(m=8k,k取自然數);

4、支持IP核之間的級聯以驅動較大規模的LCD,最大分別支持4個IP核行間級聯和列間級聯;

5、可以提供較寬的驅動輸出電壓范圍以適應不同的LCD器件;

6、提供畫中畫、分屏顯示等功能。

IP核的設計

本文按照“自頂向下”的設計方法,首先對芯片進行層次化功能劃分,同時參照已有的LCD驅動芯片的設計經驗, 并結合“自底向上”的設計方法對部分模塊進行設計, 最后根據系統設計框架對各模塊進行協調, 并進行芯片的整體功能驗證, 從而達到了設計規范的要求。

系統結構

本文設計的IP核系統結構如圖1所示。該IP核主要由下列幾個模塊組成:行掃描和列信號驅動模塊、電平轉換器、可預置數環形計數器、數據鎖存模塊、控制邏輯模塊、顯示數據RAM與地址譯碼模塊、MCU接口模塊。其中有的大模塊還可細分為若干子模塊。

各模塊設計

MCU接口模塊

MCU接口模塊是IP核與外部控制器(MCU)通信的接口,是數據傳輸的通道。MCU通過該接口對LCD驅動芯片寫入命令、讀出狀態或顯示數據。同時該接口也接受命令譯碼器的控制,從而使讀寫與內部操作相結合。該芯片由較為復雜的內部組合邏輯和時序邏輯電路實現,可以兼容目前兩種主流的MCU控制信號,支持串/并行兩種數據操作方式。

該模塊內部除了包含現有常用LCD驅動電路的MCU接口模塊中常用的幾個子模塊,如數據總線(8位)子模塊、忙狀態檢測子模塊、讀寫控制子模塊、MCU釋放子模塊外,新加入了一個行級聯和列級聯控制子模塊。數據總線主要用于內外部數據交換;忙狀態檢測子模塊用于判斷MCU狀態,產生系統忙標志信號來協調信號的讀寫操作和接收內/外部復位信號;讀寫控制子模塊用于產生正確的讀寫控制時序;MCU釋放子模塊的功能則為通過邏輯組合,在芯片執行“讀-修改-寫”過程時,釋放MCU,以便MCU可以同時執行其它操作;而新加入的級聯控制子模塊的主要功能是實現IP核之間的行級聯和列級聯,最多可支持16個IP級聯(行列各4級),CS0~CS1是行級聯控制端,CS2~CS3是列級聯控制端。舉例說明,假設有一種LCD(128×256),可用8個IP核來驅動,設置時分別令CS為0000、0001、0010、0011、0100、0101、0110、0111,就可以構成2×4的驅動IP核陣列,其排列示意圖如圖2所示。

顯示數據RAM與地址譯碼模塊

該模塊主要用于存放將要顯示的數據,在MCU接口和信號驅動電路之間起緩沖器的作用,以保證顯示數據的穩定輸出。

該模塊包括存儲顯示數據的RAM陣列和地址譯碼器兩個子模塊。首先,由列地址電路提供列地址,通過列地址譯碼器選中一列8位的RAM存儲單元,MCU通過接口對其進行讀/寫;然后,由行地址譯碼器對RAM以行為單位進行掃描,結合顯示數據鎖存電路可以實現整行數據的輸出,通過電極驅動電路輸出到液晶顯示器以供顯示。

數據鎖存模塊

該模塊包含兩個子模塊:列數控制鎖存子模塊和驅動鎖存子模塊。列數控制鎖存子模塊由k個并聯的8位數據鎖存器構成,主要作用是鎖存數據總線上的數據,在控制邏輯模塊的控制信號和時鐘信號作用下把從RAM上輸出到8位數據總線上的顯示數據信號分別鎖存在相應的8位數據鎖存器中,64位數據需要8次,每次8位輸入。驅動鎖存器子模塊是一個由64個1位鎖存器并聯而成的64位驅動鎖存器,它的作用是在控制邏輯模塊的控制信號和時鐘信號作用下把上面8個8位數據鎖存器里傳輸來的m位數據一次全部鎖存起來,然后輸入到后面的列信號電極驅動模塊。

控制邏輯模塊

該模塊的主要作用是控制信號數據傳輸和選擇列信號線的數目。可以通過列數控制輸入端M來控制列數控制鎖存器子模塊、驅動鎖存器子模塊和時鐘發生器來實現適用于不同規模LCD的功能。根據需要,通過向列數控制輸入端M輸入不同的數值,來控制有多少位列數控制鎖存器處于工作狀態,其他的鎖存器單元則置為空閑態。在工作周期內把顯示數據RAM中的數據通過8位數據總線鎖存到對應的列數控制鎖存器中,然后在一個時鐘信號控制下一次鎖存到驅動鎖存器中,以作為電極驅動模塊的輸入信號。這樣,IP核可以實現控制選擇驅動列數的功能。當M為“000”時,列數控制鎖存器的低8位(第一個鎖存器)工作,其它的全置閑,對應的列電極是SEG0~SEG7;當M為“001”時,列數控制鎖存器的低16位(第一和第二個鎖存器)工作,其它的全置閑,對應的列電極是SEG0~SEG15;依次類推,直到列數控制鎖存器64位寄存器全部工作,對應的列電極是SEG0~SEG63.

電極驅動模塊

該模塊主要含有四個子模塊:行掃描電極驅動子模塊、列信號電極驅動子模塊、電平轉換器和可預置數環形計數器。

電平轉換器的作用是根據實際應用的需要,通過外加的控制信號將邏輯信號的電壓轉換為實際的LCD驅動電壓,并輸出到驅動模塊;行掃描電極驅動子模塊的作用是給行電極提供一定周期的掃描信號脈沖;列信號電極驅動子模塊的作用是把來自鎖存器的數據施加到相應的列電極,與行電極的掃描信號來建立交流驅動電場,從而驅動LCD器件的顯示。可預置數環形計數器可以通過行數控制端N(S0~S5)來控制行掃描電極數,以適應不同規模的LCD屏,根據實際的需要通過向行數控制端N輸入不同的數值,來控制具體工作的行數,其它的電極全部置閑。在行驅動時鐘信號控制下,逐行掃描,循環往復,直到行數控制端N輸入新的數值,再在新數目的行電極進行循環逐行掃描。例如,當外加信號N為“011011”時,掃描電極的數目為27,行掃描驅動子模塊在行電極COM0~COM26上產生逐行掃描信號,其它行電極COM27~COM63全部都置為低電平,循環往復,若施加了新的外加信號N為“100011”,掃描電極驅動子模塊就在行電極COM0~COM34上產生循環的逐行掃描信號。

IP核系統實現

首先,根據上面對整個系統功能定義和劃分及對各個模塊的設計,對各功能模塊分別用VHDL語言進行建模;其次,在Xilinx公司的FPGA器件上,用其EDA工具ISE進行仿真和綜合調試,并優化設計;然后,用VHDL定義頂層模塊將各模塊連接起來,并進行相應的系統調試和驗證;最后,得到一個LCD的驅動電路,具有64個COM(行)和64個SEG(列) 輸出,有高速的8位并行MCU接口及串行接口,芯片內含有存儲顯示數據的RAM,并且可以通過級聯控制端CS來進行級聯擴展以滿足較大的LCD,通過列數控制端M和行數控制端N來適應不同規模的LCD.

仿真和驗證

本文利用Xilinx公司的仿真軟件ISE作為仿真工具,分兩步對所設計的IP核進行了驗證。

首先,本文先對IP核的各個模塊(包括內部的子模塊)進行了初步的功能驗證。然后,參照芯片的工作過程,對整個芯片進行了整體仿真。圖3和圖4是利用ISE對整個IP核的行和列控制功能進行仿真而得到的仿真結果。圖中CLK和CLK1分別是MCU接口模塊的數據傳輸控制時鐘和行電極掃描脈沖;M和N分別為列電極與行電極數目選擇控制端; CS的低兩位和高兩位分別為行級聯與列級聯控制端。

圖3和圖4的仿真結果說明:

1. 當RESET為高電平時,IP核處于初態或清零態;當WRITE為高電平時,IP核處于工作態,可以接收顯示數據。

2. 在時鐘CLK的上升沿,MCU通過接口向IP核的RAM并行寫入8位顯示數據;在時鐘CLK1的上升沿,行掃描驅動電極依次輸出掃描脈沖,列信號電極會把RAM里的數據從SEG上輸出。

3. 行數控制端可以改變行掃描的電極數目。當行數選擇控制端N為“3E”時,在COM0~COM61輸出掃描信號。如圖3所示,在第1個行時鐘信號時,電極COM61上輸出掃描信號,在行驅動時鐘控制下,逐行遞減對行電極進行掃描;第7個行時鐘信號時,N變為“22”,掃描信號變成在行電極COM33上輸出,逐行遞減對COM0~COM33進行逐行掃描。

4. 列數控制端可以改變列信號的電極數目。當列數選擇控制端M為“110”時,SEG電極為48位輸出;當M為“010”時,SEG的輸出變為16位;當M為“101”,SEG的輸出變為40位;當M為“100”,SEG的輸出變為32位。

本文對該IP核的列數控制、行數控制、核間級聯等功能分別進行了功能驗證,并都通過了驗證。此處限于篇幅只介紹了列數與行數控制功能。

結語

本文討論了一種LCD顯示驅動芯片IP核的設計,根據自頂向下的設計思想,將芯片進行了層次化功能劃分,并對芯片的整體功能進行了驗證。在芯片的功能驗證中,本文采用了VHDL硬件描述語言對電路的邏輯功能和時序關系進行了仿真驗證。該LCD顯示驅動器由于采用了參數化設計,具有很好的移植性,可方便地應用于便攜式儀器及PDA等有關產品的各種不同規模的平板顯示系統應用中。

電子發燒友App

電子發燒友App

評論