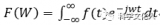

快速傅里葉變換 (Fast Fourier Transform,FFT), 即利用計(jì)算機(jī)計(jì)算離散傅里葉變換(DFT)的高效、快速計(jì)算方法的統(tǒng)稱,簡(jiǎn)稱FFT。

2023-07-20 16:46:23 2011

2011

大家好我有一些關(guān)于FFT IP CORE 9.0的配置通道的問題,在我的設(shè)計(jì)中,核心告訴我,我有一個(gè)16位數(shù)據(jù)寬的configuraiton tdata,但在實(shí)現(xiàn)細(xì)節(jié)中它說我只有11位配置,第一個(gè)

2020-05-11 09:20:03

`通過控制 variable streaming型FFT核進(jìn)行FFT變換,首先前16周期進(jìn)行1024點(diǎn)變換,然后跳轉(zhuǎn)進(jìn)行16點(diǎn)FFT,現(xiàn)在情況是,從FIFO 輸出的采樣數(shù)據(jù)正常輸入到FFT核,控制

2017-12-12 17:04:14

我正在使用FFT IP核9.0。我已經(jīng)定制了ip核心,具體如下數(shù)據(jù)格式:定點(diǎn),縮放選項(xiàng):縮放,舍入模式:截?cái)啵斎霐?shù)據(jù)寬度:16, 相位因子寬度:16,輸出訂購(gòu)選項(xiàng):自然訂單輸入

2020-05-12 08:32:53

在仿真fft ip核時(shí) 輸出信號(hào)一直為0,檢查了輸入波形,應(yīng)該沒有問題,大家?guī)兔纯窗奢斎胧怯蓃om里面的mif文件產(chǎn)生的信號(hào)。

2017-11-21 10:44:53

我用quartus II調(diào)用modelsim仿真fft ip核,仿真結(jié)束后我想驗(yàn)證下數(shù)據(jù)是否正確,結(jié)果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結(jié)果txt文件與用

2012-09-20 12:48:37

親愛的大家我已經(jīng)通過fft核心v9.0的數(shù)據(jù)表。我想實(shí)現(xiàn)FFT核心,但我沒有在頂層模塊(VHDL)中找到任何FFT核心的例子。如果有人建議我提供一些文檔或示例,我將感激不盡。這是我第一次嘗試在整個(gè)項(xiàng)目中使用xilinx IP核(頂層模塊)最好的祝福

2020-05-21 08:19:53

我想問一下,在quartus上直接調(diào)用IP核和在qsys中用IP核有什么區(qū)別?自個(gè)有點(diǎn)迷糊了

2017-08-07 10:09:03

我調(diào)用了一個(gè)ip核 在下載到芯片中 有一個(gè)time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個(gè)解決方法就是把ip核生成的v文件加到主項(xiàng)目文件中就是上面

2016-05-17 10:28:47

請(qǐng)教:ARM多核處理器中不同的核是否可配置為純REE環(huán)境和(REE+TEE)或純TEE環(huán)境?實(shí)現(xiàn)“不同CPU核的REE與TEE同時(shí)并行運(yùn)行,并相互通信”?(手機(jī)上是否就這樣做的?)謝謝。

2022-09-05 15:55:30

控制機(jī)制對(duì)當(dāng)前變長(zhǎng)分組骨干網(wǎng)的流量控制還是具有重要的參考價(jià)值,所以有必要對(duì)ATM的流量控制及其實(shí)現(xiàn)方式進(jìn)行深入的研究。 IP核是一段具有特定電路功能的硬件描述語言代碼,該程序與集成電路工藝無關(guān),因而

2011-09-27 11:54:25

用Quartus II 調(diào)用IP核時(shí),在哪可以查看IP核的例程

2014-07-27 20:28:04

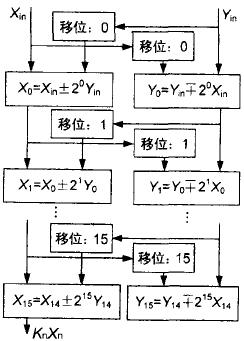

結(jié)果樣點(diǎn)(對(duì)應(yīng)于輸入數(shù)據(jù)塊)輸出之間的時(shí)幀(Time )。轉(zhuǎn)換時(shí)間不包括輸出所有轉(zhuǎn)換輸出數(shù)據(jù)塊的時(shí)間。(4)同表8.3(4)。二.FFT兆核函數(shù)的應(yīng)用1系統(tǒng)要求本節(jié)講述的應(yīng)用需要下列硬件和軟件配置

2012-08-13 14:34:06

有某試驗(yàn)數(shù)據(jù),用matlab求fft之后再求得的功率譜密度是這樣的:圖1但是用fft ip核,取前4096個(gè)數(shù)據(jù),得到fft之后的結(jié)果是這樣的:圖2求功率譜密度得到的是這樣的:圖3試驗(yàn)數(shù)據(jù)都是零點(diǎn)幾

2016-04-21 20:36:18

Gowin FFT IP用戶指南主要包括功能簡(jiǎn)介、信號(hào)定義、參數(shù)介紹、工作原理、GUI 調(diào)用等,旨在幫助用戶快速了解高云半導(dǎo)體 Gowin FFT IP 的特性及使用方法。

2022-10-08 08:11:09

最近在做FFT IP核,,走了好多彎路,LISENCE激活過了0034的IP核,通過修改LISENCE.DAT的方法。后來生成FFT的時(shí)候卡住,又嘗試了關(guān)閉quartus_map進(jìn)程和重裝jre

2019-04-03 16:16:21

USB_OTG_IP核中AMBA接口的設(shè)計(jì)與FPGA實(shí)現(xiàn)

2012-08-06 11:40:55

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實(shí)現(xiàn)高清圖像轉(zhuǎn)標(biāo)清圖像(具體就是1080p50轉(zhuǎn)576i30

2015-04-13 14:12:18

發(fā)生IP核鎖定,一般是Vivado版本不同導(dǎo)致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態(tài)報(bào)告 Report -》 Report IP Status 2)點(diǎn)擊

2021-01-08 17:12:52

一.Xilinx FFT IP介紹

1.總體特性

?FFT IP核支持復(fù)數(shù)的正逆傅里葉變換,可以實(shí)時(shí)配置變換的長(zhǎng)度

?變換的長(zhǎng)度N=2 ^m^ ,m=3-16,即支持的點(diǎn)數(shù)范圍為8-65536

2023-06-19 18:34:22

alter FFT ip核控制程序(verlog),輸出為幅值,可以直接觀察幅頻特性

2013-07-02 21:55:03

使用altera的FFTIP核的可變流結(jié)構(gòu)進(jìn)行FFT時(shí),輸出為什么跟實(shí)際情況是倍數(shù)關(guān)系

2016-09-20 19:18:10

ise FFT ip核的datasheet文檔打不開什么原因

2015-08-27 14:46:45

qsys設(shè)計(jì) avalon-mm 的硬IP核中斷是怎么實(shí)現(xiàn)的? 其中那個(gè)地址轉(zhuǎn)換表是有什么作用?

2020-10-28 13:59:22

,生成了NCO!在進(jìn)度條卡住時(shí),打開任務(wù)管理器,關(guān)閉quartus_map.exe*32進(jìn)程,成功生成IP核。(FFT核也適用)該IP核沒有生成*.bsf文件,不能用于原理圖輸入。可以使用Verilog編寫。具體為什么有哪位大神可以解答一下嗎???

2017-05-02 21:39:22

在quartusII中,應(yīng)用fft ip核時(shí),variable streaming 模式下的bit-reverse(位翻轉(zhuǎn))是什么意思?煩勞詳細(xì)幫助新手解釋一下,不甚感激

2017-01-09 10:55:59

數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開發(fā)速度。使用Verilog調(diào)用IP

2018-05-15 12:05:13

運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開發(fā)速度。今天介紹的是vivado的三種常用IP核:...

2021-07-29 06:07:16

用的xilinx的FFT 9.1版本的ip核 , 仿真出來的結(jié)果和我MATLAB算出來的結(jié)果差的很多,也沒有倍數(shù)關(guān)系,scaled因數(shù)改了好幾次,沒有溢出,波形大致相同,但是數(shù)值上差的太多,已經(jīng)弄了快兩周了,求做過這個(gè)的講講經(jīng)驗(yàn)。

2018-07-10 16:16:31

有沒有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學(xué)習(xí)FFT的IP核的使用,但是仿真結(jié)果有問題,所以想找些參考設(shè)計(jì),謝謝

2016-12-25 17:05:38

效。2.IP設(shè)置 以配置一個(gè)可更改變換點(diǎn)數(shù)的FFT IP 核為目標(biāo),具體說明各個(gè)部分。創(chuàng)建工程、添加IP核,并進(jìn)行IP核的設(shè)置。 第一個(gè)選項(xiàng)是同時(shí)進(jìn)行幾路數(shù)據(jù)流并行。第二個(gè)選項(xiàng)是變換的實(shí)際點(diǎn)數(shù),需要

2020-02-16 07:36:28

有效時(shí),才可以讀取RAM中的數(shù)據(jù)。還記得這里的 q’ output port么,這里選擇上了,也可以去掉。配置好后,點(diǎn)擊“Finish”,勾選擇RAM_inst.v。之后,在頂層模塊中實(shí)現(xiàn)RAM IP核

2016-10-01 11:07:42

摘要針對(duì)FFT算法基于FPGA實(shí)現(xiàn)可配置的IP核。采用基于流水線結(jié)構(gòu)和快速并行算法實(shí)現(xiàn)了蝶形運(yùn)算和4k點(diǎn)FFT的輸入點(diǎn)數(shù)、數(shù)據(jù)位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

剛剛接觸IP核做FFT,現(xiàn)在用的是FFTV9.0,已經(jīng)建立了一個(gè)IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應(yīng)該怎樣呢,謝謝指點(diǎn)。

2011-04-21 10:22:31

本帖最后由 Laputa_fly 于 2013-11-23 13:46 編輯

用quartus9.0調(diào)用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有結(jié)果。但是按照官方的使用說明用matlab仿真時(shí)出現(xiàn)問題。請(qǐng)大家?guī)兔鉀Q一下。謝謝!

2013-11-23 13:43:41

通過例化調(diào)用Xilinx IP核來實(shí)現(xiàn)一個(gè)512點(diǎn)、數(shù)據(jù)位寬和相位因子位寬都為10 bit的FFT算法模塊,時(shí)鐘頻率為 50MHz,采用流水線,Streaming I/O和定點(diǎn)壓縮結(jié)構(gòu)。為了方便驗(yàn)證

2016-12-27 14:12:20

在quartus II13.0版本上調(diào)用FFT IP核并進(jìn)行modelsim-altera仿真,在生成IP核時(shí),step2中勾選generate simulation model、generate

2016-10-07 22:23:33

。lirqn為中斷輸入信號(hào)。可以通過PCI編譯器IP工具臺(tái)或編輯兆核函數(shù)頭文件的方式修改PCI配置空間信息,本系統(tǒng)GCI兆核函數(shù)的配置信息如下: 3 本地總線讀寫狀態(tài)機(jī) 在用戶邏輯中,通過總線讀寫狀態(tài)機(jī)實(shí)現(xiàn)

2018-12-04 10:35:21

信號(hào)和多線程擴(kuò)展信號(hào)。所有IP核都需要基本數(shù)據(jù)信號(hào)中的一組信號(hào),其他可選信號(hào)用于支持通信需要,實(shí)現(xiàn)可配置和可擴(kuò)展性。基本數(shù)據(jù)信號(hào)包括:Clk、MAddr、MCmd、MData、MDataValid

2019-06-11 05:00:07

Viterbi譯碼的基本過程,接著根據(jù)Viterbi譯碼器IP核的特點(diǎn),分別詳細(xì)介紹了并行結(jié)構(gòu)、混合結(jié)構(gòu)和基于混合結(jié)構(gòu)的增信刪余3種Viterbi譯碼器IP核的主要性能和使用方法,并通過應(yīng)用實(shí)例給出了譯碼器IP

2010-04-26 16:08:39

16bit,定點(diǎn)signed(1.15),即最高位符號(hào)位,15位小數(shù)。同時(shí),繪制出matlab中cos時(shí)域和頻域的波形如下。 3 Vivado中添加配置FFT IP核Vivado中,打開IP

2019-08-10 14:30:03

基于FPGA的IP核8051上實(shí)現(xiàn)TCPIP的設(shè)計(jì)

2012-08-06 12:18:28

硬件集成真正的即插即用,允許系統(tǒng)集成根據(jù)應(yīng)用需要選擇最好的IP核和互聯(lián)機(jī)制。OCP為IP核設(shè)計(jì)提供了解決可配置性和接口的較好辦法,實(shí)現(xiàn)了IP核與系統(tǒng)集成的Socket接口,能夠做到核的模塊化和即插即用特性。

2018-12-11 11:07:21

怎么才能在嵌入FPGA的IP核8051上實(shí)現(xiàn)TCP/IP的設(shè)計(jì)?

2021-04-29 06:51:27

我調(diào)用FFT這個(gè)IP核,可是運(yùn)行到最后那個(gè)“EDA Netlist Writer”的時(shí)候出現(xiàn)這樣的錯(cuò)誤,Error: Can't generate netlist output files

2013-08-26 15:33:24

我的quartus ii 版本13.1fft核版本13.1 modelsim版本64位 10.4在quartus ii 中使用rtl仿真時(shí)(已經(jīng)在quartus ii中編譯成功) 彈出

2019-02-26 16:21:08

的1個(gè)輸出LED指示燈閃爍。時(shí)鐘頻率CLK_FREQUENCY和LED閃爍頻率LED_FLASH_FREQUENCY都定義為參數(shù)(parameter),一會(huì)制作IP核的時(shí)候都可以配置為GUI供調(diào)用IP

2019-09-09 10:55:24

cos時(shí)域和頻域的波形如下。 3 Vivado中添加配置FFT IP核Vivado中,打開IP Catalog,搜索FFT或者找到分類Core àDigital Signal Processing

2020-01-07 09:33:53

fft仿真沒有輸出,初始值不正常,但上板驗(yàn)證沒問題,試過重新生成ip核沒有用,請(qǐng)教一下是什么問題。

2019-05-10 10:27:57

請(qǐng)問為什么生成FFT ip 核會(huì)卡在生成這一步,前兩天還好好的。求大神的解決辦法,網(wǎng)上實(shí)在找不到方法

2016-11-01 13:42:43

如題,調(diào)用altera公司的FFT IP核,用的是13.1版本,將modulsim仿真的結(jié)果輸入到matlab畫出頻譜圖,功能仿真結(jié)果沒有問題,但門級(jí)仿真中除了原頻率信息外,出現(xiàn)了很多不存在的頻率

2018-08-28 20:43:56

(Intellectual Property)核。IP核由相應(yīng)領(lǐng)域的專業(yè)人員設(shè)計(jì),并經(jīng)反復(fù)驗(yàn)證。IP核的擁有者可通過出售IP獲取利潤(rùn)。利用IP核,設(shè)計(jì)者只需做很少設(shè)計(jì)就可實(shí)現(xiàn)所需系統(tǒng)。基于IP核的模塊化設(shè)計(jì)可縮短

2019-07-29 08:33:45

本文簡(jiǎn)要介紹了SoC 設(shè)計(jì)鏈面臨的挑戰(zhàn)以及對(duì)可配置IP 提出的新的要求。重點(diǎn)分析了如何利用Improv 系統(tǒng)公司開發(fā)的VLIW架構(gòu)和包括Jazz DSP 平臺(tái)的工具套件進(jìn)行快速、低成本、高性能的

2009-12-14 10:25:55 14

14 基于Avalon總線的可配置LCD 控制器IP核的設(shè)計(jì)

本文討論了基于Avalon 總線流傳輸?shù)?b class="flag-6" style="color: red">配置LCD 顯示控制器IP 核的設(shè)計(jì),根據(jù)自頂向下的設(shè)計(jì)思想,將IP 核進(jìn)行層次功能

2010-02-09 09:34:44 27

27 利用面向?qū)ο蠹夹g(shù)進(jìn)行可配置的FFT IP 設(shè)計(jì)與實(shí)現(xiàn)摘要:為了縮短產(chǎn)品上市時(shí)間并降低設(shè)計(jì)成本,IP 復(fù)用已經(jīng)成為IC設(shè)計(jì)的重要手段。以往利用RTL 代碼編寫的IP,往往是針對(duì)特定應(yīng)

2010-07-04 11:42:13 8

8 利用FFT IP Core實(shí)現(xiàn)FFT算法

摘要:結(jié)合工程實(shí)踐,介紹了一種利用FFT IP Core實(shí)現(xiàn)FFT的方法,設(shè)計(jì)能同時(shí)對(duì)兩路實(shí)數(shù)序列進(jìn)行256點(diǎn)FFT運(yùn)算,并對(duì)轉(zhuǎn)換結(jié)果進(jìn)行求

2008-01-16 10:04:58 6709

6709

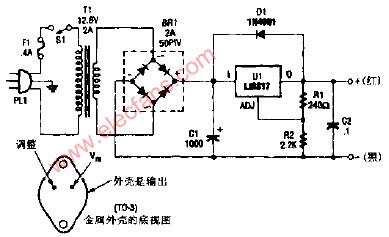

可配置電源

如果有必要的話,此可調(diào)

2009-09-30 12:07:59 703

703

可配置振蕩器,可配置振蕩器結(jié)構(gòu)原理是什么?

可配置振蕩器既具備可編程振蕩器交付時(shí)間短的優(yōu)勢(shì),又避免了其噪聲高的缺陷,其內(nèi)部結(jié)構(gòu)如圖2

2010-03-22 14:34:20 769

769 在論壇中經(jīng)常有人會(huì)問起 altera 軟件fft ip 中使用方法,有些人在使用這個(gè)fft ip core 的時(shí)候沒有得到正確的結(jié)果,事實(shí)上,這個(gè)ip core 還是比較容易使用的。有些人得不到正確的仿真結(jié)果

2011-05-10 15:19:24 0

0 在現(xiàn)代邏輯設(shè)計(jì)中,F(xiàn)PGA占有重要的地位,不僅因?yàn)榫哂袕?qiáng)大的邏輯功能和高速的處理速度,同時(shí)因?yàn)槠鋬?nèi)部嵌有大量的可配置的塊RAM,使其得到了廣泛地應(yīng)用,例如FFT算法的實(shí)現(xiàn)等。

2011-09-27 17:07:12 54

54 針對(duì)WIMAX系統(tǒng)中變長(zhǎng)子載波的特點(diǎn),通過采用流水線乒乓結(jié)構(gòu),以基2、基4混合基實(shí)現(xiàn)了高速可配置的FFT/IFFT。將不同點(diǎn)數(shù)的FFT旋轉(zhuǎn)因子統(tǒng)一存儲(chǔ),同時(shí)對(duì)RAM單元進(jìn)行優(yōu)化,節(jié)約了存儲(chǔ)空間;此外

2012-02-29 11:29:06 5

5 一種密鑰可配置的DES加密算法的FPGA實(shí)現(xiàn)

2016-05-11 11:30:19 11

11 FFT變換的IP核的源代碼,有需要的下來看看。

2016-05-24 09:45:40 18

18 利用FPGA的IP核設(shè)計(jì)和實(shí)現(xiàn)FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源碼:FFT變換的IP核的源代碼

2016-06-07 11:44:14 9

9 Xilinx FPGA工程例子源碼:Xilinx 的IP:1024點(diǎn)FFT快速傅立葉變換

2016-06-07 15:07:45 51

51 由于OFDM接收機(jī)中大多是數(shù)據(jù)串并轉(zhuǎn)換后的連續(xù)低速并行數(shù)據(jù)流輸入FFT,故這里采用流水線結(jié)構(gòu)。之后根據(jù)OFDM子載波數(shù)選擇變換長(zhǎng)度。該IP核僅支持50MHZ采樣率數(shù)據(jù)的流水線處理,如果數(shù)高速通信場(chǎng)合,可以再次將數(shù)據(jù)串并轉(zhuǎn)換用多個(gè)FFT IP核并行運(yùn)算,也就是FPGA設(shè)計(jì)中常用的“面積換速度”。

2018-06-26 10:08:00 1754

1754

數(shù)字信號(hào)處理領(lǐng)域中FFT算法有著廣泛的應(yīng)用。目前現(xiàn)有的文獻(xiàn)大多致力于研究利用FFT算法做有關(guān)信號(hào)處理、參數(shù)估計(jì)、F+FT蝶形運(yùn)算單元與地址單元設(shè)計(jì)、不同算法的FFT實(shí)現(xiàn)以及FFT模型優(yōu)化等方面。

2019-01-07 09:33:00 8932

8932

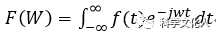

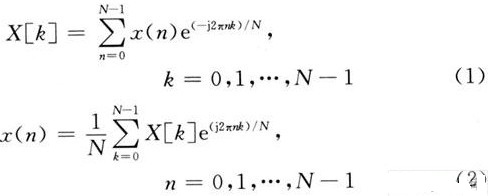

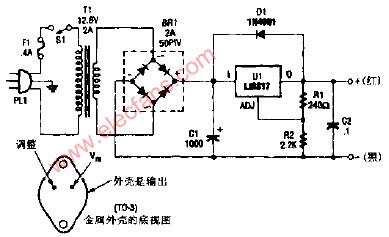

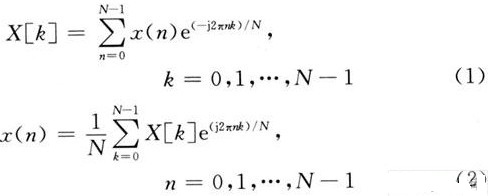

01 FFT簡(jiǎn)介 快速傅里葉變換 (Fast Fourier Transform,FFT), 即利用計(jì)算機(jī)計(jì)算離散傅里葉變換(DFT)的高效、快速計(jì)算方法的統(tǒng)稱,簡(jiǎn)稱FFT。DFT是實(shí)現(xiàn)了從頻域

2021-07-23 14:29:36 5238

5238

Xilinx快速傅立葉變換(FFT IP)內(nèi)核實(shí)現(xiàn)了Cooley-Tukey FFT算法,這是一種計(jì)算有效的方法,用于計(jì)算離散傅立葉變換(DFT)。

2022-03-30 11:01:31 2358

2358 賽靈思 Fast Fourier Transform (FFT) IP 具有專用于處理 FFT 輸出中的位增長(zhǎng)的縮放因子。本文旨在提供有關(guān)此 IP 中可用縮放方法的見解,并提供縮放調(diào)度選擇方法以避免出現(xiàn)文中所述的溢出問題。

2022-07-20 11:17:24 3572

3572 以Xilinx Vivado設(shè)計(jì)套件中提供的FFT IP為例,簡(jiǎn)要說明如何進(jìn)行FFT IP配置和設(shè)計(jì)。

2022-07-22 10:21:27 1755

1755 Gowin FFT IP 用戶指南主要包括功能簡(jiǎn)介、信號(hào)定義、參數(shù)介紹、工作

原理、GUI 調(diào)用等,旨在幫助用戶快速了解高云半導(dǎo)體 Gowin FFT IP 的特

性及使用方法。

2022-09-15 10:19:24 0

0 筆者在校的科研任務(wù),需要用FPGA搭建OFDM通信系統(tǒng),而OFDM的核心即是IFFT和FFT運(yùn)算,因此本文通過Xilinx FFT IP核的使用總結(jié)給大家開個(gè)頭,詳細(xì)內(nèi)容可查看官方文檔PG109。

2023-07-10 10:43:18 632

632

)hls_fft.h。實(shí)際上,在HLS中調(diào)用該庫實(shí)現(xiàn)FFT,其實(shí)是Vivado中的那個(gè)FFT核實(shí)現(xiàn)的,但是HLS中的配置和給定輸入輸出數(shù)據(jù)比較方便,并且對(duì)其外部封裝其他類型的總線接口非常容易。

2023-07-11 10:05:35 580

580

電子發(fā)燒友網(wǎng)站提供《在AI引擎上實(shí)現(xiàn)逐塊可配置的快速傅里葉變換應(yīng)用說明.pdf》資料免費(fèi)下載

2023-09-13 11:48:43 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論