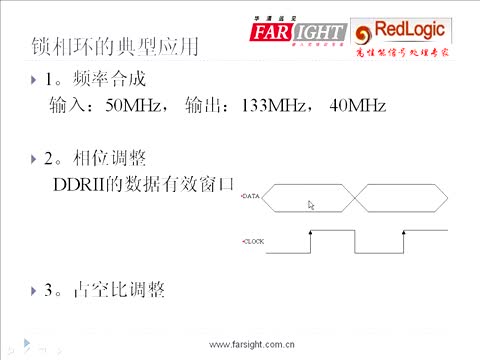

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

的提升。同時也給運算增加了難度,對并行化運算、靈活化運算提出了更高的運算。三、FPGA H.265IP核簡介1.性能摘要2.特點?H.265幀速率:1fps-60fps?支持雙流輸出?支持投資回報率

2019-03-08 10:47:22

的基礎上,給出了一種仿真調試方 案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結構分析OpenCores網站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051單片機 IP核編程,編寫的c語言矩陣鍵盤程序可以在stc89c54單片機上正常工作,但是下載到FPGA中8051單片機ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

的FPGA中都集成了專用乘法器;為了適用通信總線與接口標準,很多高端的FPGA內部都集成了串并收發器(SERDES),可以達到數十Gbps的收發速度。Xilinx公司的高端產品不僅集成了Power PC

2023-05-30 20:53:24

本帖最后由 jf_25420317 于 2023-11-17 11:10 編輯

FPGA開發過程中,利用各種IP核,可以快速完成功能開發,不需要花費大量時間重復造輪子。

當我們面對使用新IP核

2023-11-17 11:09:22

有誰知道現在國內外有哪些公司賣FPGA的圖像處理相關的IP核?

2015-04-28 21:34:24

是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC 階段,IP 核設計已成為ASIC 電路設計公司和FPGA

2018-09-03 11:03:27

求大神,FPGA內部的PCI的IP軟核實現PCI接口設計?

2013-05-02 16:12:21

`Xilinx FPGA入門連載34:超聲波測距終極結果顯示之除法器IP解析特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1概述在本例

2015-12-09 12:22:00

Xilinx FPGA入門連載43:FPGA片內ROM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-06 12:22:53

實例內部系統功能框圖如圖所示。我們通過IP核例化一個RAM,定時遍歷寫入其所有地址的數據,然后再遍歷讀出所有地址的數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內RAM

2016-01-20 12:28:28

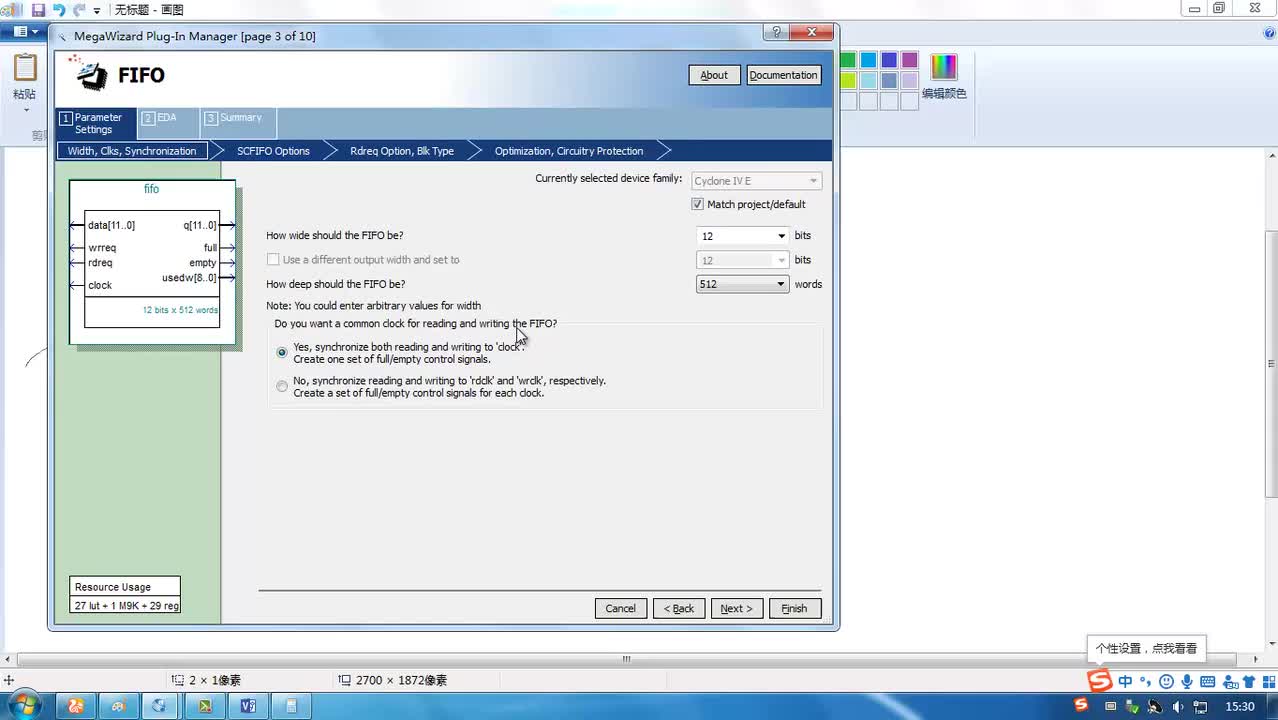

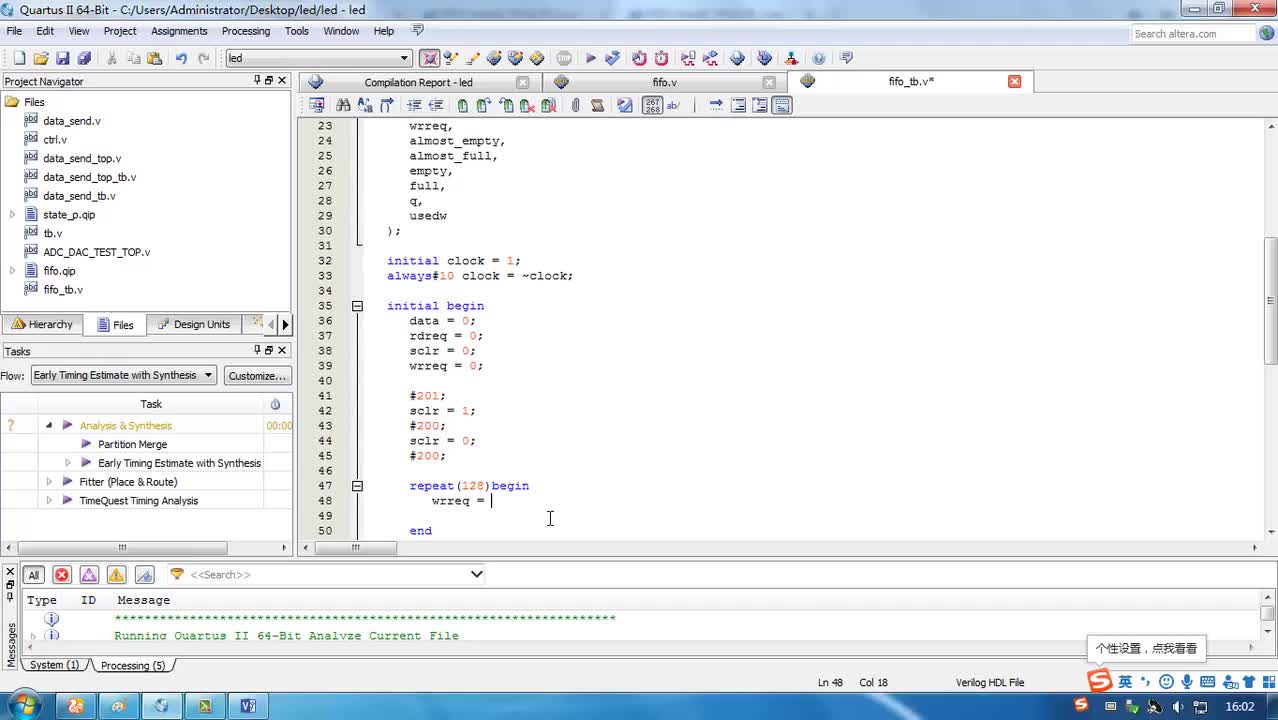

實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內FIFO的讀寫時序。 2 模塊

2016-02-26 10:26:05

`Xilinx FPGA入門連載55:FPGA 片內異步FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門連載59:FPGA 片內ROM FIFO RAM聯合實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:43:36

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

利用FPGA自帶的IP核實現雙口RAM用于2片MCU進行數據交換時多次讀數據后RAM中數據變為了0,是什么意思,打什么幫幫忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

出現網絡和數據存儲協議處理的瓶頸或延遲。VCK190 評估套件和 Design Gateway 的網絡和存儲 IP 解決方案可在 Xilinx 的 Versal AI Core 器件上以盡可能低的 FPGA 資源使用量和極高的能效在 AI 應用中實現最佳性能。

2022-11-25 16:29:20

可以移植到不同的半導體工藝中去生產集成電路芯片。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個趨勢。 本文研究了ATM流量控制的原理,并給出了一種IP核的實現方法,該IP核不僅可以用于獨立芯片,還可以作為系統的一個子模塊直接調用。

2011-09-27 11:54:25

Altera系列FPGA芯片IP核詳解

2020-06-28 13:51:01

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個輸入。我參考網上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個值X、Y合并成一個(X、Y均為定點數)。具體情況如下圖:

2019-09-10 20:07:07

與FPGA架構相集成,可以實現更大的設計靈活性和更快的上市時間。美高森美為電機控制算法開發提供了具有多個多軸電機控制參考設計和IP的生態系統,使由多處理器解決方案轉向單一器件解決方案(即SoC FPGA)更加容易。

2019-06-24 07:29:33

實現,于是2001年Altera第一次提出了可編程片上系統(SOPC)概念,并且推出了第一款嵌入式處理器軟核Nios以及之后的第二代Nios II以及相應的開發環境,此后Xilinx也推出

2020-03-09 06:50:07

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

`本視頻是Combat FPGA開發板的配套視頻課程,本章節課程主要介紹如何利用Gowin FPGA實現MAC協議開發。內容包括MAC協議概述,MAC幀結構,以及Gowin以太網Mac IP使用簡介

2021-05-06 15:08:59

技術10.4.2 基于FPGA的千兆以太網MAC控制器實現方案10.4.3 Xilinx 千兆以太網MAC IP Core10.5 本章小結第11章時序分析原理以及時序分析器的使用11.1 時序分析的作用

2012-04-24 09:23:33

附件為使用FPGA實現兩路CAN接口進行回環通信的工程文件。包含詳細的工程使用說明文檔。在小梅哥的Starter FPGA開發板上驗證通過,CAN通信使用開源的OC_CAN IP和VP230收發器實現,上層應用使用NIOS II實現,使用非常方便。

2017-09-22 22:42:14

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

。FPGA具有并行運算、反復使用、大量可使用的軟核的優勢,是實現機器視覺理想構架的合理選擇。FPGA是小批量系統提高集成度、可靠性的最佳選擇之一。隨著VLSI工藝的不斷提高,單一芯片內部已可以容納上百萬個

2019-05-05 08:30:00

各位前輩好!我在用Xilinx Virtex5 FPGA做通過千兆網和上位機通信,有幾個問題想請教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

基于FPGA的嵌入式系統的開發工具包。本文介紹基于SoPC的波形發生器在EDK工具包下的設計與實現。本設計采用嵌入式軟處理器核 MicroBlaze以及自主編寫的包括實現DDS在內的多種IP Core

2009-06-25 08:12:37

基于FPGA的IP核8051上實現TCPIP的設計

2012-08-06 12:18:28

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

基于FPGA的FFT和IFFT IP核應用實例AT7_Xilinx開發板(USB3.0+LVDS)資料共享騰訊鏈接:https://share.weiyun.com/5GQyKKc百度網盤鏈接

2019-08-10 14:30:03

在通信、圖像處理、模式識別等領域都有著廣泛的應用。Vivado集成的FIR IP核可以實現如下公式所示的N級卷積運算。 FIR IP核可以根據配置實現復用的乘累加單元,以實現面積最優化的設計;當然了

2019-07-16 17:24:22

最小硬件系統設計原理圖;2)10/100 Ethernet MAC IP源代碼和驅動;3)集成10/100 Ethernet MAC在內的Nios處理器片上系統架構設計實例,以及該系統下經過嚴格測試

2014-06-19 12:04:25

最小硬件系統設計原理圖;2)10/100 Ethernet MAC IP源代碼和驅動;3)集成10/100 Ethernet MAC在內的Nios處理器片上系統架構設計實例,以及該系統下經過嚴格測試

2014-06-19 12:06:43

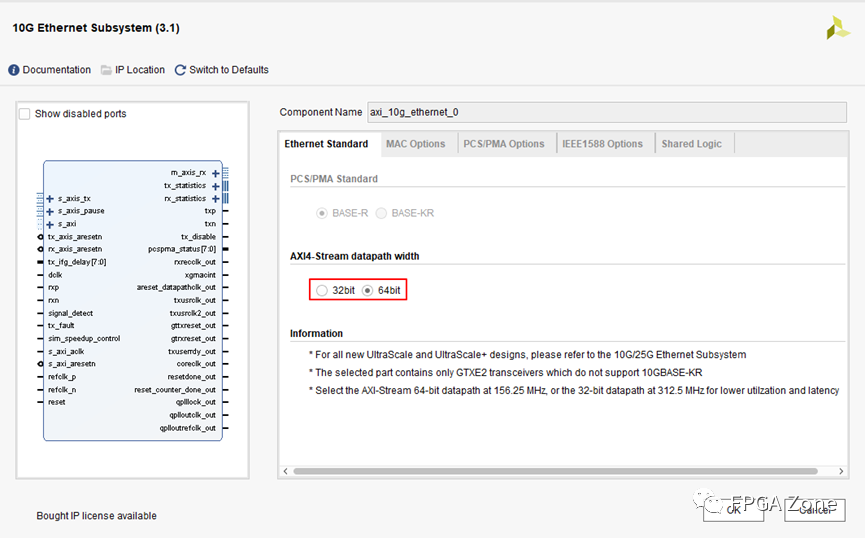

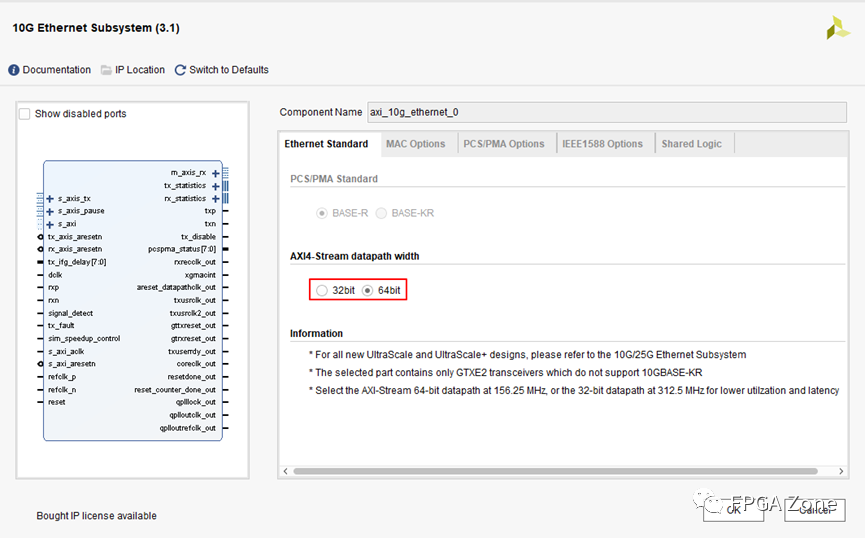

Ethernet PCS/PMA IP核本案例使用10G Ethernet PCS/PMA IP核實現物理層(PCS與PMA)功能。10G Ethernet PCS/PMA IP核開發文檔為產品資料“6-開發

2021-01-21 19:24:54

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

。FPGA具有并行運算、反復使用、大量可使用的軟核的優勢,是實現機器視覺理想構架的合理選擇。 FPGA是小批量系統提高集成度、可靠性的最佳選擇之一。隨著VLSI工藝的不斷提高,單一芯片內部已可以容納

2013-09-04 12:14:55

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

實現的RTL級設計,與具體實現工藝無關,相比于固核和硬核具有較大的靈活性,在FPGA中定制PCI接口軟核實現PCI接口控制具有明顯的優勢:可以在單片FPGA中同時完成PCI接口和用戶邏輯的設計,縮減成

2018-12-04 10:35:21

引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口標準

2019-06-11 05:00:07

【摘要】:Viterbi譯碼器在通信系統中應用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

內容簡介本書基于XILINX的嵌入式開發平臺,講解了嵌入式系統的基本概念、FPGA和MicroBlaze處理器以及最新的多端口內存控制器(MPMC)的原理。[1]通過不同的總線和接口實驗,詳細講述了

2017-12-08 14:27:35

入RAM。本實驗將為大家介紹如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作。1.實驗原理Xilinx在VIVADO里為我們已經提供了ROM的IP核, 我們只需通過IP核例化一個ROM,根據

2021-01-07 15:48:39

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

(IntellectualProperty)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短設計周期,提高設計質量。現場

2019-09-03 07:44:22

本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

怎么才能在嵌入FPGA的IP核8051上實現TCP/IP的設計?

2021-04-29 06:51:27

深圳明德揚科技教育有限公司,是一家高科技民營公司,主營業務為IC/FPGA設計、開發、培訓。旗下包括廣州健飛集成電路設計有限公司(辦公設在廣州市南沙自貿區)、龍核集成電路IP核交易平臺。明德揚

2018-06-02 17:35:40

在學校做畢業設計,被老板要求在Xilinx的FPGA上完成SATA的操作,急需SATA的HOST與DEVICE的IP核。由于可以使用部分項目經費,所以重金求購SATA IP核。在網上查了一下,有

2014-02-07 10:34:53

Xilinx系列FPGA芯片IP核詳解 ,altera系列FPGA芯片IP核詳解 , 相關資料 謝謝!!萬分感謝!!!!!

2015-06-03 15:03:34

采用xilinx EDK的GPIO IP核實現中斷的功能(里面很詳細的)

2012-08-17 10:02:52

(Intellectual Property)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短

2019-07-29 08:33:45

通過將第三方IP集成到NI LABVIEW軟件中,您可以使用許多為XILINX現場可編程門陣列(FPGA)精調過的算法實現高性能,并且提高代碼重用度。LABVIEW FPGA模塊為導入外部IP提供了兩個方法:組件級知識產權(CLIP)節點和結合XILINX核心生成器的IP集成節點。本技

2011-03-15 13:25:58 90

90 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源碼:Xilinx TCP_IP協議實現

2016-06-07 14:54:57 31

31 研究了TCP/IP通信協議棧在Xilinx 公司現場可編程門陣列FPGA上的實現,介紹了其軟硬件的系統組成

和原理,提出一種不需操作系統的TCP/IP協議棧的高效工作模式,并在

2017-09-04 09:24:59 9

9 研究了嵌入式TCP/IP通信協議棧在Xilinx FPGA上的實現,介紹了其軟硬件的系統組成和原理,提出一種實時操作系統上TCP/IP協議棧的高效工作模式,并在Virtex5 FPGA上移植成功。通過建立測試平臺進行數據傳輸測試,證明其具有穩定、高效的通信性能,為嵌入式設備開發提供了新的思路。

2017-11-17 17:05:01 7251

7251

。 使用Xilinx內核生成器IP函數實現FPGA VI中不同的Xilinx內核生成器IP。LabVIEW使用IP集成節點實現上述函數。函數名稱和說明來自于Xilinx數據表。單擊Xilinx內核生成器配置對話框的數據表按鈕,了解IP內核的詳細信息。 選板隨終端變化且僅顯示FPGA設備系列支持的IP。

2017-11-18 05:54:05 1286

1286 本頁包含通過LabVIEW FPGA模塊可用的Xilinx CORE生成器IP的列表。LabVIEW通過Xilinx IP節點實現該IP。 下列IP名稱和說明來自于Xilinx數據表。LabVIEW

2017-11-18 05:55:51 4465

4465 LabVIEW使用IP集成節點方便的整合Xilinx內核生成IP至FPGA VI。按照下列步驟添加Xilinx內核生成器IP至FPGA VI。 1、在支持的FPGA終端下新建一個空白VI,并顯示VI

2017-11-18 05:56:22 1746

1746 資源。為簡化設計,降低硬件資源開銷,可以在FPGA中利用IP核實現的嵌入式微處理器來對串口數據進行處理。

2019-08-02 08:08:00 3816

3816 ? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 本文接續上一篇《FPGA雜記基礎篇》,繼續為大家分享IP例化和幾個基于FPGA芯片實現的Demo工程。IP例化IP即是一個封裝好的模塊,集成在相應的開發環境里面,以安路的TD軟件為例,不同系列的芯片集成了不同的IP模塊,可以通過軟件例化調用

2020-12-24 12:58:51 1048

1048 基于FPGA的TCP/IP協議的實現說明。

2021-04-28 11:19:47 49

49 ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 12

12 筆者在校的科研任務,需要用FPGA搭建OFDM通信系統,而OFDM的核心即是IFFT和FFT運算,因此本文通過Xilinx FFT IP核的使用總結給大家開個頭,詳細內容可查看官方文檔PG109。

2023-07-10 10:43:18 632

632

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 2357

2357

本文開源一個FPGA項目:UDP萬兆光通信。該項目實現了萬兆光纖以太網數據回環傳輸功能。Vivado工程代碼結構和之前開源的《UDP RGMII千兆以太網》類似,只不過萬兆以太網是調用了Xilinx

2023-09-01 16:25:13 742

742

上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數據位寬是寫數據位寬兩倍的FIFO,然后使用讀時鐘頻率:寫時鐘頻率=2:3,進行簡單的FIFO跨時鐘域操作。

2023-09-07 18:31:35 759

759

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

電子發燒友App

電子發燒友App

評論