PLD和FPGA有什么區別與聯系?

PLD(Programmable Logic Device)是可編程邏輯器件的總稱。早期的PLD多屬于EEPROM或乘積項(Product Term)結構。FPGA(Field Programmable Gate Arry)是指在線可編程邏輯陣列,最早為Xilinx公司推出。多為SRAM框架或查表框架,需外接配置用的EPROM下載。Xilinx將SRAM框架或查表框架,需外接配置用的EPROM下載的PLD稱之為FPGA。把Flash、EEPROM框架或乘積項框架的PLD稱為CPLD。 Altera把自己的PLD產品MAX系列/FLEX/ACEX/APEX系列稱為CPLD。由于FLEX/ACEX/APEX系列也是SRAM型,需外接配置用的EPROM下載,很多人把Altera的FLEX/ACEX/APEX系列產品也稱為FPGA。

PLD高速通訊USB轉移技術分析

可編程邏輯器件(PLD)是20世紀70年代在ASIC設計的基礎上發展起來的一種劃時代的新型邏輯器件。自PLD器件問世以來,制造工藝上采用TTL、CMOS、ECL及靜態RAM技術,器件類型有PROM、EPROM、 E2PROM、FPLA、PAL、GAL、PML及LCA等。PLD在性能和規模上的發展,主要依賴于制造工藝的不斷改進,高密度PLD是VLSI集成工藝高度發展的產物。80年代末,美國ALTERA和XILINX公司采用EECMOS工藝,分別推出大規模和超大規模的復雜可編程邏輯器件(CPLD)和現場可編程邏輯門陣列器件(FPGA)。這種芯片在達到高集成度的同時,所具有的應用靈活性和多組態功能是以往的LSI/VLSI電路無法比擬的。自從跨入90年代以來,可編程邏輯器件CPLD/FPGA得到了飛速發展,向高集成度、高速度和低價位方向不斷邁進;不僅具有電擦除特性,而且出現了邊緣掃描及在線編程等高級特性;其應用領域不斷擴大,可用于狀態機、同步、譯碼、解碼、計數、總線接口、串并轉換等很多方面,而且在信號處理領域的應用也活躍起來。使用CPLD可以提高系統集成度、降低噪聲、增強系統可靠性并降低成本。

本文主要介紹ATMEL公司的CPLD芯片ATF1508AS的特點及應用。ATF1508AS是利用ATMEL成熟的電擦除技術實現的高性能、高密度的復雜可編程邏輯器件(CPLD),與ALTERA公司的EPM7000系列引腳完全兼容;可以將EPM7000的POF文件轉換為適合ATF1508AS的工業標準JEDEC編程文件,下載到ATF1508AS芯片中。

1 ATF1508AS的特點

ATF1508AS是利用ATMEL成熟的電擦除技術實現的高性能、高密度的復雜可編程邏輯器件(CPLD)。它有128個邏輯宏單元和最大100個輸入,能很容易地集成一系列TTL、SSI、MSI、LSI和傳統PLD的邏輯功能。ATF1508AS的增強型路由開關矩陣增加了可用的門數和設計改變時引腳鎖定的成功率,這是非常重要的。ATF1508AS有96個雙向I/O引腳和4個輸入引腳。這4個輸入引腳也可以用于全局控制信號、全局寄存器時鐘、全局復位和全局輸出允許。

128個宏單元中的每一個都產生一個隱藏的反饋回路到全局總線,每一個輸入引腳、I/O引腳也都匯入全局總線。每個邏輯塊的開關矩陣從全局總線中選擇 40個獨立的信號,每一個宏單元也產生一個返送邏輯項到局部總線。宏單元之間的級聯邏輯可以快速有效地實現復雜的邏輯功能。ATF1508AS包括八個這樣的邏輯鏈,每一個都能通過扇入最多40個乘積項實現邏輯項求和。

ATF1508AS是在系統編程(ISP)器件。它用工業標準的4腳JTAG接口(IEEE標準1149.1),完全與 JTAG的邊界掃描描述語言(BSDL)兼容。ISP允許器件不用從印刷電路板上拿走就可編程;除簡化生產流程外,ISP也允許通過軟件進行設計修改。

ATF1508AS的引腳保持電路提供對所有輸入和I/O引腳的設置。當任何引腳驅動到高電平或低電平,緊接著引腳被懸空時,引腳將保持先前的高電平或低電平狀態。這種電路防止沒有用到的輸入和I/O線懸空而成為中間的電壓值,這會導致不必要的功耗和系統噪聲。引腳保持電路去除了對外部上拉電阻的需要和直流功耗。

ATF1508AS的加密特性可以保護ATF1508AS的設計內容。兩個字節(16位)的用戶信號可被用戶存取,能存放工程名、部件號、版本或日期等,而且用戶信號的存取不受加密熔絲的狀態影響。

ATF1508AS具有上電復位特性。在上電期間,所有的I/O引腳將為三態,直到VCC到達上電電壓,這樣可防止在上電期間發生總線競爭。ATF1508AS的寄存器設計成在上電時復位,從VCC上升到VRST后的微小的延時,所有的寄存器將復位到低電平,輸出狀態要根據緩沖器的極性設置。這種特性對于狀態機的初始化是比較關鍵的。

2 ATF1508AS的宏單元

ATF1508AS的宏單元如圖1所示。它的宏單元非常靈活,足以支持高復雜邏輯功能并且高速工作。宏單元包括五個部分:乘積項和乘積項選擇多路復用器、或/異或/級聯邏輯、觸發器、輸出選擇和使能、邏輯陣列輸入。沒有用到的宏單元可由編譯器禁止以降低功耗。

(1)乘積項和乘積項選擇矩陣

每一個宏單元有5個乘積項,每個乘積項作為它的輸入從全局總線和局部總線接收所有信號。乘積項選擇矩陣(PTMUX)按需分配這5個乘積項到宏單元的邏輯門,也負責分配控制信號。乘積項選擇矩陣的編程是由設計編譯器決定的,編譯器將選擇優化的宏單元配置。

(2)或/異或/級聯邏輯

ATF1508AS的邏輯結構是為有效地支持所有的邏輯而設計的。在一個宏單元內,所有的乘積項可以被布進或門,產生一個5輸入的與/或求和項。通過鄰近的宏單元扇入額外的乘積項,可以擴展到40個乘積項而只有很小的延時。宏單元的異或門允許有效地實現比較和算術功能,其中異或門的一個輸入來自或運算的求和項,另一個輸入可以是一個乘積項或一個固定的高電平或低電平。對于組合邏輯輸出,固定電平允許極性選擇;對于時序邏輯,固定電平允許利用反演規則(摩根定律的推論)化簡乘積項。異或門也可以用于仿真T型和JK型觸發器。

(3)觸發器

ATF1508AS的觸發器有非常靈活的數據和控制功能。觸發器的輸入可以來自于異或門、一個單獨的乘積項或直接由I/O口輸入。選擇單獨的乘積項允許在一個組合邏輯輸出宏單元內生成一個隱藏的寄存器反饋(這個特性是由fitter軟件自動實現的)。除D、T、JK和SR類型外,ATF1508AS的觸發器還可配置為鎖存器。在這種模式中,當時鐘為高時,數據通過;當時鐘為低時,數據鎖存。

時鐘信號可以是全局CLK信號(GCK)和一個單獨的乘積項。觸發器在時鐘的上升沿改變狀態。當GCK信號作為時鐘信號時,宏單元的一個乘積項可以選擇作為時鐘允許信號。當使用時鐘使能功能時,使能信號(乘積項)為低時,所有的時鐘邊沿將被忽略。觸發器的異步復位信號(AR)可以是全局復位信號(GCLEAR)、一個乘積項或不使用。AR也可以是GCLEAR和一個乘積項的邏輯或輸出。異步置位信號(AP)可以是一個乘積項或不使用。

(4)輸出選擇和使能

ATF1508AS宏單元的輸出可以選擇為寄存器型和組合型。隱藏的反饋信號可以是組合或寄存器信號而不管輸出是組合型還是寄存器型。輸出使能多路復用器(MOE)控制輸出使能信號。如果是簡單的輸出操作,任何緩沖器都可以永久使能。如果引腳用作輸入,緩沖器也可以永久禁止。在這種配置下,所有的宏單元資源仍然可用,包括隱藏的反饋信號、擴展器和級聯邏輯。每一個宏單元的輸出使能信號都可以選擇一個全局輸出使能信號。該器件有6 個全局輸出使能信號(OE)。

(5)邏輯陣列輸入

邏輯陣列輸入包括全局總線/開關矩陣和返送總線:

◇ 全局總線/開關矩陣

全局總線包括所有的輸入和I/O引腳信號以及所有128個宏單元的隱藏反饋信號。每個邏輯塊的開關矩陣將全局總線的所有信號作為其輸入。在軟件的控制下,這些信號中最多可以有40個被選擇作為邏輯塊的輸入。

◇ 返送總線

每一個宏單元可以產生一個返送乘積項。這個信號連接到局部總線上,并且對16個宏單元有效,它是宏單元一個乘積項的反極性。每個局部總線的16個返送項允許產生高扇入求和項(最多21個乘積項),而只有很小的延時。

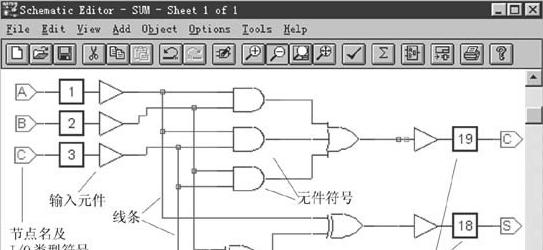

3 設計軟件支持

ATMEL公司提供了CPLD的設計軟件,而且很多第三方的工具軟件也支持ATF1508AS的設計,可以用多種高級描述語言和格式進行邏輯描述,如CUPL、ABEL、VHDL等。由于ATF1508AS與ALTERA公司的EPM7000系列是完全引腳兼容的,因此可以使用 ALTERA公司的MAXPLUSII軟件。它能進行VHDL語言的編譯和綜合,使用方便,功能強大。MAXPLUSII綜合后產生適合ALTERA的 CPLD編程的POF文件,使用POF2JED軟件(ATMEL公司提供),就可將POF文件轉換為適合ATF1508AS的工業標準JEDEC編程文件,下載到ATF1508AS芯片中。

4 器件編程

ATF1508AS器件是利用4腳JTAG協議在系統編程(ISP)的。ATMEL提供了ISP硬件(下載電纜)和軟件,以允許從PC對ATF1508AS進行編程。若要允許ISP編程支持“自動測試裝置(ATE)”向量,必須通過ATMEL的ISP軟件生成串行向量格式(SVF)文件,也可轉換為除SVF外的其它ATE測試格式。ATF1508AS器件也可以用標準的第三方編程器來編程,這時JTAG ISP口可以被禁止從而允許這四個額外的I/O引腳用于邏輯功能。

ATF1508AS還有一個特性就是如果由于任何原因編程過程被中斷,則器件將被鎖定以防止輸入和I/O引腳被驅動。在這種狀態下,輸入和I/O引腳缺省下為高阻狀態。在編程器件時,輸入和I/O引腳也將為高阻狀態。此外,引腳保持電路設置在器件編程期間將保持以前的狀態。 ATF1508AS器件出廠時被初始化為已擦除狀態,可以直接用來ISP編程。

5 應用實例

(1)應用ATF1508AS進行串并轉換

本系統應用ATMEL公司的ATF1508AS進行串行數據到并行數據的轉換,在進行數據采集中,用到Crystal半導體公司生產的24位高精度Σ-△模/數轉換器CS5321/CS5322組件。該組件最終輸出字長為24位的2的補碼格式的串行數字信號,將其轉換為并行數據可以方便與單片機的接口。串并轉換可采用移位寄存器來實現。對實現6通道24位采樣,若采用移位寄存器,則需要8位移位寄存器,共3×6=18片,另外還要用幾片譯碼器。這樣,會使芯片數量大增,占用大片電路板面積,使系統的體積增大。本系統使用ATF1508AS來實現6通道24位數據的串并轉換,可將大部分數字邏輯設計(包括組合邏輯和時序邏輯)集成在一個芯片內,大幅減少芯片數量,減小系統體積。

由于ATF1508AS內部有128個宏單元,而且24位串并轉換需要24個移位寄存器,因此不能同時進行6通道的串并轉換,只能分時復用。本系統分3次進行串并轉換,每次轉換2個通道,等待單片機讀取2個通道的并行數據后再進行剩下的轉換。部分串并轉換VHDL程序如下(硬件描述語言是VHDL,軟件是ALTERA公司的MAXPLUSⅡ軟件和ATMEL公司的POF2JED軟件,下載軟件是ATMEL公司的ATMISP,下載電纜是ATMEL公司的專用電纜):

s2p : process(SCLK1M,DRDYIN,WORKING,RESET)

begin

if WORKING=‘1’ or RESET=‘1’ then

shift_enable 《= ‘0’;

state 《= s0;

elsif SCLK1M‘event and SCLK1M=’0‘ then

count1 《= count1+1;

case state is

when s0 =》if DRDYIN=’0‘ then

shift_enable 《= ’1‘;

count1 《= (others=》’0‘);

int_reg 《= ’1‘;

state 《= s1;

elsif READOK=’1‘ then

int_reg 《= ’1‘;

end if;

when s1=》shift_reg0《=shift_reg0(22 downto 0)& SOD(0);

shift_reg1《=shift_reg1(22 downto 0)& SOD(1);

if count1=23 then

shift_enable 《= ’0‘;

int_reg 《= ’0‘;

state 《= s2;

else

int_reg 《= ’1‘; end if;

when s2 =》 if shift_enable=’1‘ then

shift_reg0《=shift_reg0(22 downto 0)& SOD(2);

shift_reg1《=shift_reg1(22 downto 0)& SOD(3);

if count1=23 then

shift_enable 《= ’0‘;

int_reg 《= ’0‘;

state 《= s3;

else

int_reg 《= ’1‘; end if;

elsif READOK=’1‘ then

shift_enable 《= ’1‘;

count1 《= (others=》’0‘);

end if;

when s3 =》if shift_enable=’1‘ then

shift_reg0《=shift_reg0(22 downto 0)& SOD(4);

shift_reg1《=shift_reg1(22 downto 0)& SOD(5);

if count1=23 then

shift_enable 《= ’0‘;

int_reg 《= ’0‘;

state 《= s0;

else

int_reg 《= ’1‘; end if;

elsif READOK=’1‘ then

shift_enable 《= ’1‘;

count1 《= (others=》’0‘);

end if;

end case;

end if;

end process;

(2)應用ATF1508AS進行高速USB通信

USB是近年來應用在PC領域的新型接口技術,具有使用方便、速度快、連接靈活、支持熱插拔等特點。USB1.1協議定義在高速下12 Mb/s、低速下1.5 Mb/s的傳輸速度。若要達到高速12 Mb/s(相當于近1 MB/s)的速度,就要大約1μs傳輸1個字節。但由于USB的控制傳輸、錯誤檢測以及單片機本身速度的限制,很難達到這么高的速度,因此,必須采用 DMA方式才能達到真正的高速傳輸,使用CPLD就可以實現類似DMA方式。單片機負責解釋USB的控制傳輸,當要進行從外存取數送到USB接口芯片時,單片機讓出總線,由CPLD完成該工作。CPLD產生外存的讀取時序和地址、片選信號,同時產生USB接口芯片的寫時序和地址、片選信號,這樣就可以自動實現外存數據到USB接口芯片的工作,而且速度很快,不需要單片機干預。以下給出RAM的讀取時序、地址信號和USB接口芯片寫時序的VHDL程序片斷:

rram1 : process(SCLK2M) -- RAM_OE(RAM讀時序)

begin

if SCLK2M’event and SCLK2M=‘1’ then

if read=‘0’ then

ram_oe_reg 《= ‘1’;

cpld2_counter 《= (others=》‘0’);

elsif read=‘1’ then

cpld2_counter 《= cpld2_counter+1;

if cpld2_counter》0 then

ram_oe_reg 《= not ram_oe_reg;

end if;

end if;

end if;

end process;

rram2 : process(SCLK2M,WORKING,RESET) -- ADDRESS(RAM地址信號)

begin

if WORKING=‘1’ or RESET=‘1’ then

adr_reg 《= (others=》‘0’);

elsif SCLK2M‘event and SCLK2M=’0‘ then

if read=’1‘ and ram_oe_reg=’1‘ and cpld2_counter》2 then

adr_reg 《= adr_reg+1;

end if;

end if;

end process;

wd12 : process(SCLK2M) --USB芯片讀時序

begin

if SCLK2M’event and SCLK2M=‘0’ then

if read=‘0’ then

d12_wr_reg 《= ‘1’;

elsif read=‘1’ and cpld2_counter/=129 then

d12_wr_reg 《= not d12_wr_reg;

end if;

end if;

end process;

結束語

CPLD器件的優勢在于縮短開發生產周期,現場靈活性好,而且隨著電子技術的發展,其集成度越來越高,速度越來越快,價格也逐漸降低,因此市場發展很快。ATMEL公司的ATF1508AS是高性能、高密度的復雜可編程邏輯器件,使用方便,具有很高的性價比,因此具有廣闊的應用前景。

電子發燒友App

電子發燒友App

評論