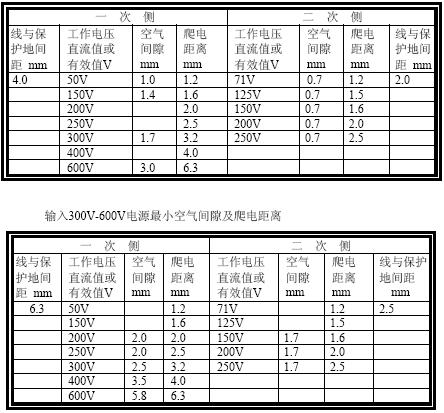

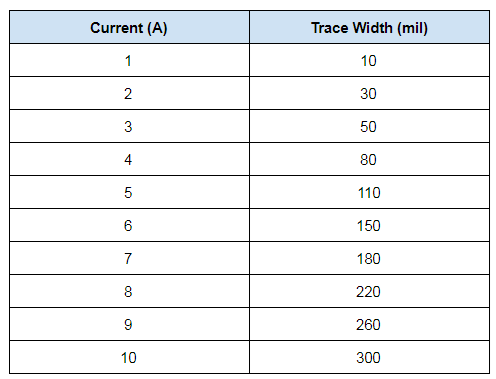

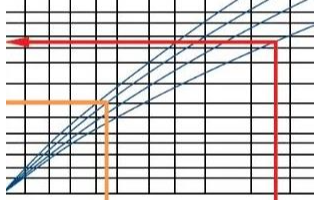

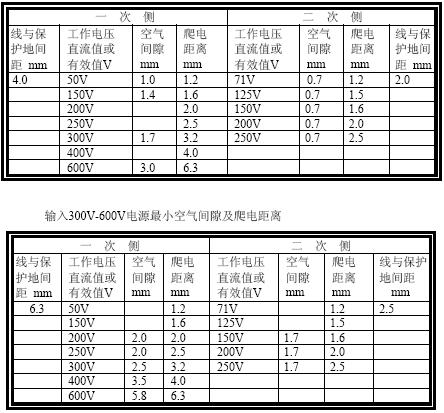

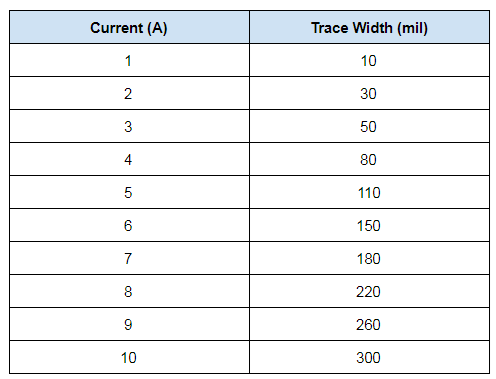

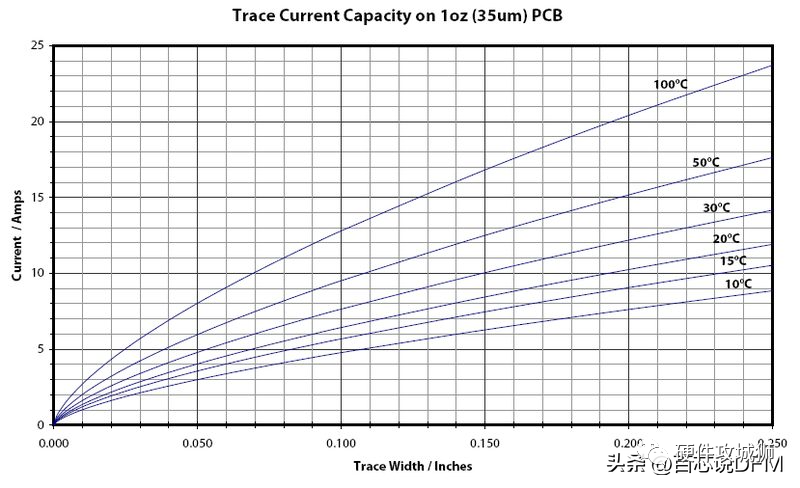

時(shí),您可以使用PCB走線寬度與電流表來確定您需要在布局中使用的電源走線寬度。 另一種選擇是使用基于IPC-2152或IPC-2221標(biāo)準(zhǔn)的計(jì)算器。有必要學(xué)會(huì)如何閱讀IPC標(biāo)準(zhǔn)中的等效走線寬度與電流圖表,因?yàn)镻CB走線

2023-12-06 08:05:09 1981

1981

PCB導(dǎo)線寬度的測(cè)量

由于此測(cè)試是非破壞性的測(cè)試,因此,可在生產(chǎn)前或生產(chǎn)過程中的任何時(shí)候來測(cè)量。

目的:

用于測(cè)量經(jīng)生產(chǎn)得到的導(dǎo)線寬度與客戶線路

2009-04-15 00:34:38 987

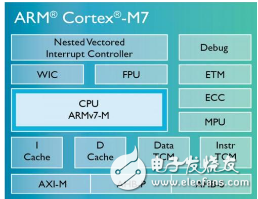

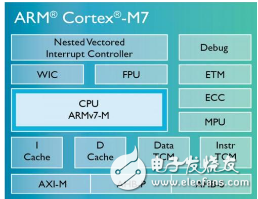

987 最近和同事談到了ARM平臺(tái)下數(shù)據(jù)總線寬度及對(duì)齊方式對(duì)程序效率的影響問題,在定義結(jié)構(gòu)數(shù)據(jù)類型時(shí),為了提高系統(tǒng)效率,要注意字長(zhǎng)對(duì)齊原則。正好有點(diǎn)感觸和大家一起談?wù)劇?

這里主要給大家解釋下所謂的對(duì)齊到底是什么?怎么對(duì)齊?為什么會(huì)對(duì)齊或者說對(duì)齊帶來什么樣的效率差異。

2018-01-30 09:34:14 8196

8196

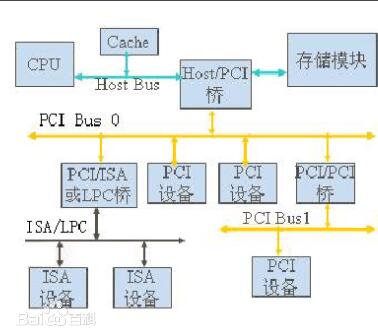

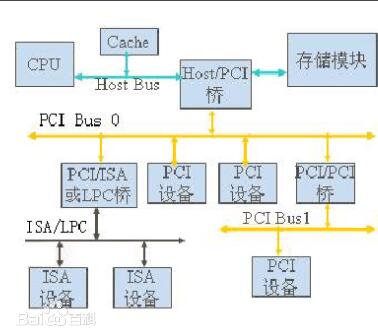

本文主要詳解PCI總線與PXI總線有什么區(qū)別,首先介紹了PCI 總線結(jié)構(gòu)圖、特點(diǎn)及PCI總線性能,其次闡述了PXI總線的特性,最后介紹了PCI總線與PXI總線的區(qū)別。

2018-05-24 09:15:23 13958

13958

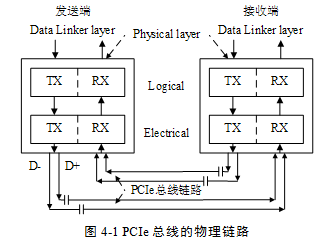

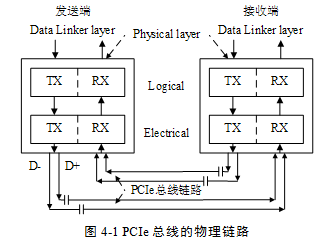

單端并行數(shù)據(jù)信號(hào)才能達(dá)到的總線帶寬。 PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外部設(shè)備共享總線帶寬,而PCIe總線使用了高速差分總線,并采用端到端的連接方式,因此在每一條PCIe鏈路中只能連接兩個(gè)設(shè)備。這使得PCIe與PCI總線采用的

2020-11-21 10:42:13 3562

3562

A2B是汽車音頻總線的簡(jiǎn)稱,一款高帶寬、雙向、數(shù)字音頻總線,由ADI設(shè)計(jì)研發(fā)。

2022-08-31 09:32:42 24822

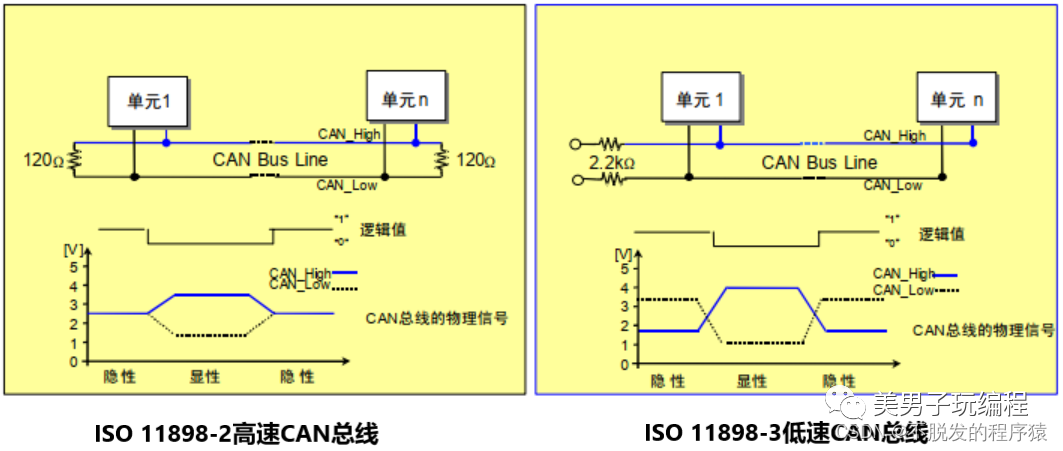

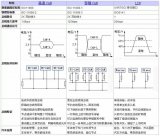

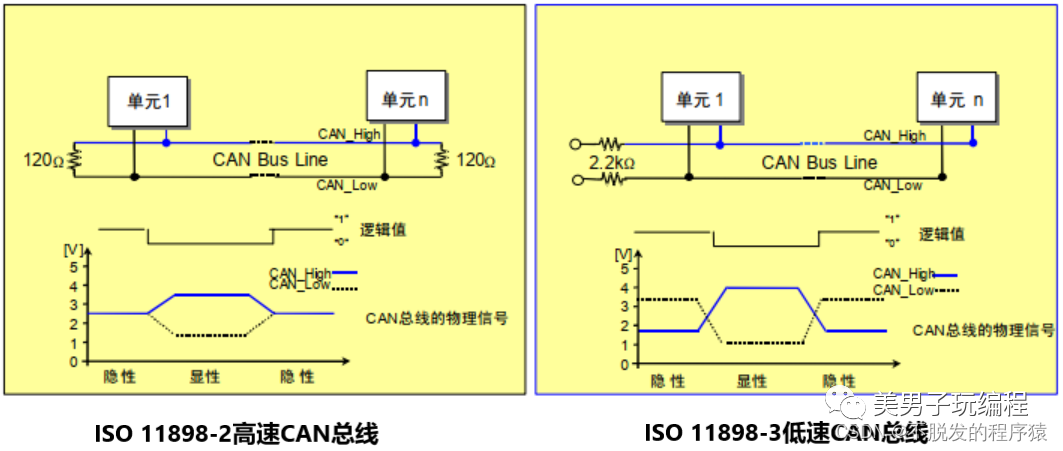

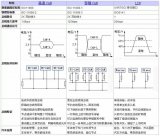

24822 在ISO 11898-2和ISO 11898-3中分別規(guī)定了兩種CAN總線結(jié)構(gòu)(在BOSCH CAN2.0規(guī)范中,并沒有關(guān)于總線拓?fù)浣Y(jié)構(gòu)的說明):高速CAN總線和低速CAN總線,區(qū)別表如下所示。

2023-04-07 09:30:18 1836

1836

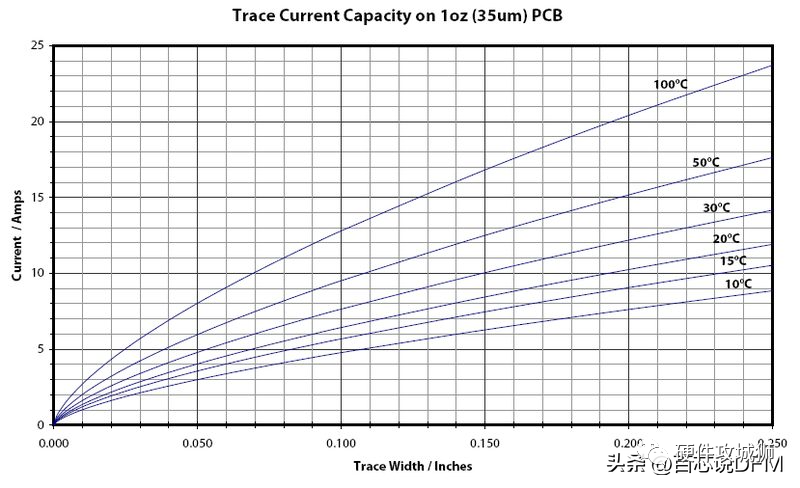

銅是一種具有高熔點(diǎn)的強(qiáng)導(dǎo)體,但仍應(yīng)盡力保持較低的溫度。您需要適當(dāng)調(diào)整電源導(dǎo)軌寬度,使溫度保持在一定限值內(nèi)。不過,這時(shí)您需要考慮在給定走線中流動(dòng)的電流。使用電源軌、高壓元件和電路板的其他對(duì)熱敏感的部分時(shí),您可以使用PCB走線寬度與電流表來確定您需要在布局中使用的電源走線寬度。

2023-12-01 10:05:37 848

848

16.6的走線寬度會(huì)自動(dòng)記憶上一次的走線寬度問題 這個(gè)以前用16.3的時(shí)候都是默認(rèn)多寬的線,換16.6之后就會(huì)出現(xiàn)自動(dòng)記憶上一次的走線寬度,這是16.6本來就是這樣的,還是哪里可以設(shè)置啊?

2014-10-20 15:12:16

總線頻率:反映總線工作的速率(f),通常單位是MHz;總線寬度:數(shù)據(jù)總線的位數(shù)(w),單位時(shí)b(位),是微型計(jì)算機(jī)的一個(gè)重要指標(biāo),通常與處理器字長(zhǎng)一致;總線傳輸速率:總線上可以傳輸?shù)臄?shù)據(jù)總量(BW

2022-03-01 06:43:11

8bitNandflash,然后呢,又要把GPMC拓展出來接到FPGA上,F(xiàn)PGA地址空間4K,總線寬度16biMMC啟動(dòng)方式從MMC0和MMC1啟動(dòng),辣么,eMMC采樣怎樣的啟動(dòng)方式能與FPGA擴(kuò)展的總線共存?

2018-06-20 07:44:04

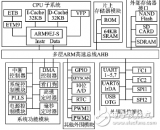

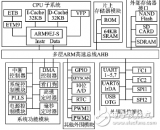

一、概括 首先,說點(diǎn)不靠譜的,APB和AHB總線,我個(gè)人感覺這個(gè)類似于個(gè)人PC系統(tǒng)里的北橋和南橋總線。 南橋總線上掛接的都是鼠標(biāo)、鍵盤這些慢速的設(shè)備,北橋上掛接顯卡等高速設(shè)備。南橋頻率低,北橋頻率高

2021-08-20 06:18:24

常見問題分析。CAN總線和UART、I2C、SPI總線最大的區(qū)別主要在于取消了傳統(tǒng)的地址編碼方式,理論上講總線上的互聯(lián)節(jié)點(diǎn)數(shù)不受限制,擁有強(qiáng)大的握手與出錯(cuò)管理及重發(fā)機(jī)制,具有很強(qiáng)的抗干擾能力。STM32 CAN 基礎(chǔ)內(nèi)容CAN網(wǎng)絡(luò)中主要由CAN控制器和CAN收發(fā)器組成,大部分STM32內(nèi)部都集成了C

2021-08-19 07:41:06

作者:GWD 時(shí)間:2019.06.28一、學(xué)習(xí)要點(diǎn)1、問:DS1302的(雙)總線與DHT11的單總線區(qū)別?答:DS1302的總線是一條數(shù)據(jù)線,一條時(shí)鐘線,此類總線“上寫下讀”,上升沿寫入數(shù)據(jù)給

2022-01-17 07:32:40

`如題,PCB布線時(shí)設(shè)定的電源線寬和地線寬度大于貼片元件引腳寬度,導(dǎo)致不能布線怎么辦?應(yīng)該如何設(shè)置規(guī)則呢?比如說,我設(shè)定電源線寬和GND線寬為20mil,但是LQFP64的引腳寬度只有10mil,連線時(shí)就不能進(jìn)行了,請(qǐng)高手指點(diǎn)一下,謝謝!`

2013-05-10 21:40:01

業(yè)界主導(dǎo)公司開始起草新技術(shù)的規(guī)范,對(duì)其正式命名為PCI Express。它采用了目前業(yè)內(nèi)流行的點(diǎn)對(duì)點(diǎn)串行連接,比起PCI以及更早期的計(jì)算機(jī)總線的共享并行架構(gòu),每個(gè)設(shè)備都有自己的專用連接,不需要向整個(gè)總線請(qǐng)求帶寬,而且可以把數(shù)據(jù)傳輸率提高到一個(gè)很高的頻率,達(dá)到PCI所不能提供的高帶寬。

2016-03-02 08:27:28

mmc.c文件里面函數(shù)mmc_select_bus_width兩個(gè)版本區(qū)別為上圖,3.1版本有正常bus_width寬度的切換,4.0版本沒沒有對(duì)該變量進(jìn)行賦值所以總線寬度無法自動(dòng)識(shí)別,實(shí)測(cè)3.1版本正常操作emmc,4.0版本會(huì)報(bào)錯(cuò),請(qǐng)幫忙檢查一下4.0版本該代碼是否有問題

2022-04-27 09:45:44

目錄1、cpu處理的數(shù)據(jù)寬度2、數(shù)據(jù)總線寬度3、地址總線寬度4、性能差別1、cpu處理的數(shù)據(jù)寬度CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度代表單片機(jī)的位數(shù)。也就是一個(gè)一個(gè)時(shí)鐘周期里,處理器

2021-07-13 06:20:07

嗨,我在我的項(xiàng)目中使用SRIO Gen2 v4 ipcore。我已經(jīng)在kintex 7(xc7k160t)中實(shí)現(xiàn)了它。生成的ipcore具有數(shù)據(jù)寬度為64的用戶axi接口。有沒有選項(xiàng)可以將用戶界面總線寬度更改為32或16.我無法在ipcore GUI中找到這樣的選項(xiàng)。

2020-04-27 09:52:17

PCIe總線概述隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢(shì)所趨。與單端并行信號(hào)相比,高速差分信號(hào)可以使用更高的時(shí)鐘頻率,從而使用更少的信號(hào)線,完成之前需要許多單端并行數(shù)據(jù)信號(hào)才能達(dá)到的總線帶寬。PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外...

2021-07-29 07:07:06

switcher_bus is-- 類屬參數(shù)generic (BUS_WIDTH : integer := 8 ); -- 總線寬度port (din1 : in std_logic_vector

2018-10-23 09:24:16

pcb設(shè)置布線寬度時(shí)沒有g(shù)nd有acc

2019-09-06 05:35:14

的時(shí)間內(nèi)可以傳輸?shù)臄?shù)據(jù)量都是有限的。 這就是總線帶寬,往往以兆字節(jié)每秒(MB/s)表示。 如果動(dòng)態(tài)波形測(cè)量對(duì)您的應(yīng)用十分重要,一定要考慮使用有足夠帶寬的總線。根據(jù)您選擇的總線,總帶寬可以在多個(gè)設(shè)備之間

2018-03-21 11:18:43

/LAN/LXI。了解總線性能 首先,為了對(duì)不同總線的評(píng)價(jià)和比較設(shè)定標(biāo)準(zhǔn),簡(jiǎn)述儀器控制總線相關(guān)的性能標(biāo)準(zhǔn)至關(guān)重要。 帶寬 在考慮可選擇的總線的技術(shù)特點(diǎn)時(shí),帶寬和時(shí)延是兩個(gè)最重要的總線特性。帶寬度

2009-02-26 00:05:14

你好我想知道,我如何創(chuàng)建一個(gè)通用總線寬度的custuom ip核心。在核心內(nèi)部,我必須使用xilinx的addsub ip。但是通用總線寬度必須有一個(gè)選項(xiàng)來重新定義這個(gè)addsub

2019-04-18 07:12:26

PCB走線寬度與通過電流的對(duì)應(yīng)關(guān)系是什么?決定PCB走線寬度的因素有哪些?

2021-09-27 07:24:00

單片機(jī)中晶振頻率和總線頻率的區(qū)別

2017-05-09 19:27:46

**第一至第三章**Q1. 若存儲(chǔ)器的數(shù)據(jù)總線寬度為32位,存取周期為200ns,則存儲(chǔ)器的帶寬是多少?存儲(chǔ)器的帶寬指單位時(shí)間內(nèi)從存儲(chǔ)器進(jìn)出信息的最大數(shù)量。存儲(chǔ)器帶寬 = 1/200ns ×32位

2021-07-28 06:23:01

) 時(shí)鐘同步方式(5) 與 CPU 及時(shí)鐘頻率無關(guān)(6) 總線寬度 32 位(5V)/64 位(3.3V)(7) 能自動(dòng)識(shí)別外設(shè)I2C 簡(jiǎn)單雙向串行總線I2C 器件都有一個(gè)唯一的地址...

2021-11-09 06:01:35

傳送更多數(shù)據(jù),而總線可同時(shí)傳輸?shù)臄?shù)據(jù)數(shù)就稱為寬度(width),以比特為單位,總線寬度愈大,傳輸性能就愈佳。總線的帶寬(即單位時(shí)間內(nèi)可以傳輸?shù)目倲?shù)據(jù)數(shù))為:總線帶寬 = 頻率 x 寬度(Bytes/sec)。當(dāng)總線空閑(其他器件都以高阻態(tài)形式連接在總線上)且一個(gè)器件要與目的器件

2022-02-24 06:50:10

是否可以將數(shù)據(jù)總線寬度配置為24位?我檢查了8, 16位和32位之間的差異,只改變了最后8位中的第七十九行(CyuU3pIPIBGPGIFIFBuxCONFIG)。我需要24位數(shù)據(jù)寬度和SPI為我的啟動(dòng)從SPI閃存(固件)。如果我查看數(shù)據(jù)表中的PIN表,可以看到數(shù)據(jù)總線和SPI總線之間沒有交叉點(diǎn)。

2019-08-21 09:02:22

` 1概述用于PL與DDR3交互的AXI HP總線,它的性能到底如何?吞吐量是否能滿足我們的應(yīng)用?必須4個(gè)通道同時(shí)使用?還是只使用1個(gè)通道?時(shí)鐘頻率的高低對(duì)AXI HP總線的帶寬有什么影響?這些

2019-11-28 10:11:38

的core里,請(qǐng)問MSM數(shù)據(jù)搬移的速度和總線帶寬是多少,是否足夠在8個(gè)core完成各自FFT運(yùn)算的時(shí)間里,更新8個(gè)核需要計(jì)算的下一次的行數(shù)據(jù)。

2018-06-25 03:14:41

AD16為什么不按首選走線寬度走呢?總是按照最小走線寬度走

2019-05-21 01:43:25

想請(qǐng)教一下,C6678中的EDMA的傳輸過程是什么樣的?DBS是傳輸控制器一次讀寫的最大字節(jié)數(shù),最大128字節(jié),但是數(shù)據(jù)總線寬度才32字節(jié)啊,這兩者有何關(guān)系呢?還有每次把數(shù)據(jù)讀到FIFO中

2019-01-10 11:16:33

請(qǐng)問一下arm總線帶寬的余量如何設(shè)計(jì)大于30呢?

2023-03-15 10:20:15

有可能動(dòng)態(tài)地改變狀態(tài)機(jī)的總線寬度在16位和8位之間嗎?我正在禁用狀態(tài)機(jī),改變CYFXGPIFRIGHEVE的寄存器值以獲得16位或8位數(shù)據(jù)總線,然后重新裝入狀態(tài)機(jī),但這對(duì)我來說不行,是正確的方法還是

2019-06-20 11:31:28

我正在使用 FX3S 芯片上的 SDIO 端口 0 與解調(diào)設(shè)備通信。 我使用下面的代碼片段將總線寬度設(shè)置為 1 位。

io_cfg.s0Mode = CY_U3P_SPORT_1BIT

2024-03-05 07:03:33

親愛的先生,F(xiàn)X3支持32位GPIF II接口。我們使用GPIF設(shè)計(jì)器1來繪制接口和狀態(tài)機(jī)圖。在接口中只有8、16、24、32選擇GPIF數(shù)據(jù)總線寬度。但是我需要12 GPIF數(shù)據(jù)總線。請(qǐng)幫助選擇12位GPIF數(shù)據(jù)總線。謝謝你最好的問候,拉米什

2019-09-17 12:28:17

PCI總線漸漸地取代了ISA總線。它有許多優(yōu)點(diǎn),比如即插即用(Plug and Play)、中斷共享等。在這里我們對(duì)PCI總線做一個(gè)深入的介紹。 從數(shù)據(jù)寬度上看,PCI總線有32bit、64bi

2008-06-16 14:24:07 147

147 1。典型的焊盤直徑和最大導(dǎo)線寬度的關(guān)系 焊盤直徑(英寸/Mil/毫米) 最大導(dǎo)線寬度(英寸/Mil/

2006-04-16 23:45:44 2028

2028 1。典型的焊盤直徑和最大導(dǎo)線寬度的關(guān)系 焊盤直徑(英寸/Mil/毫米) 最大導(dǎo)線寬度(英寸/Mil/毫米) 0.040/ 40 /1.0

2006-09-25 14:06:54 551

551 PCB設(shè)計(jì)時(shí)銅箔厚度,走線寬度和電流的關(guān)系不同厚度,不同寬度的銅箔的載流量見下表:

2007-12-12 14:30:28 14675

14675

要:本應(yīng)用筆記說明了如何計(jì)算DS31256 HDLC控制器的總線帶寬。并展示了一個(gè)實(shí)驗(yàn)室實(shí)測(cè)的結(jié)果。同時(shí)演示了一個(gè)總線利用率速算表,該速算表如果需要可以索要。

2009-04-18 11:24:11 1181

1181

AGP、PCI-E總線帶寬的計(jì)算方法

總線是一組進(jìn)行互連和傳輸信息(指令、數(shù)據(jù)和地址)的信號(hào)線。主要參數(shù)有總線位寬、總線時(shí)鐘頻率和總線傳輸速率。

※總

2009-05-09 08:42:41 2953

2953 什么是數(shù)據(jù)總線寬度/地址總線寬度?

數(shù)據(jù)總線寬度

數(shù)據(jù)總線負(fù)責(zé)整個(gè)系統(tǒng)的數(shù)據(jù)流量的大

2010-02-04 10:25:01 6588

6588 什么是主板VL局部總線/ATX電源/ATX板型

VL局部總線:(Local Bus:局部總線)是VESA組織設(shè)計(jì)的一種開放性總線結(jié)構(gòu)。它的寬度是32位

2010-02-05 11:53:29 724

724 高帶寬嵌入式應(yīng)用中SoC微控制器的新型總線開發(fā)

傳統(tǒng)SoC總線架構(gòu)已不能滿足新的聯(lián)網(wǎng)嵌入式設(shè)計(jì)對(duì)高帶寬數(shù)據(jù)流進(jìn)行實(shí)時(shí)控制的需求, NetSilicon開發(fā)的可編程總線帶寬

2010-03-03 16:16:51 622

622

PCI總線:

為32位總線,且可擴(kuò)展為64位,有124個(gè)腳(實(shí)際上去掉4個(gè)定位卡有120引腳),AD線有32條,工作頻率為33MHZ/66MHZ,最大傳輸速率133MB/S。總線寬度32位(5V

2010-12-17 17:58:06 745

745 導(dǎo)線寬度與負(fù)載電流

2011-01-20 17:56:13 32

32 賽普拉斯半導(dǎo)體公司日前宣布推出具有 32 位總線寬度的 128 Mb、64 Mb 和 32 Mb MoBL(更長(zhǎng)電池使用壽命)異步SRAM

2011-08-02 09:01:30 757

757 在傳統(tǒng)的嵌入式多處理器系統(tǒng)中,處理器之間的互連是通過分時(shí)共享總線來實(shí)現(xiàn)的,所有通信爭(zhēng)用總線帶寬,由此就造成處理器越多,每個(gè)處理器可用帶寬就越少, 從而帶來嚴(yán)重的系統(tǒng)

2012-07-16 16:46:36 2862

2862

PCB走線寬度標(biāo)準(zhǔn)(軍用)

2013-09-09 16:26:20 0

0 PCB設(shè)計(jì)時(shí)銅箔厚度,走線寬度和電流的關(guān)系

2017-01-28 21:32:49 0

0 SPI、I2C、UART三種串行總線協(xié)議的區(qū)別

2017-07-17 17:23:16 0

0 數(shù)據(jù)總線DB用于傳送數(shù)據(jù)信息。地址總線AB是專門用來傳送地址的,由于地址只能從CPU傳向外部存儲(chǔ)器或I/O端口,所以地址總線總是單向三態(tài)的,這與數(shù)據(jù)總線不同。

2017-11-13 09:09:39 33370

33370

1.有多大的數(shù)據(jù)量經(jīng)過該總線? 所有的 PC 總線在一定的時(shí)間內(nèi)可以傳輸?shù)臄?shù)據(jù)量都是有限的。 這就是總線帶寬,往往以兆字節(jié)每秒(MB/s)表示。 如果動(dòng)態(tài)波形測(cè)量對(duì)您的應(yīng)用十分重要,一定要考慮

2017-11-15 10:20:23 1524

1524 指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度不同:

2017-11-15 15:43:05 2884

2884 總線可分成CPU總線,存儲(chǔ)器總線,I/O通道總線和外圍接口總線四個(gè)層次。每個(gè)層次的總線又分為地址總線、控制總線、數(shù)據(jù)總線等三種。地址總線和控制總線上的信號(hào)是由執(zhí)行總線操作的主設(shè)備產(chǎn)生的,CPU

2017-11-16 14:56:56 59441

59441 。SDR SDRAM一個(gè)時(shí)鐘周期只能傳輸一個(gè)數(shù)據(jù)位寬的數(shù)據(jù), 因此在相同的數(shù)據(jù)總線寬度和工作頻率下, DDR SDRAM的總線帶寬比SDR SDRAM的總線帶寬提高了一倍。

2018-07-20 18:38:00 12744

12744

8位單片機(jī) 16位 32位區(qū)別? 指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度. 如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。

2018-07-15 11:07:00 122543

122543 指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度.

如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。

2018-01-22 15:05:08 15419

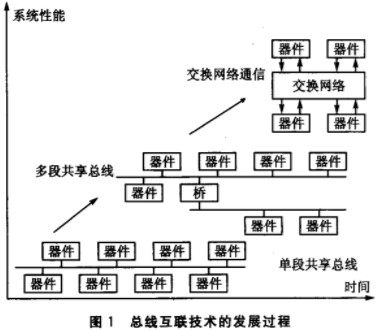

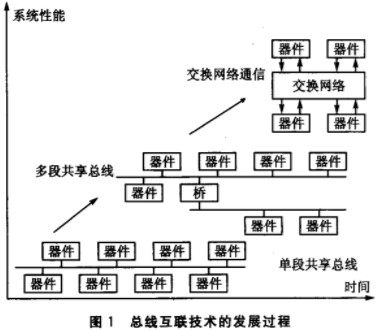

15419 無論是單分段共享總線互聯(lián)系統(tǒng),還是級(jí)聯(lián)的多分段共享總線互聯(lián)系統(tǒng),在這類基于共享的總線體系結(jié)構(gòu)中,所有通信無不是在爭(zhēng)用總線帶寬,由此造成外設(shè)越多可用帶寬就越少,從而帶來嚴(yán)重的傳輸瓶頸。不僅如此

2019-05-21 08:16:00 2268

2268

一個(gè)比特。因此,必須同時(shí)采用多條線路才能傳送更多數(shù)據(jù),而總線可同時(shí)傳輸?shù)臄?shù)據(jù)數(shù)就稱為寬度(width),以比特為單位,總線寬度愈大,傳輸性能就愈佳。總線的帶寬(即單位時(shí)間內(nèi)可以傳輸?shù)目倲?shù)據(jù)數(shù))為:總線帶寬

2018-11-28 16:58:32 586

586 指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度。 如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度不同:

2019-04-17 17:27:00 0

0 位數(shù)指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度不同:

2019-09-20 17:19:00 0

0 位數(shù)指CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度相同,則這個(gè)寬度就是所說的單片機(jī)位數(shù)。如果總線寬度與CPU一次處理的數(shù)據(jù)寬度不同:

2019-06-19 17:44:00 0

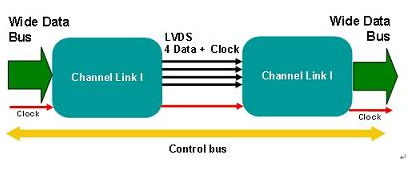

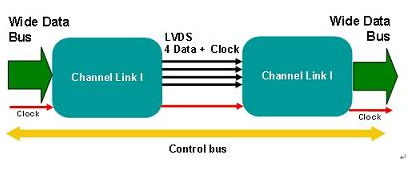

0 早期的SerDes產(chǎn)品,如圖1所示的Channel Link I器件,通過使用一個(gè)單獨(dú)的時(shí)鐘線把并行數(shù)據(jù)總線(寬度達(dá)48位)串行到多通道LVDS總線上。在此之前,通常是利用寬帶狀線纜的數(shù)據(jù)總線實(shí)現(xiàn)從點(diǎn)A到點(diǎn)B的數(shù)據(jù)傳輸。

2019-10-10 16:00:46 2170

2170

傳統(tǒng)SoC總線架構(gòu)已不能滿足新的聯(lián)網(wǎng)嵌入式設(shè)計(jì)對(duì)高帶寬數(shù)據(jù)流進(jìn)行實(shí)時(shí)控制的需求,NetSilicon開發(fā)的可編程總線帶寬控制系統(tǒng)可以使多個(gè)資源同時(shí)訪問總線,使其既滿足應(yīng)用要求又不會(huì)影響其他重要操作的性能。本文將對(duì)該系統(tǒng)的可編程總線帶寬分配方案進(jìn)行探討。

2020-04-11 09:24:51 2401

2401 銅是一種具有高熔點(diǎn)的強(qiáng)導(dǎo)體,但您仍應(yīng)盡力保持低溫。在這里,您需要適當(dāng)調(diào)整走線寬度的大小,以將溫度保持在一定范圍內(nèi)。但是,這是您需要考慮給定走線中流動(dòng)的電流的地方。當(dāng)使用電源軌,高壓組件以及電路板

2020-12-31 12:14:08 7167

7167

在下一個(gè) PCB 原型的 PCB 設(shè)計(jì)過程中,有幾個(gè)因素會(huì)影響走線的寬度,長(zhǎng)度和樣式。本文將深入探討各種需要特定走線布局特征以及如何或何時(shí)將它們納入您的 PCB 設(shè)計(jì)的應(yīng)用。 什么是走線寬度

2020-10-29 15:04:03 4711

4711 我們需要知道我們的目的是測(cè)量經(jīng)生產(chǎn)得到的導(dǎo)線寬度與客戶線路圖形上的原線路設(shè)計(jì)要求寬度是否還是一致的。

2020-11-17 10:18:28 3048

3048 花點(diǎn)時(shí)間看了一些關(guān)于LIN總線基礎(chǔ)的內(nèi)容,把其中的關(guān)鍵點(diǎn)提取了出來,在這里分享給大家。在這里你可能要問“不都有CAN總線了嗎?這個(gè)LIN總線又是從哪里來的?”其實(shí)理由很簡(jiǎn)單,就是CAN總線太貴啦!處處都用CAN總線的話,那整車的總線架構(gòu)成本將會(huì)變得很高!

2021-03-17 17:51:18 25252

25252

設(shè)計(jì)得非常簡(jiǎn)單和有效,可以連接大量外圍設(shè)備。通過使用中央仲裁機(jī)制,可以方便地實(shí)現(xiàn)總線設(shè)備間的通信:然而,當(dāng)速率和帶寬不斷增加時(shí),并行結(jié)構(gòu)的潛力不斷被發(fā)掘并不再能夠滿足系統(tǒng)設(shè)計(jì)要求。 并行總線結(jié)構(gòu)的帶寬可以通過增加總線寬度或者提高總

2021-10-15 10:10:26 7445

7445 激光器的線寬和帶寬名字很相近,但是表示的意思差很大的。首先看線寬,線寬比較好理解,就是激光光譜的半峰全寬。 激光器帶寬,就不是一個(gè)光譜的長(zhǎng)度單位了,它的全名應(yīng)該叫激光器調(diào)制帶寬。 半導(dǎo)體激光器的調(diào)制

2021-10-27 16:05:22 8142

8142

/s(4) 時(shí)鐘同步方式(5) 與 CPU 及時(shí)鐘頻率無關(guān)(6) 總線寬度 32 位(5V)/64 位(3.3V)(7) 能自動(dòng)識(shí)別外設(shè)I2C 簡(jiǎn)單雙向串行總線I2C 器件都有一個(gè)唯一的地址...

2021-11-04 10:06:13 12

12 目錄1、cpu處理的數(shù)據(jù)寬度2、數(shù)據(jù)總線寬度3、地址總線寬度4、性能差別1、cpu處理的數(shù)據(jù)寬度CPU處理的數(shù)據(jù)的寬度,參與運(yùn)算的寄存器的數(shù)據(jù)長(zhǎng)度代表單片機(jī)的位數(shù)。也就是一個(gè)一個(gè)時(shí)鐘周期里,處理器

2021-11-15 16:21:11 20

20 傳送更多數(shù)據(jù),而總線可同時(shí)傳輸?shù)臄?shù)據(jù)數(shù)就稱為寬度(width),以比特為單位,總線寬度愈大,傳輸性能就愈佳。總線的帶寬(即單位時(shí)間內(nèi)可以傳輸?shù)目倲?shù)據(jù)數(shù))為:總線帶寬 = 頻率 x 寬度(Bytes/sec)。當(dāng)總線空閑(其他器件都以高阻態(tài)形式連接在總線上)且一個(gè)器件要與目的器件

2021-12-31 19:57:13 15

15 總線帶寬就是總線的最大傳輸速度,帶寬越大速度就越快。但是總線帶寬的計(jì)算公式里卻要除以一個(gè)8很多人都不知道為什么,接下來詳細(xì)介紹一下:

2022-01-29 17:04:00 14959

14959 當(dāng)涉及到PCB 設(shè)計(jì)時(shí),PCB 走線電流容量帶來的限制是至關(guān)重要的。雖然IPC-2221通用設(shè)計(jì)指南是一個(gè)很好的起點(diǎn),但 PCB 走線寬度計(jì)算器提供了可用于電路板設(shè)計(jì)的準(zhǔn)確值。

2022-08-22 09:05:44 2838

2838 plccan總線通訊的意義就在于提高了PLC工作的穩(wěn)定性和安全性,畢竟CAN總線可以算得上是最穩(wěn)的幾類現(xiàn)場(chǎng)總線之一了。

2022-09-21 14:07:23 3734

3734 走線寬度是PCB設(shè)計(jì)中最關(guān)鍵的因素之一。

2023-07-12 13:53:28 7781

7781

14 外部總線 RA6器件包括一個(gè)外部總線控制器。某些RA6器件具有內(nèi)置的SDRAM控制器。 14.1 總線寬度和多路復(fù)用 外部存儲(chǔ)區(qū)的訪問寬度可以設(shè)置為8位或16位。通過將CSnCR寄存器或SDC

2023-07-14 12:10:05 290

290

總線控制在計(jì)算機(jī)和電子系統(tǒng)中起著重要的作用,它管理和協(xié)調(diào)了各個(gè)設(shè)備和組件之間的數(shù)據(jù)傳輸和通信,保證了系統(tǒng)的正常運(yùn)行和效率。通過總線控制,各個(gè)設(shè)備可以共享總線資源并進(jìn)行協(xié)同操作,實(shí)現(xiàn)數(shù)據(jù)傳輸和協(xié)議的正確性和可靠性。

2023-07-24 15:32:34 5474

5474 CAN總線負(fù)載率(busload)表征的是單位時(shí)間內(nèi)總線上的位流(bitstream)相對(duì)總線帶寬的占比。

2023-07-27 17:29:26 695

695

LIN(Local Interconnect Network)總線是基于UART/SCI(通用異步收發(fā)器/串行接口)的低成本串行通訊協(xié)議。其目標(biāo)定位于車身網(wǎng)絡(luò)模塊節(jié)點(diǎn)間的低端通信,主要用于智能傳感器和執(zhí)行器的串行通信,而這正是CAN總線的帶寬和功能所不要求的部分。

2023-09-13 16:35:41 4329

4329

PCB設(shè)計(jì)時(shí)銅箔厚度,走線寬度和電流的關(guān)系

2023-03-01 15:37:46 13

13 并行總線和串行總線的區(qū)別? 并行總線和串行總線是計(jì)算機(jī)系統(tǒng)中常見的兩種數(shù)據(jù)傳輸方式,它們有著不同的工作原理和應(yīng)用場(chǎng)景。在這篇文章中,我將詳細(xì)介紹并行總線和串行總線的區(qū)別,并探討它們各自的優(yōu)勢(shì)和劣勢(shì)

2023-12-07 16:45:27 1519

1519 can總線與485總線五大區(qū)別? CAN總線和485總線是現(xiàn)代工業(yè)自動(dòng)化領(lǐng)域中常見的兩種通信總線,它們都具有一定的優(yōu)勢(shì)和特點(diǎn)。 一、傳輸距離 CAN總線和485總線在傳輸距離上有著明顯的差異。CAN

2024-02-03 09:22:39 1583

1583 pcb板走線寬度的設(shè)計(jì)指南

2024-02-23 17:30:13 272

272

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論