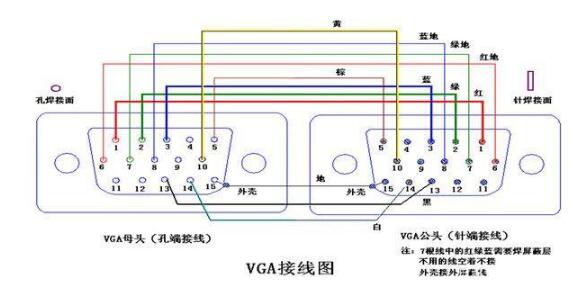

VGA(Video Graphics Array)視頻圖形陣列是IBM于1987年提出的一個使用模擬信號的電腦顯示標準。VGA接口即電腦采用VGA標準輸出數(shù)據(jù)的專用接口。VGA接口共有15針,分成3排,每排5個孔,顯卡上應(yīng)用最為廣泛的接口類型,絕大多數(shù)顯卡都帶有此種接口。它傳輸紅、綠、藍模擬信號以及同步信號(水平和垂直信號)。

vga接口原理

常見接口之色差VGA接口(D-Sub接口)

說到VGA接口,相信很多朋友都不會陌生,因為這種接口是電腦顯示器上最主要的接口,從塊頭巨大的CRT顯示器時代開始,VGA接口就被使用,并且一直沿用至今,另外VGA接口還被稱為D-Sub接口。

很多人覺得只有HDMI接口才能進行高清信號的傳輸,但這是一個大家很容易進入的誤區(qū),因為通過VGA的連接同樣可以顯示1080P的圖像,甚至分辨率可以達到更高,所以用它連接顯示設(shè)備觀看高清視頻是沒有問題的,而且雖然它是種模擬接口,但是由于VGA將視頻信號分解為R、G、B三原色和HV行場信號進行傳輸,所以在傳輸中的損耗還是相當(dāng)小的。

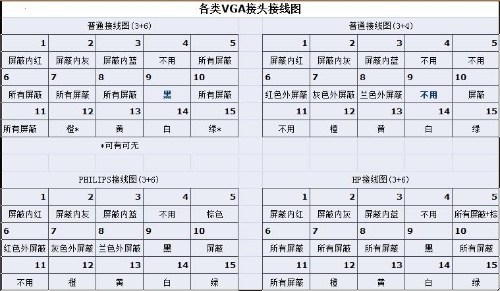

15針VGA接口引腳(4張)

VGA接口產(chǎn)生原因: 顯卡所處理的信息最終都要輸出到顯示器上,顯卡的輸出接口就是電腦與顯示器之間的橋梁,它負責(zé)向顯示器輸出相應(yīng)的圖像信號。CRT顯示器因為設(shè)計制造上的原因,只能接受模擬信號輸入,這就需要顯卡能輸出模擬信號。VGA接口就是顯卡上輸出模擬信號的接口,VGA(Video Graphics Array)接口,也叫D-Sub接口。雖然液晶顯示器可以直接接收數(shù)字信號,但很多低端產(chǎn)品為了與VGA接口顯卡相匹配,因而采用VGA接口。

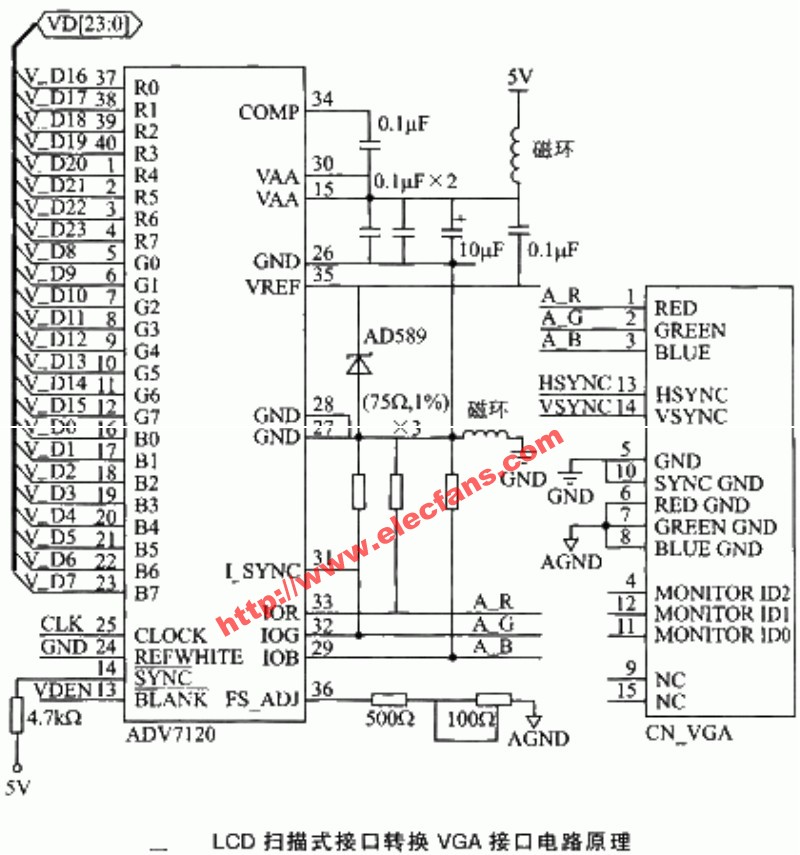

vga接口設(shè)計原理

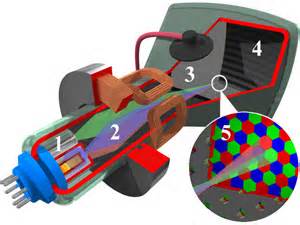

基于CRT的VGA顯示使用了幅度調(diào)制的方式來移動電子束(陰極射線)在涂有熒光粉層的屏幕上顯示信息。彩色CRT顯示使用了三個電子束(紅、藍、綠)對陰極射線管頂端顯示屏內(nèi)部的熒光圖層施加能量。電子槍產(chǎn)生電子束,其工作原理是由燈絲加熱陰極,陰極發(fā)射電子,然后在加速極電場的作用下,經(jīng)聚焦極聚成很細的電子束,在陽極高壓作用下,獲得巨大的能量,以極高的速度去轟擊熒光粉層。

這些電子束轟擊的目標就是熒光屏上的三原色。為此,電子槍發(fā)射的電子束不是一束,而是三束,它們分別受電腦顯卡R、 G、 B三個基色視頻信號電壓的控制,去轟擊各自的熒光粉單元。受到高速電子束的激發(fā),這些熒光粉單元分別發(fā)出強弱不同的紅、綠、藍三種光。根據(jù)空間混色法(將三個基色光同時照射同一表面相鄰很近的三個點上進行混色的方法)產(chǎn)生豐富的色彩,這種方法利用人們眼睛在超過一定距離后分辨力不高的特性,產(chǎn)生與直接混色法相同的效果。用這種方法可以產(chǎn)生不同色彩的像素,而大量的不同色彩的像素可以組成一張漂亮的畫面,而不斷變換的畫面就成為可動的圖像。

利用了人們眼睛的視覺殘留特性和熒光粉的余輝作用,這就是即使只有一支電子槍,只要三支電子束可以足夠快地向所有排列整齊的像素進行激發(fā),人們還是可以看到一幅完整的圖像的。現(xiàn)在的CRT顯示器中的電子槍能發(fā)射這三支電子束,然后以非常非常快的速度對所有的像素進行掃描激發(fā)。

要形成非常高速的掃描動作,還需要偏轉(zhuǎn)線圈(Deflection coils)的幫助,通過它可以使顯像管內(nèi)的電子束以一定的順序,周期性地轟擊每個像素,使每個像素都發(fā)光,而且只要這個周期足夠短,也就是說對某個像素而言電子束的轟擊頻率足夠高,人們就會看到一幅完整的圖像。把這種電子束有規(guī)律的周期性運動叫掃描運動。

因為有大量排列整齊的像素需要激發(fā),必然要求有規(guī)律的電子槍掃描運動才顯得高效,通常實現(xiàn)掃描的方式很多,如直線式掃描,圓形掃描,螺旋掃描等等。其中,直線式掃描又可分為逐行掃描和隔行掃描兩種,事實上,在CRT顯示系統(tǒng)中兩種都有采用。逐行掃描是電子束在屏幕上一行緊接一行從左到右的掃描方式,是比較先進的一種方式。而隔行掃描中,一張圖像的掃描不是在一個場周期中完成的,而是由兩個場周期完成的。在前一個場周期掃描所有奇數(shù)行,稱為奇數(shù)場掃描,在后一個場周期掃描所有偶數(shù)行,稱為偶數(shù)場掃描。無論是逐行掃描還是隔行掃描,為了完成對整個屏幕的掃描,掃描線并不是完全水平的,而是稍微傾斜的,為此電子束既要作水平方向的運動,又要作垂直方向的運動。前者形成一行的掃描,稱為行掃描,后者形成一幅畫面的掃描,稱為場掃描。

典型的,視頻數(shù)據(jù)是來源于視頻刷新存儲器,給每個像素位置分配一個或多個字節(jié)(Nexys2板子一個像素使用了3比特)。當(dāng)電子束穿過顯示屏?xí)r,控制器必須索引視頻存儲器,并且恢復(fù)和應(yīng)用視頻數(shù)據(jù)在準確的時間來顯示。

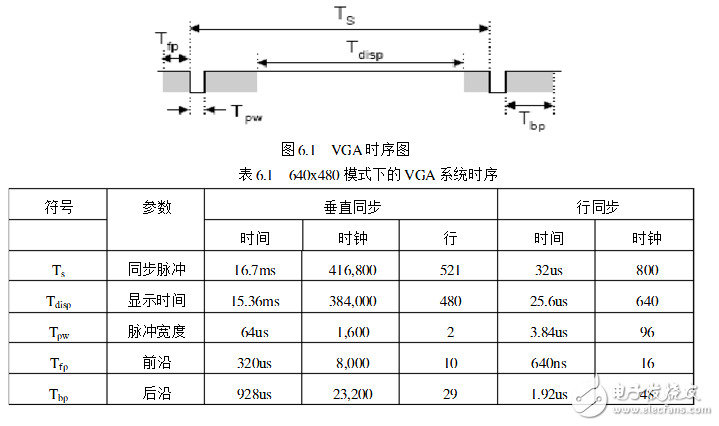

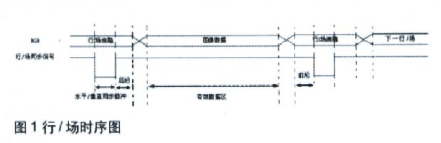

基于像素時鐘,VGA控制器必須產(chǎn)生HS和VS時序信號,并配合視頻數(shù)據(jù)的傳輸。像素時鐘定義了用于顯示一個像素信息的時間。VS信號定義了顯示的刷新頻率。刷新頻率是顯示圖層和電子束密度的函數(shù),實際上的刷新頻率在50Hz到120Hz范圍。在給定的刷新頻率下的顯示的行定義了水平“折回”頻率。對于640像素和480行的顯示模式使用了25MHz的像素時鐘和60+/-1Hz的刷新頻率。圖6.1給出了信號的時序圖,表6.1給出了VGA相對應(yīng)的時序參數(shù)

VGA顯示設(shè)計原理

1.圖像存儲原理

該設(shè)計將使用核產(chǎn)生器生成的塊ROM存儲器來存儲圖片,并在VGA顯示器上進行顯示。圖片的大小為240x160像素,圖片的名字為loons240x160.jpg。

為了顯示圖片,必須先將JPAG格式的圖片轉(zhuǎn)換為相應(yīng)的loons240x160.coe文件,這個轉(zhuǎn)換過程是使用matlab函數(shù)IMG2coe8(imgfile,outfile)實現(xiàn)的。注意這個函數(shù)產(chǎn)生的.coe文件為每個圖形像素包含8位的字節(jié)信息,其格式為:

[R2,R1,R0,G2,G1,G0,B1,B0]

讀入Matlab函數(shù)的原始圖像包含8位的紅色,8位的綠色,8位的藍色,存儲在.coe文件的圖像包含3位的紅色,3位綠色和2位的藍色。這種轉(zhuǎn)換是和Nexys2板子的8位VGA顏色的硬件設(shè)計是相對應(yīng)的,其圖像質(zhì)量必然降低。

2.設(shè)計結(jié)構(gòu)

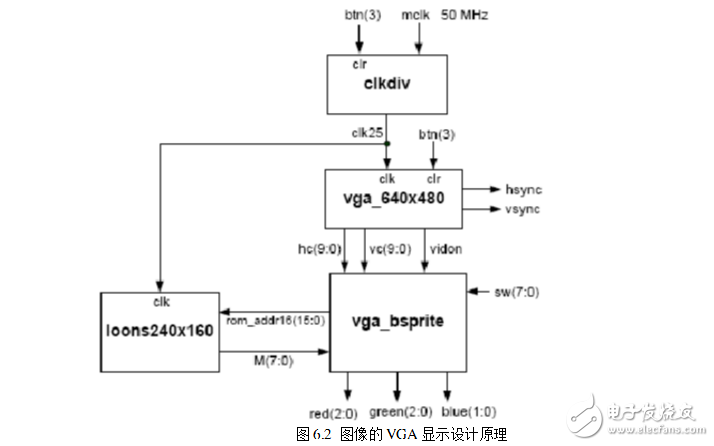

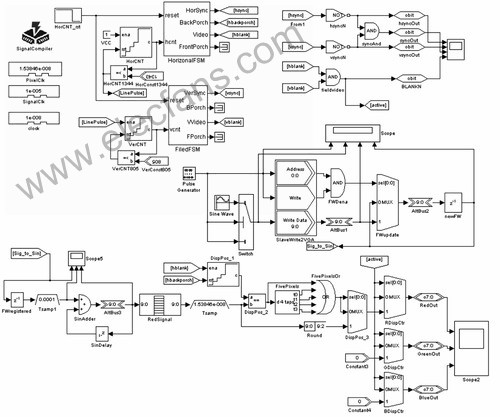

圖6.2給出了設(shè)計的結(jié)構(gòu)圖,從圖中可以看出該設(shè)計由clkdiv模塊,vga_640x480模塊,loons240x160模塊和VGA_bsprite模塊構(gòu)成。

設(shè)計的輸入信號包含:

1)btn(3):板上的按鍵輸入信號,系統(tǒng)清除信號; 2)mclk:板上50MHz的輸入信號,系統(tǒng)時鐘輸入信號; 3)sw(7:0):板上的撥碼開關(guān)輸入信號, 設(shè)計的輸出信號包含:

1)hsync:行同步信號,提供給VGA顯示器接口; 2)vsync:垂直同步信號,提供給VGA顯示器接口;

3)red(2:0):3位***信號,經(jīng)電阻網(wǎng)絡(luò)變換后提供給VGA顯示器接口; 4)green(2:0):3位綠色輸出信號,經(jīng)電阻網(wǎng)絡(luò)變換后提供給VGA顯示器接口; 5)blue(1:0):2位藍色輸出信號,經(jīng)電阻網(wǎng)絡(luò)變換后提供給VGA顯示器接口; 3.圖像存儲和尋址原理

產(chǎn)生的.coe文件將包含240x160=38,400個字節(jié)。ROM地址的計算: rom_addr16=ypix*240+xpix

其中xpix和ypix是圖像本地像素的位置,在實現(xiàn)該乘法時,使用移位相加的算法: ypix*240=ypix*(128+64+32+16);

紅,綠和藍輸出從loon240x160ROM M[7:0]輸出,其地址是根據(jù)上面的等式計算得到。

設(shè)計實現(xiàn)和驗證

1.打開ISE10.1,新建工程vga,設(shè)計參數(shù)選擇:芯片選擇Spartan3E XC3S1200E-4FG320,頂層設(shè)計選擇HDL,仿真器選項選擇Xilinx ISE Simulator。

2.新建名字為vga_bsprite,類型為VHDL module的設(shè)計文件,完成設(shè)計代碼輸入。 3.新建名字為clkdiv,類型為VHDL module的設(shè)計文件,完成設(shè)計代碼輸入。 4.新建名字為vga640x480,類型為VHDL module的設(shè)計文件,完成設(shè)計代碼輸入。 5.使用IMG2coe8.m(matlab程序),將圖片轉(zhuǎn)換為.coe文件(ROM核需要的保存象素信息的XILINX的存儲文件格式)。

6.新建名字為loons240x160,類型為IP(Core Generator & Architecture Wiazrd)的設(shè)計文件,在RAM & ROM中選擇ROM,寬度為8,深度為38400。

7.在處理窗口中,選擇并點擊Synthesis,工程進行語言檢查和綜合,確認設(shè)計正確。 8.新建文件名為vga_bsprite_top,類型為Implementation Constraints File用戶約束文件vga_bsprite_top.ucf。使用Nexys2板卡上的50MHz時鐘作為mclk輸入,撥碼開關(guān)SW(7:0)作為sw(7:0)的輸入,hsync,vsync,red,green,blue分別和VGA接口的行同步、垂直同步、紅色、綠色和藍色信號連接。按照板子設(shè)計在vga_bsprite.ucf文件完成引腳位置約束,保存并關(guān)閉該文件。

9.在管理窗口中雙擊Implement Design選項,完成設(shè)計實現(xiàn);

10.在管理窗口中右鍵點擊Generate Programming File,選擇屬性Properities,在Startup Option標簽欄中的FPGA Startup Clock選擇JTAG。

11.在管理窗口中雙擊Generate Programming File,生成比特流文件;

12.將Nexys2板卡和VGA顯示器連接,并上電后,在管理窗口中雙擊Configure Target Device,出現(xiàn)配置界面,選擇配置文件并下載到芯片中,確認下載成功。

13.對設(shè)計進行調(diào)試和驗證。

設(shè)計代碼

1.vga_bsprite.vhd代碼 library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity vga_bsprite is port (

vidon : in std_logic;

hc : in std_logic_vector(9 downto 0); vc : in std_logic_vector(9 downto 0); M : in std_logic_vector(7 downto 0); sw : in std_logic_vector(7 downto 0); rom_addr16 : out std_logic_vector(15 downto 0);

red : out std_logic_vector(2 downto 0); green : out std_logic_vector(2 downto 0); blue : out std_logic_vector(1 downto 0) );

end vga_bsprite;

architecture Behavioral of vga_bsprite is

constant hbp: std_logic_vector(9 downto 0) := “0010010000”; --Horizontal back porch = 144 (128+16) (96+48) constant vbp: std_logic_vector(9 downto 0) := “0000011111”; --Vertical back porch = 31 (2+29) constant w: integer := 240; constant h: integer := 160;

signal xpix, ypix: std_logic_vector(9 downto 0); signal rom_addr : std_logic_vector(16 downto 0); signal C1, R1: std_logic_vector(9 downto 0); signal spriteon, R, G, B: std_logic; begin

--set C1 and R1 using switches

C1 《= ‘0’ & SW(3 downto 0) & “00001”; R1 《= ‘0’ & SW(7 downto 4) & “00001”; ypix 《= vc-R1 when vc》=R1 and vc《R1+h xpix 《= hc-C1 when hc》=C1 and hc《C1+w

spriteon 《= ‘1’ when (((hc 》= C1 ) and (hc 《 C1 + w)) and ((vc 》= R1 ) and (vc 《 R1 + h))) else ‘0’;

process(xpix, ypix)

variable rom_addr1, rom_addr2: STD_LOGIC_VECTOR (16 downto 0); begin

rom_addr1 := (ypix & “0000000”) + (‘0’ & ypix & “000000”) + (“00” & ypix & “00000”) + (“000” & ypix & “0000”); -- y*(128+64+32+16) = y*240

rom_addr2 := rom_addr1 + (“00000000” & xpix); -- y*240+x rom_addr16 《= rom_addr2(15 downto 0);

end process;

process(spriteon, vidon, M) begin

if (spriteon = ‘1’ ) then

red 《= M(7 downto 5); green 《= M(4 downto 2); blue 《= M(1 downto 0); end if; end process; end Behavioral;

電子發(fā)燒友App

電子發(fā)燒友App

評論