課題研究的目的和意義

頻譜分析儀可以方便設計人員確定干擾信號的頻率范圍,以便選擇合理的濾波方案,但一般的頻譜分析儀體積較大,不便于工業現場使用,因此設計手持式頻譜分析儀,便于攜帶,功耗低,可長時間記錄數據,還可通過網絡遠程操作。

本頻譜儀的設計是以賽靈思的FPGA為核心,先在模擬前端驅動可編程放大器完成模擬信號的放大及電平遷移,然后按設定的采樣頻率驅動ADC完成數據采集,之后完成快速傅立葉變換,最后將結果顯示在4寸彩色液晶屏上,并按設定存儲數據或是通過網絡傳輸數據。

頻譜分析在生產實踐和科學研究中有著廣泛的應用。所謂頻譜分析就是將信號源發出的信號強度按頻率順序展開,使其成為頻率的函數,并考察變化規律。對于一個電信號的研究,我們可以分析它隨時間變化的特性,也可以由它所包含的頻率分量(即頻譜分布)來描述。通常把前者稱為時域分析,后者稱為信號的頻域分析。對信號進行頻譜分析,可以得到信號的頻率結構,了解信號的頻率成分或系統的特征。在此基礎之上,可實現對信號的跟蹤控制,從而實現對系統狀態的早期預測,發現潛在的危險并診斷可能發生故障的原因,對系統參數進行識別及校正。因此,頻譜分析是揭示信號特征的重要方法,也是處理信號的重要手段。而進行頻譜分析的儀器就是頻譜分析儀,它能自動分析電信號并在整個頻譜上顯示出全部頻率分量情況,確定一個變化過程(稱為信號)的頻率成分,以及各頻率成分之間的相對強弱關系。

頻譜分析儀的應用非常廣泛,而各行各業、各個部門對頻譜分析儀應用的側重點也不盡相同,對于需要在野外或測量現場來回測試、檢查的應用,體積較大,重量較重,便攜性不好的頻譜分析儀就顯得非常不方便,若有體積小、重量輕、便攜性好的頻譜分析儀,則會給其應用帶來很大的方便,更好的發揮頻譜分析儀的作用

對于頻譜分析儀的具體應用,主要有以下幾個方面:

(1)對信號參數進行測量

(2)用于信號仿真測量

(3)用于電子設備調試

(4)用于國防

課題研究的主要任務和預期目標

傳統頻譜分析儀主要依靠模擬濾波器來分開各頻率成分并進行頻率成分測量。為了提高頻譜分辨率,需要通頻帶很窄的濾波器,并且由于模擬濾波器中心頻率會隨時間、環境溫度“漂移”,因此制造高穩定度、高精度的的這種頻譜分析儀比較困難。

隨著FFT的提出,利用數字方法進行頻譜分析成為可能,這解決了很多傳統頻譜分析儀存在的問題,如“溫漂”等。實現FFT算法有利用軟件或利用純硬件等不同方法,利用軟件的方法可以在PC機或在DSP芯片上實現,其頻譜分析主要是依靠軟件計算來實現。而利用硬件方法的有FPGA或專用集成電路(ASIC)。隨著技術的不斷發展,目前FPGA芯片的性能和規模已達到很高的程度,用它來實現快速傅立葉變換(FFT)不僅成為可能,而且性能也有保證,對于大規模數字系統,也可以將其集成在一片FPGA芯片上,從而縮小產品體積,加強系統的可靠性和便攜性。因此,用FPGA來實現譜分析儀的功能是一個很好的選擇。

設計該手持式譜分析儀,基于FFT分析法的頻譜分析儀是優先考慮的方案。對于手持式譜分析儀,全球兩大測試儀器開發商,安捷倫和泰克公司都相繼開發出了相關產品,但價格昂貴。目前國內對這方面的研究也比較多,不過大多采用DSP芯片模式,FFT采用軟件實現,因此,在系統集成度和系統可靠性方面,將不會優于單芯片的FPGA硬件解決方案。故本課題選擇基于FPGA的便攜式頻譜分析儀的研究與設計,其中FFT由硬件電路實現。

本次設計的主要任務是設計一種基于FPGA的手持式頻譜分析儀。采用高性能FPGA實現基于FFT算法的頻譜分析處理,并將處理結果最終從液晶屏上顯示出來。首先研究傅里葉變換的特點,了解清楚快速傅里葉變換(FFT)與頻譜分析的關系,了解清楚窗函數對快速傅里葉變換(FFT)的影響以及混疊現象、頻譜泄露和柵欄效應對頻譜分析的影響,其次,了解清楚 FPGA的工作原理及其提供的可以利用的資源,特別是賽靈思系列的FPGA可供利用的資源。最后提出適合于FPGA實現的頻譜分析儀的系統方案。設計各個組成部分,整合整個系統,最后完成頻譜分析儀的設計工作。

?? 設計方案

根據工作原理,頻譜分析儀大致可分為模擬式和數字式兩大類,本設計是數字式頻譜分析儀,該分析儀先將所采集的信號通過一個低通濾波器進行濾波,然后將經濾波處理的模擬信號進行采樣量化,再通過放大器放大后送入Atlys Spartan@-6 FPGA 開發套件中進行數字信號處理,用快速傅立葉變換的方法求得信號的頻譜。

??? 方案論證:

1、FFT原理:

傅里葉變換就是信號的時域描述與頻域描述的某種變換關系。對于某一模擬非周期信號,存在著以下的傅里葉變換對

(1)

(1)

(2)

(2)

式(2)叫做傅里葉逆變換式。式(1)稱為傅里葉變換式,即函數![]() 是

是![]() 的傅里葉變換或傅里葉積分,函數

的傅里葉變換或傅里葉積分,函數![]() 反映了非周期信號

反映了非周期信號![]() 的頻譜。

的頻譜。

一個信號的傅里葉變換,其實質就是把該信號分解成許多不同頻率的正弦波之和。通過傅里葉變換可以得到信號的各種頻率成分,得到信號的頻譜。

式(1)是對頻率域而言的,它可以看作是時間函數![]() 在頻率域上的表示,頻率域上所包含的信息和時間域上所包含的信息完全相同,唯一的差別只是形式不同而已。通常,

在頻率域上的表示,頻率域上所包含的信息和時間域上所包含的信息完全相同,唯一的差別只是形式不同而已。通常,![]() 是一個復函數,即:

是一個復函數,即:

![]() (3)

(3)

![]() 和

和![]() 分別為實部和虛部,則幅度譜(即通常所說的頻譜)

分別為實部和虛部,則幅度譜(即通常所說的頻譜)![]() 表示為

表示為

![]() (4)

(4)

因此,頻譜分析儀的幅度譜(即通常所說的頻譜)可以通過(4)式得到。

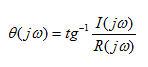

相位函數![]() 表示為

表示為

(5)

(5)

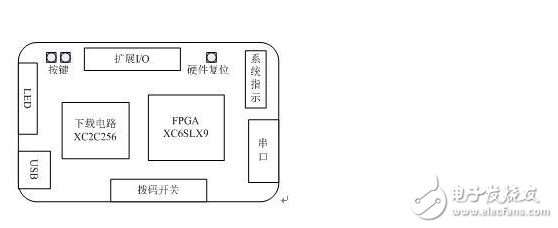

該式反映了信號的相頻特性。 在本設計中所使用的FFT處理模塊是有xilinx公司所提供的Atlys Spartan?-6 FPGA 開發套件,該板卡是新一代Xilinx FPGA學習板卡,不僅適合VHDL以及Verilog HDL代碼等傳統領域學習,還可用于新一代的SOPC領域學習。開發板以Spartan-6系列的XC6SLX9-TQ144芯片為核心,供電、下載與調試都通過板卡自身的USB接口完成,擴展了LED、GPIO、UART以及USB-JTAG電路,結構如圖2所示。此外,S6 CARD通過USB線完成板卡供電和調試,便于使用。該板卡結構圖如下所示:

其主要外設如下所列:

Xilinx XC6SLX9-TQG144 FPGA;

自帶USB調試與供電電路(無需下載線和電源),CY7C68013、XC2C256;

32M SPI FLASH M25P32;

MAX3232串口;

50MHz晶振;

按鍵、LED、撥碼開關

2、濾波器原理

系統從傳感器拾取的信號中,出來系統所需要的信息外,往往還包括許多噪聲以及其他與被測量無關的信號,所以在先期的電路中加入具有頻率選擇作用的濾波器,對所采集的信號進行濾波。

按照所處理信號的形式的不同,濾波器可分為模擬與數字兩大類。此外,濾波器的三種頻帶在全頻帶中分布位置不同,可實現對不同頻率信號的選擇,依此,濾波器可分為四種不同的基本類型:低通濾波器、高通濾波器、帶通濾波器、帶阻濾波器。另外根據濾波器中采用的元器件可以分為:LC無源濾波器、由特殊元件構成的濾波器、RC無源濾波器、RC有源濾波器。

在本設計中,所要采集的信號是交流電中的50HZ的頻率,直接對所要采集的信號進行濾波,所以所選用的濾波器是模擬低通濾波器,而且,如果在電路中引入具有能量放大作用的有源器件,如電子管、晶體管、運算放大器等,補充損失的能量,可使RC網絡像LC網絡一樣,獲得良好的頻率選擇特性。所以最終所選擇的濾波器是模擬低通RC有源濾波器。

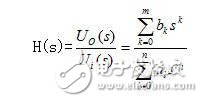

模擬濾波電路的基本形式為現行四段網絡,其特性可有傳遞函數表示如下:

定義為輸出與輸入信號電壓(或電流)的拉普拉斯變化之比。該式中s=σ+jω為拉普拉斯變量,各系數![]() 是由網絡結構與元件參數值決定的常數。根據現行網絡穩定性分析條件的要求,分母中各系數均應為正,并要求n≥m,n稱為網絡階數,也即濾波器的階數,反應電路的復雜程度。

是由網絡結構與元件參數值決定的常數。根據現行網絡穩定性分析條件的要求,分母中各系數均應為正,并要求n≥m,n稱為網絡階數,也即濾波器的階數,反應電路的復雜程度。

在傳遞函數中,令拉普拉斯變量s=jω,可以得到頻率特性函數H(jω):

H(jω)= =

= ,

,

頻率特性H(jω)是一個復函數,它的

A(ω)=  的幅值稱為幅頻特性。

的幅值稱為幅頻特性。![]() =

= ![]() 稱為相頻特性。

稱為相頻特性。

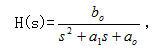

在本設計中選用的是二階濾波器,其傳遞函數的一般形式為:

,令

,令![]() 對應固有頻率,

對應固有頻率, 對應通帶增益,

對應通帶增益, 對應阻尼系數,將傳遞函數的一般形式改寫為規范的形式

對應阻尼系數,將傳遞函數的一般形式改寫為規范的形式 ,其幅頻特性與相頻特性分別為:

,其幅頻特性與相頻特性分別為:

A(ω)=

,

,

不同![]() 值下二階低通濾波器的幅頻特性和相頻特性如下圖所示:

值下二階低通濾波器的幅頻特性和相頻特性如下圖所示:

本設計中二階低通濾波器的設計平臺所使用的是microchip半導體公司所提供的濾波器設計平臺。

3、AD轉換原理:

按其工作原理的不同分為直接A/D轉換器和間接A/D轉換器兩種。直接A/D轉換器將模擬信號直接轉換為數字信號,這類A/D轉換器具有較快的轉換速度,典型的電路有并行比較型A/D轉換器、逐次比較型A/D轉換器。間接A/D轉換器則是先將模擬信號轉換成某一中間量(時間或頻率),然后再將中間量轉換為數字量輸出。此類A/D轉換器的速度較慢,典型電路有雙積分型A/D轉換器、電壓頻率轉換型A/D轉換器。 AD轉換芯片有很多,根據本次設計所采集的信號的需要,信號是交流電信號,選擇8位AD轉換器。芯片選擇的是Maxim公司所提供的MAX11662。其參數如下:VDD = 2.2V ——3.6V, VREF = VDD。

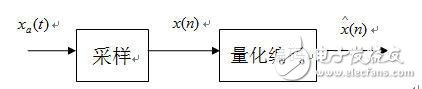

模數轉換器的原理框圖如下所示:

AD的轉換過程包括采樣、保持、量化和編碼四個階段。通過按等間隔T對模擬信號進行采樣,得到一串采樣點上的樣本數據,這一串樣本數據可看作時域離散信號(序列)。在本次設計中AD有8位,那么每個樣本數據用8位二進制數表示,即形成數字信號,因此,采樣以后到形成數字信號的這一過程是一個量化編碼的過程。

4、放大器原理:

通過低通濾波器所得到的信號可能很微弱,所以加一級前置放大器對所獲取的信號進行放大,以期能夠得到更易于處理的信號。將放大器前置的目的有兩個:①使小輸入信號不被后期電路的噪聲所淹沒;②要防止濾波器電路的噪聲被放大。

對于測量放大電路的基本要求是:①測量放大電路的輸入電阻應與傳感器輸出阻抗相匹配;②穩定的放大倍數;③低噪聲;④低的輸入失調電壓和輸入失調電流,以及低的漂移;⑤足夠的帶寬和轉換速率;⑥高共模輸入范圍和高共模抑制比;⑦可調的閉環增益;⑧線性好、精度高;⑨成本低等;

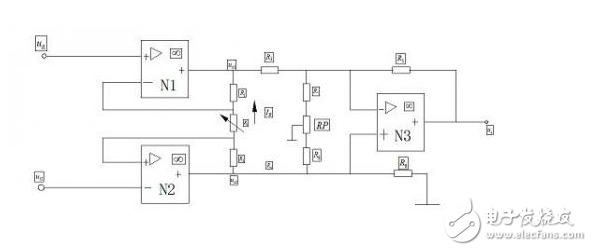

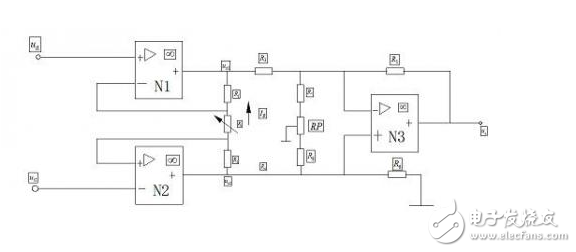

目前廣泛應用的是高共模抑制比放大電路,如下圖所示:

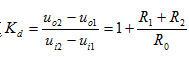

該共模抑制比電路由三個集成運算放大器組成,其中![]() 為兩個性能一致(主要是指輸入阻抗、共模抑制比和增益)的同相輸入通用集成運算放大器,構成平衡對稱(或稱同相并聯型)差動放大輸入級,

為兩個性能一致(主要是指輸入阻抗、共模抑制比和增益)的同相輸入通用集成運算放大器,構成平衡對稱(或稱同相并聯型)差動放大輸入級,![]() 構成雙端輸入單端輸出的輸出級,用來進一步抑制

構成雙端輸入單端輸出的輸出級,用來進一步抑制![]() 的共模信號,并適應接地負載的需要。

的共模信號,并適應接地負載的需要。

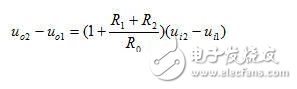

輸入級的輸出電壓,即運算放大器![]() 輸出之差為

輸出之差為![]() ,其差模增益

,其差模增益

由以上公式可知,當 性能一致時,輸入級的差動輸出及其差模增益只與差模輸入電壓有關,而其共模輸出、失調與漂移均在

性能一致時,輸入級的差動輸出及其差模增益只與差模輸入電壓有關,而其共模輸出、失調與漂移均在![]() 兩端相互抵消,因此電路具有良好的共模抑制能力,為消除

兩端相互抵消,因此電路具有良好的共模抑制能力,為消除![]() 偏置電流等得影響,通常取

偏置電流等得影響,通常取![]() 。

。

關于放大器采用的是LM386,LM386是一個用于在低電壓消費類應用設計的功率放大器。內部增益為20,輸入以地面為參考,而輸出被自動偏置到電源電壓的一半。靜態功耗只有24毫瓦,LM386是電池操作的理想選擇。

5、LCD輸出顯示原理

LCD為7段(或8段)顯示結構,故有7個(或8個)段選端,須接段驅動器,LCD的每個字段型要由頻率為幾十Hz到幾百Hz的節拍方波信號驅動。該方波信號加到LCD的公共電極和段驅動器的節拍信號輸入端。LCD顯示器的驅動接口電路分為靜態驅動和動態驅動兩種接口形式。

靜態驅動接口的功能是將要顯示的數據經過譯碼器譯為顯示碼,再變為低頻的交變信號,送到LCD顯示器。動態驅動接口通常采用專門的集成芯片來實現。一般采用主驅動器和從驅動器。主、從驅動器都采用串行數據輸入,主驅動器可以驅動48個顯示字段或點陣,每增加一片從驅動器可以增加驅動44個顯示字段或點陣。驅動方式采用1/4占空系數的1/3偏壓法。

本設計采用的動態驅動接口串行輸出。

電子發燒友App

電子發燒友App

評論