0 引言

高分辨率可見光相機(jī)是航天遙感最重要的手段之一,在商業(yè)領(lǐng)域和科學(xué)研究領(lǐng)域也都具有廣泛的應(yīng)用前景。高分辨率可見光相機(jī)的發(fā)展,已經(jīng)成為衡量一個(gè)國家科學(xué)技術(shù)水平的重要標(biāo)志。目前,用戶對地面分辨率的要求不斷提高,發(fā)展高分辨率光學(xué)遙感器成為世界各國在空間遙感領(lǐng)域研究的熱點(diǎn)。高分辨率可見光相機(jī)在國外發(fā)展較早,美國等發(fā)達(dá)國家已先后發(fā)展了高分辨率可見光相機(jī)。而我國高分辨率CCD相機(jī)的發(fā)展起步較晚,跟發(fā)達(dá)國家水平還有一定距離。影響相機(jī)分辨率的因素有很多,低噪聲視頻處理技術(shù)是實(shí)現(xiàn)相機(jī)高分辨率成像能力的關(guān)鍵之一。

1 CCD器件的噪聲及噪聲處理

CCD器件的噪聲主要有光子噪聲、散粒噪聲、肥零噪聲、轉(zhuǎn)移噪聲、暗電流噪聲和輸出噪聲[1],噪聲是影響CCD輸出圖像信號的主要因素。

在CCD應(yīng)用中為抑制和消除上述噪聲采取了以下措施[3]:

(1)在電路工藝上,增加直流電源的濾波,消除來自電源的干擾。縮短驅(qū)動電路與CCD器件的連線,降低時(shí)鐘感應(yīng)造成的尖峰干擾。數(shù)字地與模擬地分開,減少來自地線的干擾。

(2)對于轉(zhuǎn)移噪聲,采用將CCD電壓取反倒置或提高襯底電壓使CCD電壓倒置,可以消除界面態(tài)俘獲噪聲;降低運(yùn)行溫度可以使俘獲噪聲明顯成指數(shù)減小。

(3)對于散粒噪聲,利用相鄰像素(或相鄰行)積分平均器法去除或相鄰多幀取平均法。(4)暗電流噪聲:對于各像元暗電流較平均的CCD來說,如果在像元陣列的起始處有少量暗像元,則對其輸出信號采樣存儲,并與后續(xù)有效像元的輸出信號采樣值相減以去除暗電流噪聲。但必須保證兩次采樣的積分時(shí)間和溫度相同。

(5)對輸出噪聲可使用截至頻率為2f(f為CCD讀出頻率)的低通濾波器。另外還有相關(guān)雙采樣法(CDS)、雙斜積分法(DSI)、箝位切除法(CCS)等。

2 TDICCD視頻信號處理

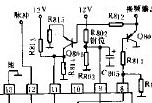

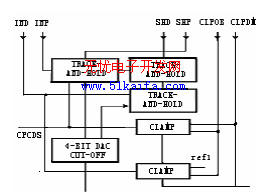

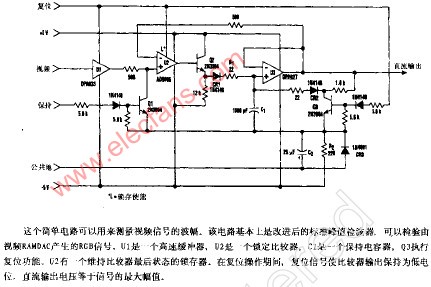

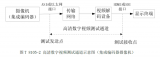

視頻處理電路主要是去除復(fù)位脈沖干擾和噪聲信號,由前置放大、相關(guān)雙采樣、箝位、濾波輸出、行緩存、輸出接口電路等環(huán)節(jié)組成。CCD視頻處理電路如圖2-1所示。

圖2-1 視頻處理電路原理框圖

CCD圖像傳感器接收的圖像信號經(jīng)過前置放大后成為差分信號輸出,經(jīng)過差分接收電路后變換成單端視頻信號,經(jīng)過CDS進(jìn)行相關(guān)雙采樣處理,得到“干凈”的視頻信號,再經(jīng)過低通濾波器濾除CCD驅(qū)動脈沖的尖峰干擾,由可控增益放大電路放大到A/D轉(zhuǎn)換器需要的電平,進(jìn)行A/D變換,成為數(shù)字圖像信號,并由緩存器(FIFO)交替緩存,由 LVDS接口芯片驅(qū)動后輸出。

在實(shí)際設(shè)計(jì)中采用了Philips公司的專用CCD相機(jī)接口芯片TDA8783來實(shí)現(xiàn)。

2.1 TDA8783簡介

TDA8783是PHILIPS公司的一種專用于CCD相機(jī)的10位模數(shù)接口芯片,主要由相關(guān)雙采樣電路(CDS)、增益控制電路(AGC)、箝位電路、低功耗10bit模數(shù)轉(zhuǎn)換器(ADC)組成[5]。可通過對片上三線串口編程實(shí)現(xiàn)片內(nèi)DACs分配來完成系統(tǒng)的各個(gè)功能。

2.2 前置放大電路

CCD輸出的信號電平隨積累電荷的增加而下降。為了進(jìn)行長距離傳輸和減少傳輸過程中引入的共模干擾,需要進(jìn)行放大和差分輸出。前置放大作用就是對CCD的輸出信號放大到足夠的幅度。

本系統(tǒng)中前置放大器與CCD輸出端之間采用交流耦合方式,消除了直流電平,有利于兩級之間的匹配,同時(shí)也消除了溫度等因素造成的零點(diǎn)漂移對傳輸信號的影響。當(dāng)然,采用交流耦合會造成信號中直流成份的丟失,這可由后續(xù)的箝位電路來恢復(fù)其直流分量。

2.3 相關(guān)雙采樣(CDS)

為保證輸出高信噪比的視頻信號,就必須對噪聲予以處理。相關(guān)雙采樣(CDS)技術(shù),不僅可以很好地濾除復(fù)位噪聲,而且對TDICCD傳感器的水平時(shí)鐘驅(qū)動及電源地線耦合串?dāng)_噪聲、輸出放大器的白噪聲和1/f噪聲等成份也有一定的濾除作用[4]。

在本系統(tǒng)中我們采用CCD相機(jī)接口芯片TDA8783實(shí)現(xiàn)CCD視頻信號處理,它內(nèi)部包含一個(gè)相關(guān)雙采樣(CDS)模塊,能夠有效地對CCD輸出信號進(jìn)行處理,很好地消除CCD的KTC噪聲等。CDS可編程帶寬為4~120MHz;輸入峰值電壓400mV;輸出放大器增益 為6dB。在使用中,可以通過對外部三線串口編程來選擇內(nèi)部控制DAC來實(shí)現(xiàn)CDS功能。當(dāng)串口移位寄存器地址A2A1A0=“001”時(shí),片內(nèi)4bit DAC工作控制CDS工作。本系統(tǒng)中采樣速率為4MHz,在此4 bit DAC輸入代碼設(shè)置為D3D2D1D0=“0001”。

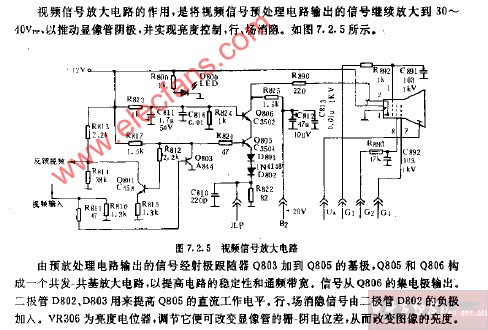

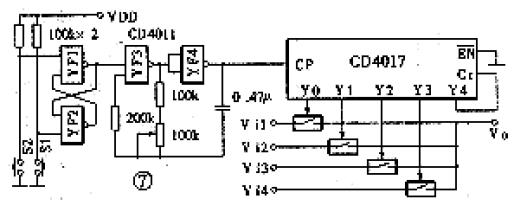

2.4 增益控制

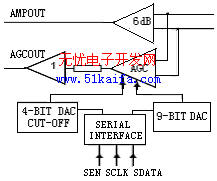

為了適應(yīng)不同亮度的目標(biāo),防止信號過弱或飽和,視頻信號處理電路中應(yīng)設(shè)計(jì)增益選擇放大電路。根據(jù)地面目標(biāo)的亮度,選用相應(yīng)的增益。CCD相機(jī)接口芯片TDA8783內(nèi)部集成了一個(gè)增益控制器(AGC),AGC輸出最小增益為4.5dB,最大增益為34.5dB。TDA8783的增益控制內(nèi)部邏輯關(guān)系如圖2-2所示。通過對三線串口編程來實(shí)現(xiàn)增益控制功能,當(dāng)串口輸入移位寄存器地址A2A1A0=“010”時(shí),9 bit控制DAC工作;當(dāng)其輸入代碼為“00”時(shí),為最小增益4.5dB,輸入代碼大于等于“319”時(shí),輸出增益為34.5dB。

圖2-2增益控制內(nèi)部邏輯關(guān)系圖

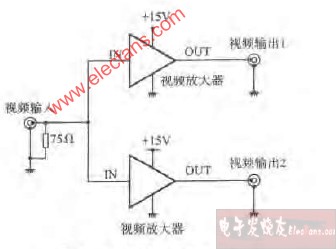

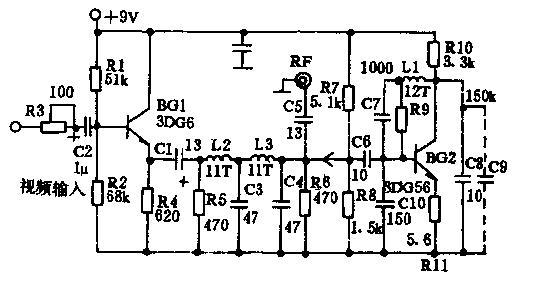

2.5 箝位與濾波電路

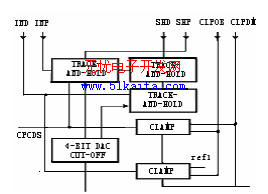

圖2-3輸入箝位內(nèi)部邏輯框圖

相關(guān)雙采樣處理電路輸出的信號混雜有采樣尖鋒干擾和其它高頻干擾信號,這就需要經(jīng)過低通濾波電路來濾除高頻干擾,并挑選出頻率較低的有用視頻信號。同時(shí),前置放大器采用交流耦合,負(fù)極性的交流信號經(jīng)過相關(guān)雙采樣去除噪聲,并以正極性的形式出現(xiàn)在相關(guān)雙采樣電路的輸出端。兩次采樣并相減的過程中會引入一些不必要的負(fù)極性成份。由于A/D轉(zhuǎn)換電路要求輸入的模擬量不能為負(fù)值,所以設(shè)置了箝位電路,去除低通濾波后信號中的負(fù)電平。

TDA8783中包含了帶寬控制電路和箝位控制電路,可以通過對片上三線串口編程來實(shí)現(xiàn)帶寬控制和箝位控制功能。TDA8783的箝位控制內(nèi)部邏輯關(guān)系如圖2-3所示。當(dāng)串口輸入移位寄存器地址A2A1A0=“001”時(shí),片上8 bit DAC工作來控制帶寬,此時(shí)D3~D0用于設(shè)置CDS帶寬,D4~D7用于設(shè)置AGC帶寬;當(dāng)串口輸入移位寄存器地址A2A1A0=“100”時(shí),片上10bit DAC工作來控制ADC(模數(shù)轉(zhuǎn)換器)的輸入箝位電平。

當(dāng)輸入代碼為“0”時(shí),VDACOUT(ADC箝位控制DAC輸出電壓)為1.5V;當(dāng)輸入代碼為“1023”時(shí),VDACOUT為2.5V。

2.6 模數(shù)轉(zhuǎn)換

視頻處理電路的輸出是模擬信號,為便于數(shù)據(jù)壓縮和傳輸,需要把它轉(zhuǎn)換成數(shù)字信號,模數(shù)轉(zhuǎn)換電路[2]在時(shí)序脈沖控制下把模擬視頻信號轉(zhuǎn)換成數(shù)字視頻信號,并按規(guī)定的格式驅(qū)動輸出。根據(jù)技術(shù)指標(biāo)要求,輻射量化等級為8bit,需要采用采樣速率大于10MHz的A/D芯片輸出。為了獲得高質(zhì)量的量化信號,需要認(rèn)真選擇性能參數(shù)較高的A/D轉(zhuǎn)換器。

?? 在本系統(tǒng)中, TDA8783集成了一個(gè)10bit A/D轉(zhuǎn)換器。該ADC(模數(shù)轉(zhuǎn)換器)的最大采樣頻率可以達(dá)到40MHz,最小時(shí)鐘脈寬12ns,占空比1:1,輸入峰值電壓2V,最大輸入電流120 ,+5V單電源供電,典型非線性誤差0.2LSB,最大采樣延時(shí)5ns。

在進(jìn)行A/D轉(zhuǎn)換時(shí),需要正確確定A/D轉(zhuǎn)換的采樣點(diǎn),也就是采樣脈沖在模擬信號上的位置(必須讓采樣點(diǎn)落在有效而且穩(wěn)定的模擬信號段上),否則有可能是采樣點(diǎn)落在信號的不穩(wěn)定位置,產(chǎn)生誤差信號,或是采樣點(diǎn)落在信號以外的位置,產(chǎn)生錯(cuò)誤信號。

2.7 數(shù)據(jù)輸出接口

數(shù)據(jù)輸出采用LVDS差分輸出,每通道的輸出信號有:一路像元時(shí)鐘,一路行同步信號和數(shù)字圖像信號。圖像數(shù)據(jù)、行同步和像元時(shí)鐘信號經(jīng)過接口電路驅(qū)動后輸出。接口芯片選用NS公司的DS90C031。

3 結(jié)論

(1)只有正確設(shè)計(jì)系統(tǒng)的時(shí)序驅(qū)動信號才能夠完成整個(gè)電路的協(xié)調(diào)工作;

(2)CCD輸出視頻信號的前置放大電路也應(yīng)盡量靠近傳感器,CCD視頻信號處理電路

間也應(yīng)盡量靠近,來減小傳輸過程中引入的噪聲干擾;

(3)CCD信號經(jīng)過視頻處理電路處理后,信號質(zhì)量得到了很大改善,滿足系統(tǒng)指標(biāo)要求。

電子發(fā)燒友App

電子發(fā)燒友App

評論