01車載SoC芯片現狀

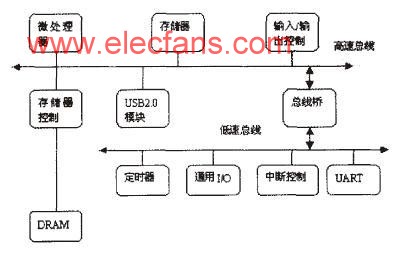

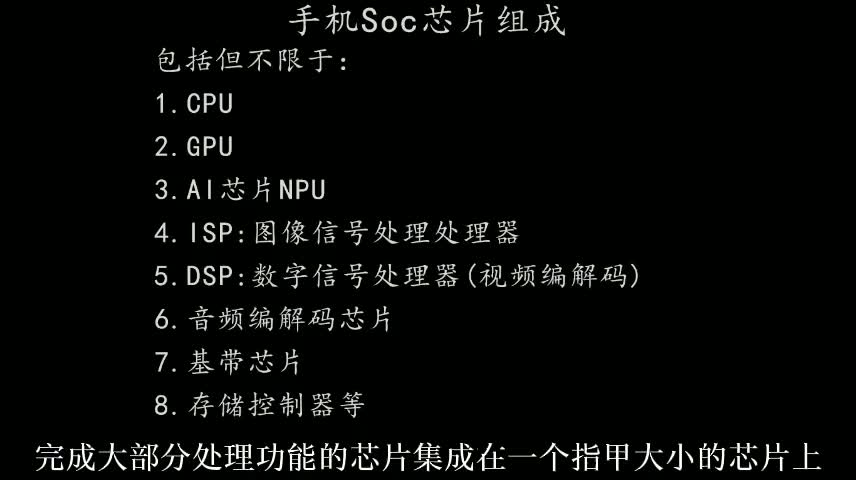

SoC的全稱叫做:System-on-a-Chip,中文的的意思就是“把系統都做在一個芯片上”。這個概念最先是從智能手機發展起來的,通過將CPU、GPU、內存、Modem,ISP,DSP,Codec等系統部件打包集成在一顆芯片內,手機廠商就不需要分別單獨采購這些功能芯片,從而帶來節省主板空間、成本和功耗的收益,這對追求輕薄、長時間續航的手機來說非常具有吸引力。

SoC在汽車上的首次應用,首先是在智能座艙領域。隨著智能座艙的發展,不僅需要強大的CPU算力來提高任務處理能力,強悍的GPU算力來處理視頻、圖片等非結構化數據,高效的AI 算力來滿足智能座艙的智能化交互體驗要求,高速的DSP算力實現大帶寬實時通訊,還需要能操作系統兼容手機生態,從而快速提升娛樂體驗。總之,智能座艙在4G通信、車載WFI、駕駛艙手勢識別、高品質音視頻處理、編解碼、圖像拼接等典型應用場景的需求跟智能手機的業務場景高度契合,所以憑借在消費電子、通信領域的技術實力和品牌優勢高通在2014年基于驍龍600平臺打造了驍龍620A車規級SoC芯片,取得了巨大的成功,截至目前高通的智能座艙SoC芯片已經演化到第四代SA8295。

在智能駕駛領域,海量幀圖像處理極其考驗芯片的并行計算能力,顯然擅長邏輯和數字運算能力的CPU無法滿足大量并行的簡單運算任務,因此,在自動駕駛上通常使用了集成CPU 和XPU(GPU/NPU/TPU)?的SoC 芯片。隨著智駕水平的發展,智駕SoC的算力也在不斷提升,目前已經量產AI算力最高的智駕SoC是英偉達Orin。

由于智艙與智駕的場景并不相同,帶來的算力側重點也不相同,所以智艙SoC和智駕SoC很長一段時間內平行發展。在今年9月份,高通和英偉達幾乎先后腳發布了自己的汽車超算芯片Thor(英偉達)和Snapdragon Ride Flex(高通),這兩款芯片都可以同時支持智艙和智駕功能。業內不禁驚呼,是不是艙駕一體芯片的時代就要到來了。對此,筆者認為真正實現艙駕一體還需要有很長的路要走。

首先,是智艙和智駕的功能安全等級不同,如何打造一款同時兼顧不同功能安全等級的OS是一個挑戰。

其次,真正艙駕一體要滿足算力靈活分配,而Thor目前通過靜態配置,一旦分配好了算力以后就無法根據場景進行切換。

第三,許多車企的組織機構里智艙與智駕分屬不同部門,在一顆芯片里如何分工協作也是一場挑戰,目前還沒有成熟的經驗可遵循。

因此,在未來一段時間內,智艙和智駕分屬兩個SoC還會是主流方案。

事實上無論是艙駕一體,還是智艙和智駕保持獨立發展,要想搞清楚車載SoC未來發展方向是什么,就必須要先回答一個問題,車載SoC芯片的發展方向是由什么來決定的?

02汽車智能化的挑戰

cao sir認為車載SoC芯片的發展方向是由整車電子電氣架構發展來決定的!

電子電氣架構是首先由德爾福公司提出的,集合汽車的電子電氣系統原理設計、中央電器盒的設計、連接器的設計、電子電氣分配系統等設計為一體的整車電子電氣解決方案的概念,按照業內普遍采納的博世定義,將電子電氣架構分為分布式架構、域集中式架構、中央集中式架構三大階段。近些年來,伴隨著汽車“新四化”的快速發展,許多車企都從分布式電氣架構邁進域集中式電氣架構,有的甚至一步跨越到中央集中式電氣架構,電子電氣架構整體呈現快速演進的態勢,這背后的原因就是汽車正面臨著“減重降本”、“智能網聯化”、“快速迭代”、“商業模式顛覆”四大挑戰。

1、“減重降本”挑戰,隨著汽車上智能化功能越來越多,傳統分布式架構會導致控制器數量繁多,成本和重量居高不下的問題。據統計,一輛基于傳統分布式電子電氣架構高端汽車的控制器高達70多個,整個電氣系統重量80Kg。

2、“智能網聯化”挑戰,在新四化浪潮下,一輛智能網聯汽車每天至少收集10TB的數據,對車輛內部、車輛與外界通訊提出更高要求,傳統以CAN通訊為主干網的電子電氣架構必然不能滿足要求。

3、“快速迭代”挑戰,傳統的低內聚、高耦合的電氣架構,可重用性、可拓展性差,開發周期長、成本高。未來市場是快魚吃慢魚的時代,傳統的分布式電子電氣架構低內聚,高耦合,新增加一個智能化功能需要許多控制器配合才能完成,不僅成本高,周期長。

4、“商業模式顛覆”挑戰,原先的賣車+售后的盈利模式,向互聯網“訂閱”盈利模式轉變,傳統面向信號的電氣架構顯然無法支持這種“訂閱”模式,所以衍生出了面向服務的SOA電氣架構。

03車載SoC芯片的發展方向

為了滿足上面的四大挑戰,面向未來的新型電氣架構必須具備“低能耗”、“可信可靠”、“高集成”、“可重用”、“可成長”、“高性能”、“低耦合”、“高開放”的八大核心特征。其中“高性能”、“低能耗”、“高集成”、“可信可靠”決定了車載SoC芯片的發展方向。

“高性能“

由于多屏互聯、智能交互、智能駕駛等場景化功能對芯片性能有著極高要求。近幾年來,智能座艙芯片的CPU算力提升相當明顯, 僅用了不到7年的時間,從過去的數KDMIPS提升到如今的100多KDMIPS,。隨著自動駕駛的發展,智駕芯片的AI算力也在大幅提升,通常業內認為實現L2級自動輔助駕駛需要的算力在10 TOPS以下,L3級需要30~60 TOPS,L4級需要超過300 TOPS,L5級需要超過1000 TOPS,甚至4000+ TOPS。

“低能耗“

據初步估計,一輛新能源車在CLTC工況下,每增加50w功耗會帶來8~10Km的續航里程損失,因此,新型電子電氣架構上對芯片能效比提出了更高的要求。降低能耗除了提升工藝納米水平以外,從通用芯片轉為某類算法“量身定做“ASIC芯片是一條前景廣闊的途徑。當前自動駕駛芯片使用GPU+FPGA的解決方案。未來算法穩定后,ASIC將成為主流。現階段,主流產品的能效比已經由最初?0.8TOPS/W(EyeQ4)、1TOPS/W(Xavier),進化到了 4.44TOPS/W(英偉達 Orin)、4.8TOPS/W(地平線征程 5),未來主流產品功耗至少在 6TOPS/W 以上。

“高集成“

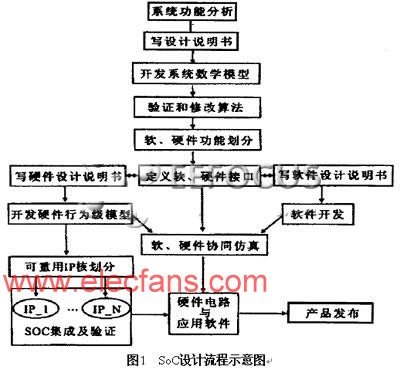

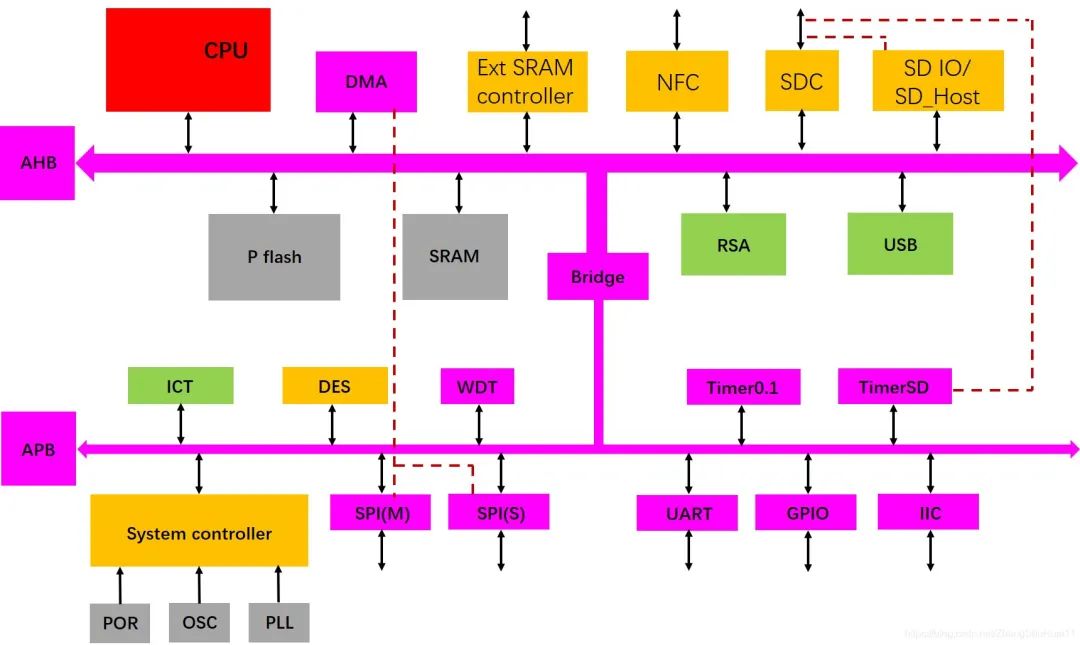

汽車電子電氣架構(E/E架構)逐漸從傳統的分布式向集中式演進。在集中式E/E架構下,新增的域控制器集成了更多的功能,主控芯片若要與其職能相匹配,則算力、性能等必須隨之提升。在此趨勢下,汽車芯片從通用型、分散化的單一功能芯片(MCU)開始逐步轉向定制化、集成化的多功能SoC(System on Chip)芯片。SoC是系統級芯片,將系統關鍵部件集成在一塊芯片上,提升性能的同時可有效地降低系統產品的開發成本,縮短開發周期,提高產品的競爭力。未來在中央集中式電氣架構下,智艙SoC和智駕SoC芯片存在融合的趨勢。

“可靠可信”

隨著功能安全和網絡安全的要求不斷提高,SoC 芯片可靠可信是首要考慮的問題。可靠性技術的實現都是以容錯為基礎, 容錯技術主要是依靠資源的冗余和系統重構資源的組織來完成。冗余主要包括硬件冗余、軟件冗余、時間冗余、信息冗余等。硬件冗余是在常規的硬件功能設計之外再另加一些備用的附加的硬件, 當常規硬件發生錯誤時備用硬件起作用, 使系統仍然能夠正常工作; 軟件冗余是增加一些額外的用于檢錯糾錯的程序, 當運行出錯時程序能夠自行進行檢錯糾錯; 時間冗余是為某一指令或一段程序開辟額外的時間讓其重復執行; 信息冗余是增加信息的多余度, 使其自己具有檢錯糾錯的能力。

03國產SoC如何破局?

短期來看,憑借先發優勢、朋友圈規模和迭代速度,高通和英偉達分別在智能座艙領域和智能駕駛領域尚未有人能與其棋逢對手,國產SoC如何在強敵環伺的競爭格局中破局,并與他們同臺競技?

首先要以緊緊圍繞以用戶需求為中心,打造創新管理流程。以自動駕駛AI芯片為例,當前市場上許多芯片公司都是基于自己算法開發的IP,用戶買他們芯片就要同時使用他們的算法,有的芯片公司的產品甚至無法支持CNN+Transfomer算法,還有的芯片公司則會持續跟蹤前言視覺學習算法,在設計過程中確保兼容,另外還通過軟硬件協同設計,并提供工具鏈支持客戶構筑自己的算法IP,從而為客戶打造專屬的運行效率更高的智駕SoC。

其次是打造高水平的技術團隊。芯片行業本身就是一個系統性的工程,對專業學科的要求非常高且廣泛包含但不限于數學、化學、物理、圖像、光學等等。復雜性和廣泛程度,更考驗各位工程師們扎實的理論基礎和出色的工程落地能力!因此與之對應的工作內容合理劃分和優質的人才是芯片設計公司的重要靈魂,也是打造芯片正向開發的能力的基石。

第三,對智艙芯片來說,隨著車內元宇宙、非觸摸式交互,艙泊一體等一系列智能座艙場景落地,智能座艙SoC的算力發展整體向PC看齊趨勢,當前市場上主流的座艙芯片未來將會被更高算力的SoC所取代,在新舊交替的過程中追求極致算力的智艙SoC芯片將會獲得市場青睞。

第四,對智駕AI芯片來說,算力在不斷提升同時帶來了功耗、成本和面積的大幅提高,因此單純依靠芯片算力堆疊是無法解決智能駕駛系統計算平臺的支撐問題,筆者認為算力的無限膨脹不會是未來的趨勢,與動輒上千TOPS的算力相比,精準高效的AI算力以及更好的軟件是培訓顯得更為重要,為車企節約開發周期與成本。

狄更斯在《雙城記》中說過:“這是一個最好的時代,也是一個最壞的時代。”,在新型電子電氣架構變革的過程中,車載SoC市場格局將發生深刻變化,未來到底誰主沉浮,目前下結論還為時尚早,但是cao sir認為,那些圍繞用戶需求為中心,深耕技術的芯片企業,一定會有更多的機會!

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論