NVIDIA DRIVE AGX 是一個可擴展的開放式自動駕駛汽車計算平臺,充當自動駕駛汽車的 大腦。作為同類產品中硬件平臺的佼佼者,NVIDIA DRIVE AGX 為功能安全的人工智能自動駕 駛提供高性能、高能效的計算。硬件方面,NVIDIA DRIVE 嵌入式超級計算平臺處理來自攝像頭、普通雷達和激光雷達傳 感器的數據,以感知周圍環境、在地圖上確定汽車的位置,然后規劃并執行安全的行車路線。軟件方面,NVIDIA DRIVE AGX 具備可擴展和軟件定義特性,平臺能夠提供先進的性能, 助力自動駕駛汽車處理大量傳感器數據,并做出實時駕駛決策。開放式 NVIDIA DRIVE 軟件 棧還可幫助開發者使用冗余和多樣化的深度神經網絡 (DNN),構建感知、建圖、規劃和駕駛 員監控功能。通過持續迭代和無線更新,該平臺變得日益強大。同時,開放式 NVIDIA DRIVE SDK 為開發者提供了自動駕駛所需的所有構建塊和算法堆棧。該軟件有助于開發者更高效地 構建和部署各種先進的自動駕駛應用程序,包括感知、定位和地圖繪制、計劃和控制、駕駛 員監控和自然語言處理。本文將分幾個章節以當前應用最為廣泛的主流英偉達芯片 Orin x 為例,分別從硬件和軟 件兩個方向來說明如何進行從軟到硬件級別的開發和應用。 ?

1.英偉達內部架構設計

以 Orin-x 為例,其中的 CPU 包括基于 Arm Cortex-A78AE 的主CPU 復合體,它提供通用高速計算能力;以及基于 Arm Cortex-R52 的功能安全島(FSI),它提供了隔離的片上計算資源, 減少了對外部 ASIL D 功能安全 CPU 處理的需求。

GPU 則是 NVIDIAAmpere GPU,為 CUDA 語言提供高級并行處理計算能力,并支持多種工具, 如 TensorRT,一種深度學習推理優化器和運行時,可提供低延遲和高吞吐量。Ampere 還提供最先進的圖形功能,包括實時光線跟蹤。域特定硬件加速器(DSA)是一組專用硬件引擎,旨在從計算引擎中卸載各種計算任務,并以高吞吐量和高能效執行這些任務。

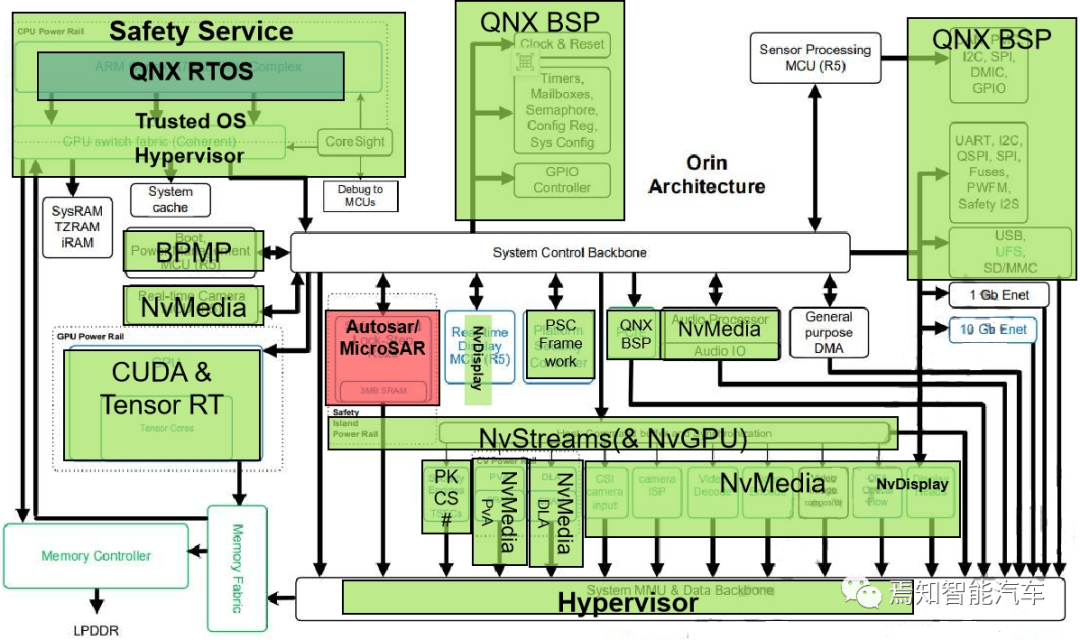

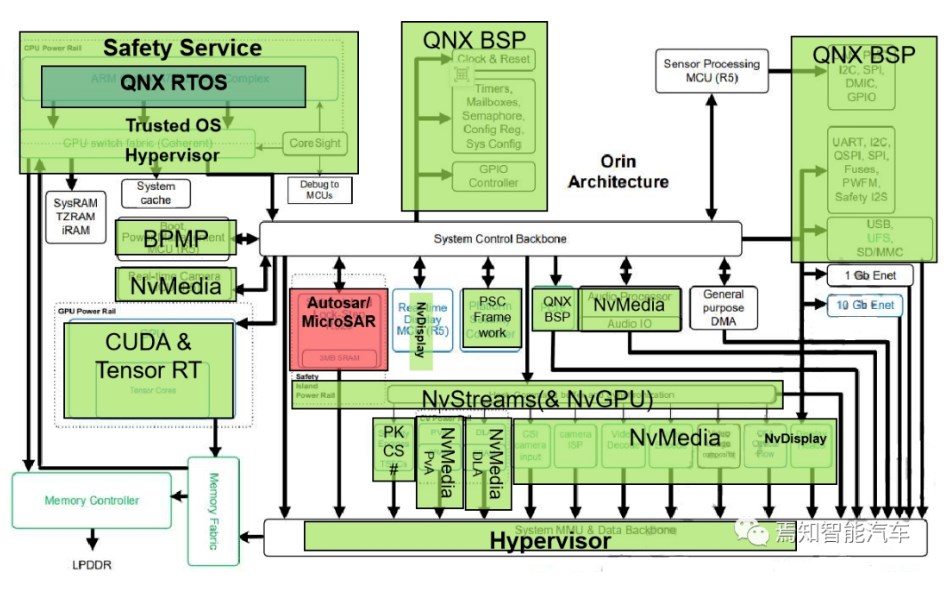

下圖顯示了 SoC 的高級架構,分為三個主要處理復合體:CPU、GPU 和硬件加速器。

? 整個芯片內部架構設計主要是按分塊進行功能設計區分。包括操作系統底層軟件QNX BSP(時鐘Clock源&系統重啟、CAN/SPI/I2C/GPIO/UART控制器、配置寄存器、系統配置)、實時運行系統QNX RTOS、Nv多媒體處理模塊(傳感器處理模塊MCU(R5)、PVA、DLA、Audio Processor、MCU R5配置實時相機輸入)、經典Autosar處理模塊(用于Safety Island Lock-Step R52s)、安全服務Safety Service(ARM Cotex-A78AE CPU Complex、CPU Switch fabric Coherent、信息安全PSC)、神經網絡處理模塊(CUDA & TensorRT)。

2.基于英偉達芯片的自動駕駛典型架構設計

常規的 SOC 系統架構通常是包含有常規的 SOC+MCU 雙芯片甚至三芯片的方式進行設計的。SOC 由于計算性能上的優勢,一般在前端感知、規劃中的計算應用場景比 MCU 更好。

MCU 由于具備較高的功能安全等級,可以作為控制執行的校驗輸出。業界對于英偉達芯片是否可以單純作為類似 TDA4 一樣的超異構芯片而獨立承擔任務, 一直都是褒貶不一的。原則上,從無論 Xavier 還是 Orin 系列,英偉達系列芯片設計都兼具 豐富的 AI 和 CPU 算力能力。考慮 L2+級別以上的自動駕駛系統開發而言,這種能力都是可 以完全適配整個方案設計的。

那么,行業內是否這樣主推相應的設計方案了呢?答案是沒有。

在英偉達 Datasheet 中關于最新安全需求中,針對 Orin 系列芯片的架構設計推薦方案中, 仍然需要使用特定的 MCU 用于失效分析和風險評估,這樣就可以及時的定位到系統的嚴重 故障,從而確保滿足由 ISO26262 標準所定義自動駕駛安全完整性能力要求(這塊后續會單 獨講解)。同時,考慮到整個域控的電源管理,接入外置 MCU 也可以很好的提升其電源管 理能力,包括對進入睡眠模式的進入退出等等。

如上所設置的 MCU 在一定程度上也可以被稱之為 Safe MCU(SMCU),開發系統過程 中需要使用一些安全等級較高的 MCU(一般需要達到 ASIL D 等級),如英飛凌 Aurix TC 系 列,瑞薩的 RH850 系列都可以充當 MCU 實現對 Orin 的 SMCU 接入。這樣的 SMCU 實際是可 以充當整個系統開發的電源控制和嚴重失效故障規避的。

如上圖所示表示了基于英偉達芯片設計系統架構的三層失效安全框架。整體上講,該架 構從 SOC 層的基礎服務、操作系統、虛擬機、實施運行環境再到 MCU 的實時運行環境幾個 方面分別實現三層級失效安全保護。SOC 層和 MCU 層分別在 NvIVC、NvIPC、SPI/Error Pin 層 級上進行健康和獨立的看門狗監控。其中,SOC 內部本身會承載一部分鎖步安全校驗 Lockstep FSI , 并 在 核 心 CPU 復 合 體 CCPLEX ( Carmel CPU complex running the capture stack and applications.表示運行捕獲堆棧和應用程序的 Carmel CPU 復合體)上運行虛擬機 Hypervisor,CPU 核上采用具備高功能安全等級的 QNX 操作系統,完成應用軟件看門狗、中間件、應用 層軟件以及驅動軟件的資源調度。當然,對于實時運行系統而言,還是運行在標準的 Autosar 上。

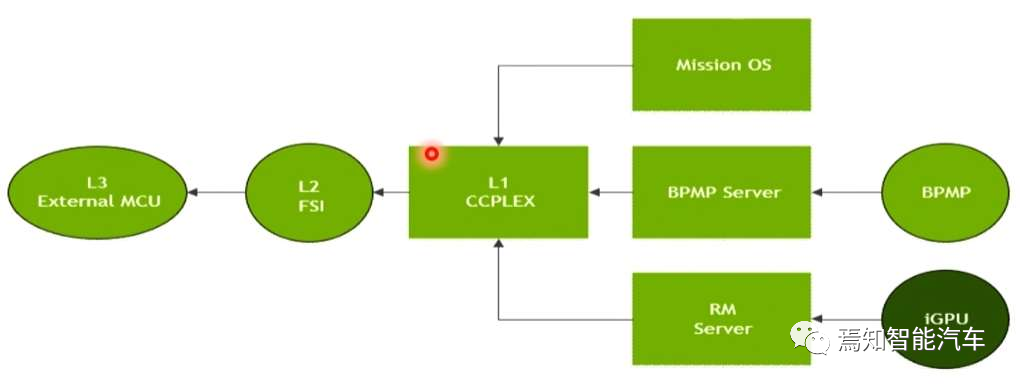

如下圖所示的安全架構表示了外置 MCU 如何支持在 SOC 上的啟動數據流,并通過一個 標準錯誤報告/傳播數據流來進行有效的安全啟動。其中,整個程序與數據引導加載過程包 括三個層面:Boot L1 級 CCPLEX、Boot L2 級 FSI、Boot L3 級 External MCU。

?啟動鏈路設計

在 L1 級程序啟動過程中,底層啟動包括利用“引導和電源管理處理器(BPMP)”終端 (一個較小的 ARM 內核位于系統的核心位置)加載底層啟動程序到 BPMP 服務器,由虛擬機Hypervisor 或操作系統 Safety OS 對相應的啟動程序文件進行調用。總體上,BPMP 的 Cortex-R5 可以實現:

1、鎖步核配對

2、Arm 7-R ISA

3、向量中斷支持:基于菊花鏈 Arm PL192 矢量中斷控制器(AVIC)

5、完備指令和數據緩存(其中涉及 32KB 指令緩存 I-Cache 和 32KB 數據緩存 D-Cache)

6、Arm 處理器修正

同時,底層 iGPU 核也會由 RM 集成式服務器驅動起來。最終在第一層加載啟動程序 L1 CCPLEX(在 NVIDIA 中稱為 CPU Complex 即高性能 64 位 Arm 內核)中完成操作系統任務 調度、引導管理程序加載、RM 服務器驅動 GPU 核等各項專業任務。

此外,L2 級主要還涉及前序文章中提到的功能安全島校驗 FSI。文章后續會單獨進行說 明。

最后,外掛的 SMCU 可以另外在做一層安全保護和啟動管理配置。這樣就可以從安全的 角度完整的驅動整個芯片工作。

3.功能安全島設計原理

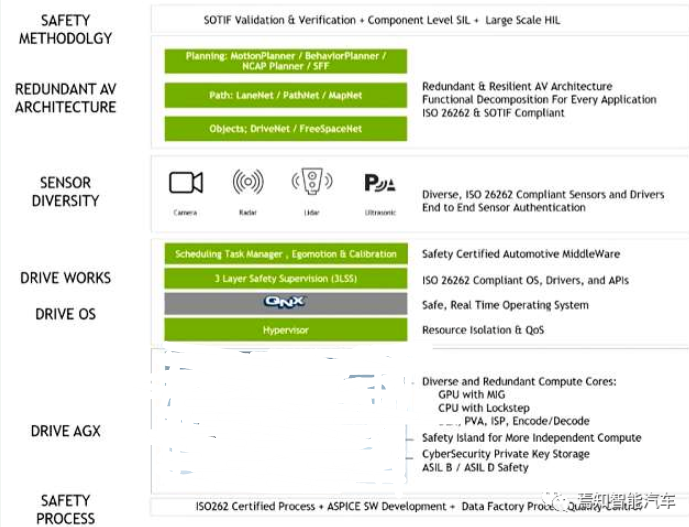

如圖2顯示了如何在英偉達系列芯片中加載 FSI 及底層相關模塊驅動引導程序。英偉達系列芯片在功能安全設計上,Orin 系列通過制定目標實現 ASIL D 系統能力設計和ASIL B/D 隨機錯誤管理能力設計。包括基于 SOC 芯片硬件的 ASIL 分解需求到各個核,確保核間設計一致性可以滿足 ASIL D 需求,并應用標準的 ASIL D 開發流程到整個功能安全設計中,從底之上分別對安全流程、Drive AGX、操作系統 Drive OS、Drive Work、傳感器、冗 余架構設計、安全策略幾個方面分別進行相應的安全設計。

? 英偉達系列芯片的功能安全島(FSI)是一個包含 Cortex-R52 和 Cortex-R5F real 的處理器集群,并具有專用 I/O 控制器的時間處理器的核心。例如,Orin-X 中的 FSI 模塊具有自己的電壓軌、振蕩器和PLL、SRAM,以確保與 SOC 內部的其他模塊相互作用最小,并實現如上模塊相互之間無干擾。

Orin-x 系列 FSI 功能包括:

Cortex-R52 處理器,也稱為安全 CPU,具有 DCLS(雙核鎖步)模式下的 4 個內核(共 8 個物理內核),可運行經典 AUTOSAR 操作系統,實現錯誤處理、系統故障處理和其他客戶工作負載,綜合性能約為 10KDMIPs。

Cortex-R5F 處理器,也稱為加密硬件安全模塊(CHSM),用于通過 CAN 接口運行加密 和安全用例,如安全車載通信(SecOC)。

整個FSI機制上總體包含有如下的一些安全指令和控制接口信息:

1、安全和 CHSM CPU 每個核心的緊密耦合內存、指令和數據緩存。

2、安全島上總共有 5MB 的片上專用 RAM,以確保代碼執行和數據存儲可以保持在 FSI 內。

3、島上有專門用于與外部組件通信的專用 I/O 接口。包含1個 UART,4 個 GPIO 口。

4、硬件安全機制,如 FSI 內所有 IP 的 DLS、CRC、ECC、奇偶校驗、超時等。

專用熱、電壓和頻率監測器。

5、邏輯隔離,確保與 SoC 的其他部分有足夠的錯誤恢復時間FFI。

FSI的實例解析1:

這里本文將通過一個例子說明設計 FSI 為目的描述相應的錯誤處理機制,其中包括對如下過程的處理模式:

1、在基于 Xavier 的平臺上調試 CSI 捕獲錯誤的各種方法。

2、如何確定使用哪種方法進行調試。

3、如何識別錯誤。

4、錯誤的可能根本原因。

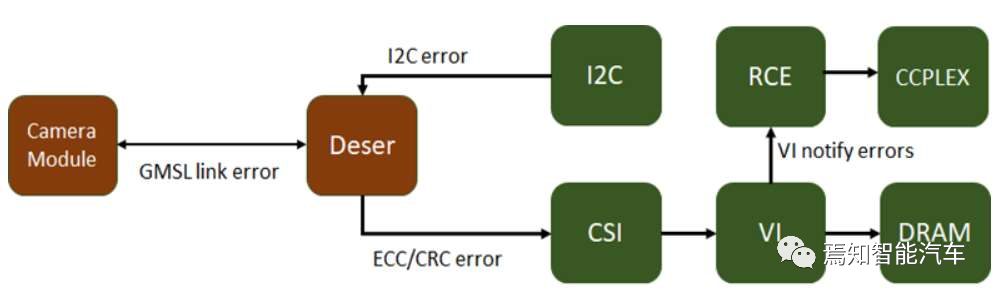

相機捕獲過程中可能發生錯誤的圖層如下:

? 每當解碼在 SoC CSI 接口接收到的 CSI 數據包并將原始幀數據寫入內存遇到錯誤時,VI 硬件引擎就會將這些錯誤通知給RCE。在 CCPLEX 上運行的捕獲堆棧可以從 RCE 查詢捕獲狀態并顯示:CSI 數據流的 ID、發生錯誤的 VC ID、錯誤類型、每個錯誤類型的詳細錯誤。錯誤狀態為確定根本原因和確定后續步驟提供了一個很好的起點。如果 VI 引擎沒有成功捕獲幀,也沒有遇到錯誤并向 RCE 報告錯誤,則會顯示幀啟動或結束超時錯誤消息提示。 ? 這可能是由于以下兩個原因之一: ?

1、解串器不是流數據。

2、VI 通道未配置為捕獲正確的數據類型/VC id。

4.英偉達系列芯片如何考慮信息安全

對于英偉達芯片來說,有效的保證信息安全主要是通過兩個層面:其一是信息安全芯片內核模塊Tegra。盡管這一芯片曾經在2018年也出現過安全漏洞。有極端黑客利用NVIDIA Tegra X1芯片中的漏洞破解了Switch主機,此漏洞允許任何人在其上運行任意代碼,這意味著自制系統和盜版軟件可以隨意運行。然而,通過不斷地內部優化,英偉達已經在很大程度上完成了漏洞修補。

比如,在使用相同 Tegra X1 CPU 的初始 Nintendo Switch 控制臺上,在 ROM 引導加載程序中發現了一個漏洞,就通過恢復模式和緩沖區溢出實現修復。NVIDIA 可以使用內置可編程保險絲將補丁存儲到內部 ROM 中解決這類修復問題。這樣既考慮了薄弱環節又兼顧了安全性,減少代碼 bug。

又如,硬件設計的性質意味著某些內部硬件模塊無法被 CCPLEX 訪問,只有 BPMP 能夠操縱它們。包括 u-boot 在內的所有低級引導步驟都可以通過簽名的二進制文件來確保安全。它們的密鑰可以存儲在 CPU 中的一次性可編程保險絲中。U-boot 本身可以配置為使用簽名的FIT 映像,從而提供一個安全的引導鏈,一直到 Linux 內核。初始 ROM 引導加載程序和 TegraBoot 也都支持完全冗余的引導路徑。

Tegra是英偉達芯片中特有的信息安全芯片內核,Tegra Security Controller(TESC)是一種信息安全子系統,他有自己的可信任根ROM、IMEM、DMEM,Crypto 加速器(AES、SHA、RNG、PKA),關鍵鏈路和關鍵存儲。TSEC 提供了一個片上TEE(可信任執行環境)可以運行NVIDIA-標記的為處理代碼。TSEC是一種典型的安全視頻回放解決方案,下載信息安全運行所需的HDCP1.x 和2.x連接授權和完整的線端連接檢測。

整體來說,TSEC可以支持:

1)線端HDMI 1.4上的HDCP 1.4和 線端HDMI 2.3上的HDCP 2.0 2.1;

HDCP連接管理沒有暴露受保護的內容,也無需運行在CPU上的軟件鑰匙。用于 HDCP 鏈路管理的兩個軟件可編程獨立指令隊列(最多可容納 16 條指令);整個芯片能夠獨立于播放器在 HDCP 狀態檢查失敗時禁用 HDMI 輸出。

2)平臺安全控制器;

他是一個高安全子系統,他可以保護和管理SOC中的資產(鑰匙、保險絲、功能、特性),并提供可信任的服務,提升自由的抵御對 SOC 的攻擊,并可以提高對子系統本身的軟件和硬件攻擊的保護水平。

3)鑰匙管理和保護;

PSC 將是唯一可以訪問芯片中最關鍵秘鑰的機制。該子系統代表了 Orin-x 中最高級別的保護,并且該子系統本身對各種軟件和硬件攻擊具有高度的彈性。

4)授信服務;

例如,在 SOC 安全啟動期間,主要的 PSC 服務可以完成有效的安全身份驗證、提供額外的密鑰/ID/數據、密鑰訪問和管理、隨機數生成和授信的時間報告。

5)信息安全監控。

PSC 將負責定期的安全管理任務,包括持續評估 SOC 的安全狀態,主動監控已知或潛在的攻擊模式(例如,電壓故障或熱攻擊),降低硬件攻擊風險,并在檢測到有攻擊的情況下采取有效的措施。PSC 將能夠接受各種軟件更新來作為解決方法,以提高現場系統的穩健性。

其二,是安全引擎(SE)的應用。他可以為加密算法提供硬件加速。

安全引擎SE中有兩種情況針對軟件使用是有用的。其一,TZ-SE只能被可信任區域軟件所訪問。其二,NS/TZ-SE可配置用來被可信任的軟件區域或非安全軟件所訪問。安全引擎SE可以為各種加密算法提供硬件加速以及硬件支撐密鑰保護。SE提供的加密算法可以被軟件用來建立加密協議和安全特性。所有加密運算都是基于國際標準技術協會NIST批準的加密算法。

英偉達的安全引擎SE可支持包含如下的所有信息安全保障能力:

NIST合規的對稱以及非對稱加密和哈希算法、側信道對策(AES/RSA/ECC)、獨立并行信道、硬件鑰匙訪問控制(KAC)(基于規則,增強硬件訪問控制的對稱鑰匙)、16xAES,4xRSA/ECC鑰匙孔、硬件密鑰隔離(僅針對AES鑰匙孔)、讀保護(僅針對AES鑰匙孔)、硬件鑰匙孔函數、密鑰包裝/解包功能(AES->AES鑰匙孔)、鑰匙從鑰匙孔分離(KDF->AES鑰匙孔)、隨機鑰匙生成(RNG->AES鑰匙孔)。

5.總結

本文從整個英偉達芯片的核心架構、功能安全、信息安全等角度完整的剖析了其在應用過程中的主要特性和策略優勢。對于如何利用英偉達系列芯片進行開發而言,充分的考慮其內部架構并結合其功能安全和信息安全能力對于整個開發調優都顯得尤為重要。后續文章將分別從硬件開發和軟件開發的角度分別進行詳細的策略剖析。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論