芯粒在汽車市場(chǎng)重新受到關(guān)注,不斷發(fā)展的電氣化和激烈的競(jìng)爭(zhēng)迫使公司加快設(shè)計(jì)和生產(chǎn)計(jì)劃。

電氣化已經(jīng)點(diǎn)燃了一些最大、最知名的汽車制造商的熱情,面對(duì)非常短的市場(chǎng)窗口和不斷變化的需求,這些制造商正在努力保持競(jìng)爭(zhēng)力。與過(guò)去不同的是,汽車制造商通常采用五到七年的設(shè)計(jì)周期,而當(dāng)今汽車的最新技術(shù)很可能在幾年內(nèi)就被認(rèn)為過(guò)時(shí)了。如果他們跟不上,就會(huì)有一批全新的初創(chuàng)公司生產(chǎn)廉價(jià)汽車,這些汽車能夠像軟件更新一樣快速地更新或更改功能。

但軟件在速度、安全性和可靠性方面存在局限性,而定制硬件正是許多汽車制造商現(xiàn)在努力的方向。這就是芯粒的用武之地,現(xiàn)在的重點(diǎn)是如何在大型生態(tài)系統(tǒng)中建立足夠的互操作性,使之成為一個(gè)即插即用的市場(chǎng)。實(shí)現(xiàn)汽車芯粒互操作性的關(guān)鍵因素包括標(biāo)準(zhǔn)化、互連技術(shù)、通信協(xié)議、電源和熱管理、安全性、測(cè)試和生態(tài)系統(tǒng)協(xié)作。

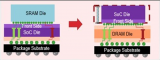

與板級(jí)的非汽車應(yīng)用類似,許多設(shè)計(jì)工作都集中在芯片到芯片的方法上,這推動(dòng)了許多新穎的設(shè)計(jì)考慮和權(quán)衡。在芯片級(jí),由于設(shè)計(jì)性能要求的提高,各種處理器、芯片、存儲(chǔ)器和 I/O 之間的互連變得越來(lái)越復(fù)雜,從而引發(fā)了一系列標(biāo)準(zhǔn)活動(dòng)。人們提出了不同的互連和接口類型來(lái)滿足不同的目的,而用于專用功能(處理器、存儲(chǔ)器和 I/O 等)的新興芯粒技術(shù)正在改變芯片設(shè)計(jì)的方法。

“汽車原始設(shè)備制造商認(rèn)識(shí)到,要控制自己的命運(yùn),他們就必須控制自己的 SoC,”西門子 EDA 虛擬和混合系統(tǒng)副總裁?David Fritz表示。“然而,他們不明白自 1982 年上大學(xué)以來(lái) EDA 已經(jīng)走了多遠(yuǎn)。此外,他們認(rèn)為他們需要進(jìn)入最新的工藝節(jié)點(diǎn),其中一套掩模組將花費(fèi) 1 億美元。他們負(fù)擔(dān)不起。他們也無(wú)法獲得人才,因?yàn)槿瞬艓?kù)相當(dāng)小。所有這些加在一起,原始設(shè)備制造商認(rèn)識(shí)到,要控制自己的命運(yùn),他們需要一種由其他人開(kāi)發(fā)的技術(shù),但可以根據(jù)需要進(jìn)行組合,以擁有獨(dú)特的差異化產(chǎn)品,他們相信至少對(duì)一些人來(lái)說(shuō)是面向未來(lái)的模型年。然后它在經(jīng)濟(jì)上變得可行。唯一符合要求的是芯粒。”

芯粒可以針對(duì)特定功能進(jìn)行優(yōu)化,這可以幫助汽車制造商利用已在多種車輛設(shè)計(jì)中得到驗(yàn)證的技術(shù)滿足可靠性、安全性和安保要求。此外,它們還可以縮短上市時(shí)間并最終降低不同特性和功能的成本。

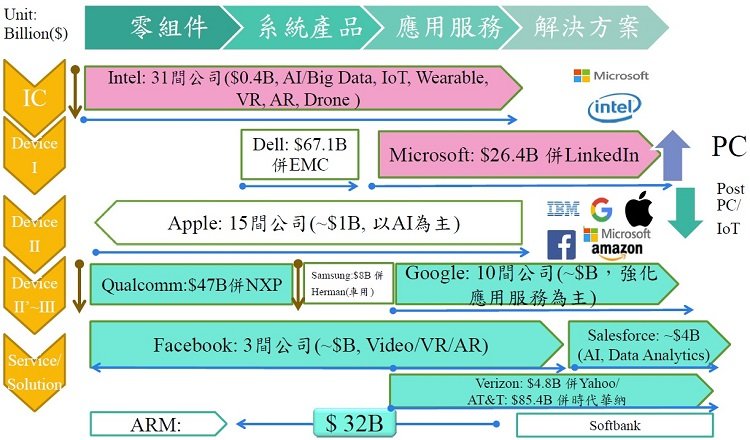

過(guò)去十年來(lái),對(duì)芯片的需求一直在增長(zhǎng)。根據(jù) Allied Market Research 的數(shù)據(jù),全球汽車芯片需求將從 2021 年的 498 億美元增長(zhǎng)到 2031 年的 1213 億美元。這種增長(zhǎng)將吸引更多的汽車芯片創(chuàng)新和投資,而芯粒預(yù)計(jì)將成為一大受益者。

但芯粒市場(chǎng)的成熟還需要一段時(shí)間,并且可能會(huì)分階段推出。最初,供應(yīng)商將提供不同風(fēng)格的專有模具。然后,合作伙伴將共同努力提供芯粒以相互支持,就像一些供應(yīng)商已經(jīng)發(fā)生的那樣。最后階段將是普遍可互操作的芯粒,由 UCIe 或其他互連方案支持。

勢(shì)頭正在增強(qiáng)

從積極的一面來(lái)看,并非所有這一切都是從頭開(kāi)始的。在板級(jí),模塊和子系統(tǒng)始終使用板載芯片到芯片接口,并將繼續(xù)這樣做。各種芯片和 IP 提供商(包括 Cadence、Diode、Microchip、NXP、Renesas、Rambus、Infineon、Arm 和 Synopsys)提供現(xiàn)成的接口芯片或 IP 來(lái)創(chuàng)建接口芯片。

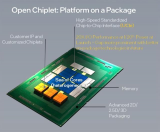

通用 Chiplet Interconnect Express (UCIe) 聯(lián)盟是芯片到芯片開(kāi)放互連標(biāo)準(zhǔn)背后的驅(qū)動(dòng)力。該組織于 2023 年 8 月發(fā)布了最新的 UCIe 1.1 規(guī)范。董事會(huì)成員包括阿里巴巴、AMD、Arm、ASE、Google Cloud、英特爾、Meta、微軟、NVIDIA、高通、三星等。行業(yè)合作伙伴表現(xiàn)出廣泛的支持。AIB 和 Bunch of Wires (BoW) 也已被提出。此外,Arm 剛剛發(fā)布了自己的 Chiplet 系統(tǒng)架構(gòu),以及更新的 AMBA 規(guī)范,以標(biāo)準(zhǔn)化 Chiplet 協(xié)議。

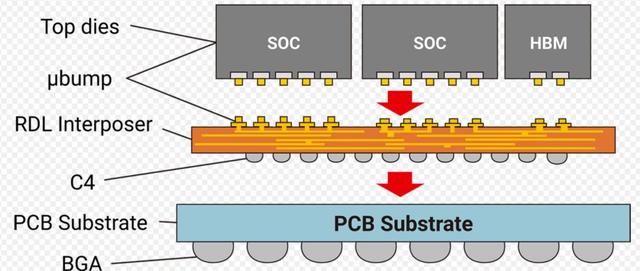

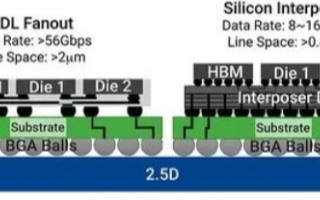

Cadence設(shè)計(jì) IP 高級(jí)產(chǎn)品營(yíng)銷組總監(jiān) Arif Khan 表示:“在必要性的推動(dòng)下,Chiplet 已經(jīng)出現(xiàn)了。”“不斷增長(zhǎng)的處理器和 SoC 尺寸正在達(dá)到標(biāo)線極限和規(guī)模不經(jīng)濟(jì)。工藝技術(shù)進(jìn)步帶來(lái)的增量收益低于每個(gè)晶體管和設(shè)計(jì)成本的上升。封裝技術(shù)(2.5D/3D)和芯片間接口標(biāo)準(zhǔn)化(例如 UCIe)的進(jìn)步將促進(jìn)芯粒的開(kāi)發(fā)。”

如今使用的幾乎所有芯粒都是由英特爾、AMD 和 Marvell 等大型芯片制造商內(nèi)部開(kāi)發(fā)的,因?yàn)樗麄兛梢試?yán)格控制這些芯粒的特性和行為。但各個(gè)層面都在開(kāi)展工作,向更多參與者開(kāi)放這個(gè)市場(chǎng)。當(dāng)這種情況發(fā)生時(shí),較小的公司可以開(kāi)始利用備受矚目的開(kāi)拓者迄今為止所取得的成就,并圍繞這些發(fā)展進(jìn)行創(chuàng)新。

Arteris高級(jí)戰(zhàn)略營(yíng)銷總監(jiān) Guillaume Boillet 表示:“我們?cè)S多人相信,擁有現(xiàn)成的、可互操作的芯粒組合的夢(mèng)想可能需要數(shù)年時(shí)間才能成為現(xiàn)實(shí)。”他補(bǔ)充說(shuō),互操作性將來(lái)自于合作伙伴群體,他們正在解決規(guī)范不完整的風(fēng)險(xiǎn)。

這也提高了 FPGA 和 eFPGA 的吸引力,它們可以為現(xiàn)場(chǎng)硬件提供一定程度的定制和更新。“Chiplet 是真實(shí)存在的,” Flex Logix首席執(zhí)行官 Geoff Tate 說(shuō)道。“目前,一家制造兩個(gè)或更多芯粒的公司比一家制造幾乎沒(méi)有良率的接近光罩尺寸芯片的公司更經(jīng)濟(jì)。Chiplet 標(biāo)準(zhǔn)化似乎還很遙遠(yuǎn)。甚至 UCIe 還沒(méi)有一個(gè)固定的標(biāo)準(zhǔn)。并非所有人都同意 UCIe、裸片測(cè)試以及當(dāng)集成封裝無(wú)法工作時(shí)誰(shuí)負(fù)責(zé)問(wèn)題等。我們確實(shí)有一些客戶使用或正在評(píng)估 eFPGA 的接口,這些接口的標(biāo)準(zhǔn)不斷變化,例如 UCIe。他們現(xiàn)在就可以實(shí)現(xiàn)芯片,并使用 eFPGA 來(lái)適應(yīng)以后的標(biāo)準(zhǔn)變化。”

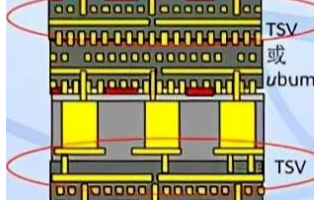

還有其他支持芯粒的努力,盡管出于一些不同的原因——尤其是設(shè)備擴(kuò)展成本的上升以及需要將更多功能集成到芯片中,而芯片在最先進(jìn)的節(jié)點(diǎn)上受到標(biāo)線的限制。但這些努力也為汽車領(lǐng)域的芯粒鋪平了道路,并且有強(qiáng)大的行業(yè)支持來(lái)實(shí)現(xiàn)這一切。例如,在 SEMI、ASME 和三個(gè) IEEE 協(xié)會(huì)的贊助下,新的異構(gòu)集成路線圖 (HIR) 著眼于各種微電子設(shè)計(jì)、材料和封裝問(wèn)題,為半導(dǎo)體行業(yè)制定路線圖。他們當(dāng)前的重點(diǎn)包括 2.5D、3D-IC、晶圓級(jí)封裝、集成光子學(xué)、MEMS 和傳感器以及系統(tǒng)級(jí)封裝 (SiP)、航空航天、汽車等。

在最近舉行的 2023 年異構(gòu)集成全球峰會(huì)上,來(lái)自 AMD、應(yīng)用材料、日月光、泛林集團(tuán)、聯(lián)發(fā)科、美光、Onto Innovation、臺(tái)積電等公司的代表都展示了對(duì) Chiplet 的大力支持。另一個(gè)支持 Chiplet 的組織是Chiplet Design Exchange (CDX) 工作組,它是開(kāi)放域特定架構(gòu)(ODSA) 和開(kāi)放計(jì)算項(xiàng)目基金會(huì) (OCP) 的一部分。Chiplet Design Exchange (CDX) 章程重點(diǎn)關(guān)注 Chiplet 和 Chiplet 集成的各種特性,包括 2.5D 堆疊和 3D 集成電路 (3D-IC) 的電氣、機(jī)械和熱設(shè)計(jì)交換標(biāo)準(zhǔn)。其代表包括Ansys、Applied Materials、Arm、Ayar Labs、Broadcom、Cadence、Intel、Macom、Marvell、Microsemi、NXP、Siemens EDA、Synopsys等。

“汽車公司對(duì)每個(gè)芯粒功能的要求仍處于劇變狀態(tài),”西門子的Fritz指出。“一個(gè)極端有這些問(wèn)題,另一個(gè)極端也有這些問(wèn)題。這是最甜蜜的地方。這就是所需要的。這些是可以開(kāi)展此類工作的公司類型,然后你可以將它們組合在一起。那么這個(gè)互操作性的事情就沒(méi)什么大不了的了。OEM 可能會(huì)說(shuō)“我必須處理所有可能性”,從而使事情變得過(guò)于復(fù)雜。另一種選擇是,他們可能會(huì)說(shuō),‘這就像高速 PCIe 一樣。如果我想從一個(gè)人到另一個(gè)人進(jìn)行溝通,我已經(jīng)知道該怎么做。我有運(yùn)行我的操作系統(tǒng)的驅(qū)動(dòng)程序。這將解決很多問(wèn)題,我相信這就是最終的結(jié)果。”

通用芯粒開(kāi)發(fā)的一種途徑?

展望未來(lái),芯粒將成為汽車和芯片行業(yè)的焦點(diǎn),這將涉及從芯粒 IP 到內(nèi)存互連以及定制選項(xiàng)和限制的一切。

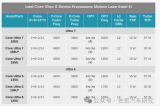

例如,瑞薩電子于 2023 年 11 月宣布了其下一代 SoC 和 MCU 的計(jì)劃。該公司瞄準(zhǔn)了汽車數(shù)字領(lǐng)域的所有主要應(yīng)用,包括有關(guān)其第五代 R-Car SoC 的最新信息,該 SoC 面向高性能應(yīng)用,采用先進(jìn)的封裝內(nèi)芯粒集成技術(shù),旨在為汽車工程師提供更大的定制靈活性他們的設(shè)計(jì)。

瑞薩指出,如果高級(jí)駕駛輔助系統(tǒng)(ADAS)需要更高的人工智能性能,工程師將能夠?qū)⑷斯ぶ悄芗铀倨骷傻絾蝹€(gè)芯片中。該公司表示,這一路線圖是在與一級(jí)和 OEM 客戶多年的合作和討論之后制定的,這些客戶一直呼吁找到一種在不影響質(zhì)量的情況下加速開(kāi)發(fā)的方法,包括在硬件可用之前就設(shè)計(jì)和驗(yàn)證軟件。

“由于對(duì)增加按需計(jì)算的需求不斷增長(zhǎng),以及對(duì)未來(lái)汽車更高水平自主性的需求不斷增長(zhǎng),我們看到了未來(lái)幾年單片解決方案擴(kuò)展和滿足市場(chǎng)性能需求方面的挑戰(zhàn),” 瑞薩電子 SoC 業(yè)務(wù)與戰(zhàn)略高級(jí)總監(jiān)Vasanth Waran說(shuō)。“Chiplet 使計(jì)算解決方案能夠擴(kuò)展并超越市場(chǎng)需求。”他指出

瑞薩電子宣布計(jì)劃從 2025 年開(kāi)始創(chuàng)建專門針對(duì)汽車市場(chǎng)的基于芯粒的產(chǎn)品系列。

標(biāo)準(zhǔn)接口允許 SoC 定制

目前尚不完全清楚標(biāo)準(zhǔn)處理器(這是當(dāng)今使用大多數(shù)芯粒的地方)與為汽車應(yīng)用開(kāi)發(fā)的芯粒之間會(huì)有多少重疊。但隨著這項(xiàng)技術(shù)轉(zhuǎn)移到新市場(chǎng),基礎(chǔ)技術(shù)和發(fā)展肯定會(huì)相互促進(jìn)。

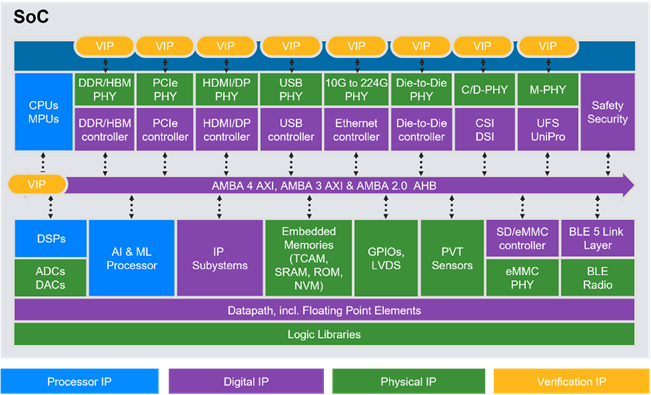

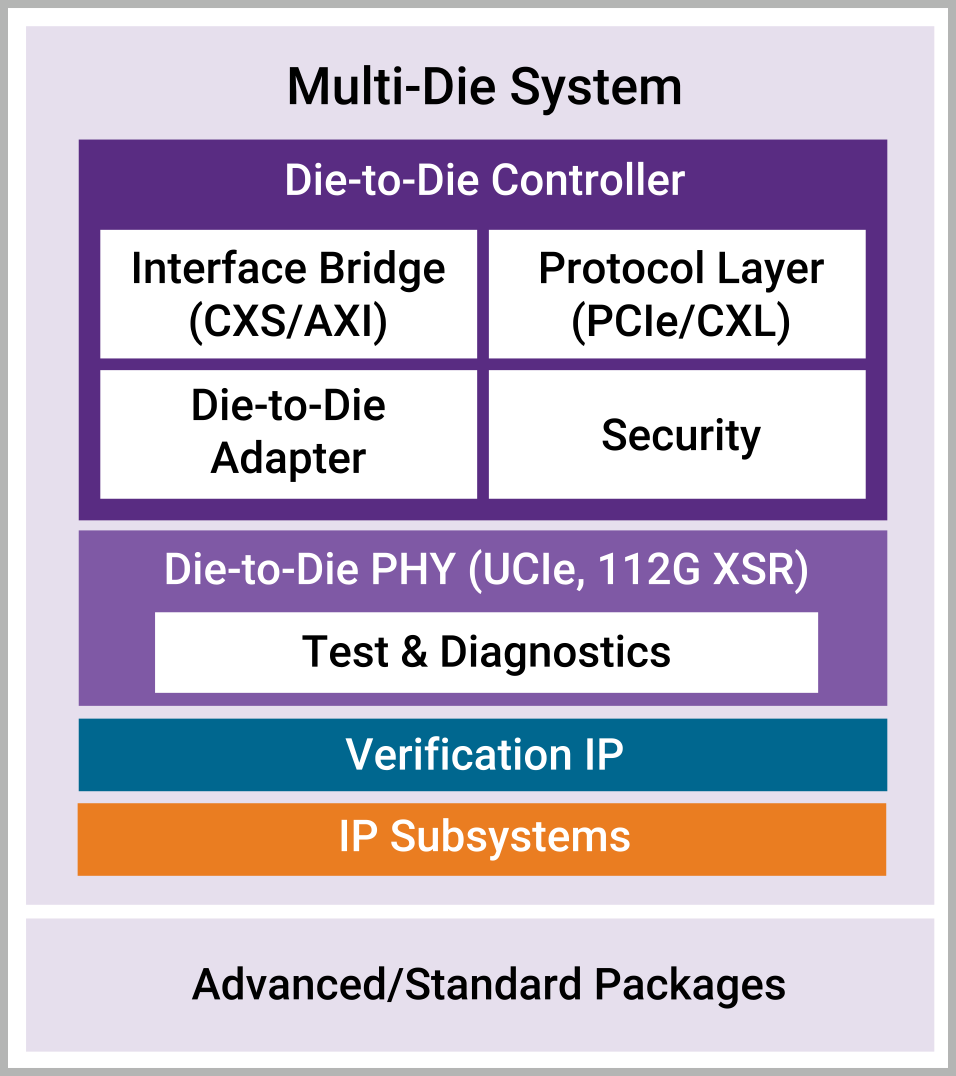

Synopsys IP 加速解決方案組高級(jí)產(chǎn)品經(jīng)理 David Ridgeway 表示:“無(wú)論是 AI 加速器還是 ADAS 汽車應(yīng)用,客戶都需要標(biāo)準(zhǔn)接口 IP 塊。” “圍繞 IP 定制要求提供經(jīng)過(guò)充分驗(yàn)證的 IP 子系統(tǒng)以支持客戶 SoC 中使用的子系統(tǒng)組件非常重要。當(dāng)我說(shuō)定制時(shí),您可能沒(méi)有意識(shí)到在過(guò)去 10 到 20 年的時(shí)間里,在 PHY 端和控制器端,可定制的 IP 已經(jīng)變得多么可定制。例如,PCI Express 已經(jīng)從 PCIe Gen 3 發(fā)展到 Gen 4,再到 Gen 5,現(xiàn)在又發(fā)展到 Gen 6。控制器可配置為支持更小鏈路寬度的多種分叉模式,包括 1 個(gè) x16、2 個(gè) x8 或 4 個(gè) x4。我們的子系統(tǒng) IP 團(tuán)隊(duì)與客戶合作,確保滿足所有定制要求。

對(duì)于人工智能應(yīng)用,信號(hào)和電源完整性對(duì)于滿足其性能要求極其重要。幾乎我們所有的客戶都在尋求挑戰(zhàn)極限,以實(shí)現(xiàn)盡可能最高的內(nèi)存帶寬速度,以便他們的 TPU 每秒可以處理更多的事務(wù)。每當(dāng)應(yīng)用程序是云計(jì)算或人工智能時(shí),客戶都希望獲得最快的響應(yīng)速度。”

進(jìn)入最后階段將是最困難的,并且需要進(jìn)行重大改變。為了確保互操作性,汽車生態(tài)系統(tǒng)和供應(yīng)鏈中足夠多的部分必須聚集在一起,包括硬件和軟件開(kāi)發(fā)商、代工廠、OSAT 以及材料和設(shè)備供應(yīng)商。

圖 1:包括處理器、數(shù)字、PHY 和驗(yàn)證的 IP 模塊可幫助開(kāi)發(fā)人員實(shí)現(xiàn)整個(gè) SoC

優(yōu)化 PPA 的最終目標(biāo)是提高效率,這使得芯粒在汽車應(yīng)用中特別有吸引力。當(dāng)UCIe成熟時(shí),預(yù)計(jì)整體性能將呈指數(shù)級(jí)提升。例如,UCIe 在標(biāo)準(zhǔn)封裝中可以提供 28 至 224 GB/s/mm 的海岸線帶寬(shoreline bandwidth ),在高級(jí)封裝中可以提供 165 至 1317 GB/s/mm 的海岸線帶寬。這意味著性能提高了 20 至 100 倍。將延遲從 20 納秒降低到 2 納秒代表著 10 倍的改進(jìn)。另一個(gè)優(yōu)點(diǎn)是功率效率提高了約 10 倍,分別為 0.5 pJ/b(標(biāo)準(zhǔn)封裝)和 0.25 pJ/b(高級(jí)封裝)。關(guān)鍵是盡可能縮短接口距離。

為了優(yōu)化芯粒設(shè)計(jì),UCIe 聯(lián)盟提供了一些建議:

仔細(xì)規(guī)劃考慮架構(gòu)切割線(即芯粒邊界),優(yōu)化功耗、延遲、硅面積和 IP 重用。例如,定制一個(gè)需要前沿工藝節(jié)點(diǎn)的芯粒,同時(shí)在舊節(jié)點(diǎn)上重復(fù)使用其他芯粒可能會(huì)影響成本和時(shí)間;

需要針對(duì)封裝熱封套、熱點(diǎn)、芯粒布局以及 I/O 布線和分線規(guī)劃熱和機(jī)械封裝約束;

需要仔細(xì)選擇工藝節(jié)點(diǎn),特別是在相關(guān)的電力傳輸方案的背景下;

需要預(yù)先制定芯粒和封裝/組裝部件的測(cè)試策略,以確保在芯粒級(jí)測(cè)試階段發(fā)現(xiàn)硅問(wèn)題,而不是在將它們組裝到封裝中之后;

結(jié)論

標(biāo)準(zhǔn)化芯片間接口的想法正在迅速流行,但實(shí)現(xiàn)這一目標(biāo)的道路需要時(shí)間、精力以及很少相互交流的公司之間的大量協(xié)作。制造一輛汽車需要一個(gè)確定的汽車制造商。使用芯粒構(gòu)建車輛需要整個(gè)生態(tài)系統(tǒng),其中包括開(kāi)發(fā)商、代工廠、OSAT 以及材料和設(shè)備供應(yīng)商的共同合作。

汽車原始設(shè)備制造商是整合系統(tǒng)和尋找創(chuàng)新方法來(lái)削減成本的專家。但仍有待觀察的是,他們能夠如何快速、有效地構(gòu)建和利用可互操作芯粒生態(tài)系統(tǒng),以縮短設(shè)計(jì)周期、改善定制化,并適應(yīng)前沿技術(shù)在完全設(shè)計(jì)和測(cè)試時(shí)可能已經(jīng)過(guò)時(shí)的世界,并提供給消費(fèi)者。

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論