資料介紹

信號(hào)在媒質(zhì)中傳播時(shí),其傳播速度受信號(hào)載體以及周?chē)劫|(zhì)屬性決定。在PCB(印刷電路板)中信號(hào)的傳輸速度就與板材DK(介電常數(shù)),信號(hào)模式,信號(hào)線與信號(hào)線間耦合以及繞線方式等有關(guān)。隨著PCB走線信號(hào)速率越來(lái)越高,對(duì)時(shí)序要求較高的源同步信號(hào)的時(shí)序裕量越來(lái)越少,因此在PCB設(shè)計(jì)階段準(zhǔn)確知道PCB走線對(duì)信號(hào)時(shí)延的影響變的尤為重要。本文基于仿真分析DK,串?dāng)_,過(guò)孔,蛇形繞線等因素對(duì)信號(hào)時(shí)延的影響。

1.引言

信號(hào)要能正常工作都必須滿足一定的時(shí)序要求,隨著信號(hào)速率升高,數(shù)字信號(hào)的發(fā)展經(jīng)歷了從共同步時(shí)鐘到源同步時(shí)鐘以及串行(serdes)信號(hào)。在當(dāng)今的消費(fèi)類(lèi)電子,通信服務(wù)器等行業(yè),源同步和串行信號(hào)占據(jù)了很大的比重。串行信號(hào)比如常見(jiàn)PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信號(hào),源同步信號(hào)比如DDR信號(hào)。

串行信號(hào)在發(fā)送端將數(shù)據(jù)信號(hào)和時(shí)鐘(CLK)信號(hào)通過(guò)編碼方式一起發(fā)送,在接收端通過(guò)時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)得到數(shù)據(jù)信號(hào)和時(shí)鐘信號(hào)。由于時(shí)鐘數(shù)據(jù)在同一個(gè)通道傳播,串行信號(hào)對(duì)和對(duì)之間在PCB上傳輸延時(shí)要求較低,主要依靠鎖相環(huán)(PLL)和芯片的時(shí)鐘數(shù)據(jù)恢復(fù)功能。

源同步時(shí)鐘主要是DDR信號(hào),在DDR設(shè)計(jì)中,DQ(數(shù)據(jù))信號(hào)參考DQS(數(shù)據(jù)選通)信號(hào),CMD(命令)信號(hào)和CTL(控制)信號(hào)參考CLK(時(shí)鐘)信號(hào),由于DQ的速率是CMD DDR2/ DDR3.DDR4預(yù)計(jì)在2015年將成為消費(fèi)類(lèi)電子的主要設(shè)計(jì),隨著DDR信號(hào)速率的不斷提高,在DDR4設(shè)計(jì)中特別是DQ和DQS之間傳輸時(shí)延對(duì)設(shè)計(jì)者提出更高的挑戰(zhàn)。

在PCB設(shè)計(jì)的時(shí)候?yàn)榱藭r(shí)序的要求需要對(duì)源同步信號(hào)做一些等長(zhǎng),一些設(shè)計(jì)工程師忽略了這個(gè)信號(hào)等長(zhǎng)其實(shí)是一個(gè)時(shí)延等長(zhǎng),或者說(shuō)是一個(gè)‘時(shí)間等長(zhǎng)’。

2.傳輸時(shí)延簡(jiǎn)介

Time delay又叫時(shí)延(TD),通常是指電磁信號(hào)或者光信號(hào)通過(guò)整個(gè)傳輸介質(zhì)所用的時(shí)間。在傳輸線上的時(shí)延就是指信號(hào)通過(guò)整個(gè)傳輸線所用的時(shí)間。

Propagation delay又叫傳播延遲(PD),通常是指電磁信號(hào)或者光信號(hào)在單位長(zhǎng)度的傳輸介質(zhì)中傳輸?shù)臅r(shí)間延遲,與“傳播速度”成反比例(倒數(shù))關(guān)系,單位為“Ps/inch”或“s/m”。

從定義中可以看出時(shí)延=傳播延遲*傳輸長(zhǎng)度(L)

其中v為傳播速度,單位為inch/ps或m/s c為真空中的光速(3X108 m/s)

εr為介電常數(shù)PD為傳播延遲,單位為Ps/inch或s/m TD為信號(hào)通過(guò)長(zhǎng)度為L(zhǎng)的傳輸線所產(chǎn)生的時(shí)延L為傳輸線長(zhǎng)度,單位為inch或m

從上面公式可以知道,傳播延遲主要取決于介質(zhì)材料的介電常數(shù),而傳播時(shí)延取決于介質(zhì)材料的介電常數(shù)、傳輸線長(zhǎng)度和傳輸線橫截面的幾何結(jié)構(gòu)(幾何結(jié)構(gòu)決定電場(chǎng)分布,電場(chǎng)分布決定有效介電常數(shù))。嚴(yán)格來(lái)說(shuō),不管是延遲還是時(shí)延都取決于導(dǎo)體周?chē)挠行Ы殡姵?shù)。在微帶線中,有效介電常數(shù)受橫截面的幾何結(jié)構(gòu)影響比較大;而串?dāng)_,其有效介電常數(shù)受奇偶模式的影響較大;不同繞線方式有效介電常數(shù)受其繞線方式的影響。

3.仿真分析過(guò)程

3.1微帶線和帶狀線傳輸時(shí)延

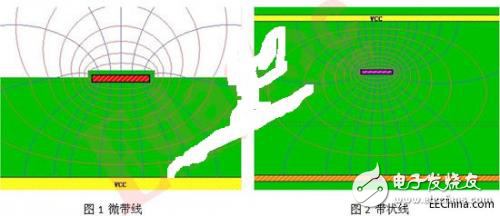

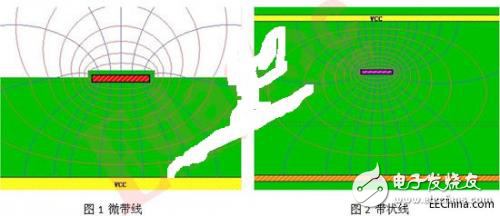

PCB中微帶線是指走線只有一個(gè)參考面,如下圖1;帶狀線是指走線有2個(gè)參考面,如下圖2。

帶狀線由于電磁場(chǎng)都被束縛在兩個(gè)參考面之間的板材中,所以走線的有效介電常數(shù)為板材的介電常數(shù)。

微帶線會(huì)導(dǎo)致部分電磁場(chǎng)暴露在空氣中,空氣的相對(duì)介電常數(shù)約為1.0006,板材如常規(guī)FR4的介電常數(shù)為4.2,那么微帶線的有效介電常數(shù)在1和4.2之間,可以利用下面的公式計(jì)算微帶線的有效介電常數(shù)「Collins,1992」:

εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1 F = 0.02 (εr -1)(1-W/H)2 (W/H 1) 3.2

其中,εe為有效介電常數(shù),εr為電路板材料的介電常數(shù),H為導(dǎo)線高于地平面的高度,W為導(dǎo)線寬度,T為導(dǎo)線厚度。

1.引言

信號(hào)要能正常工作都必須滿足一定的時(shí)序要求,隨著信號(hào)速率升高,數(shù)字信號(hào)的發(fā)展經(jīng)歷了從共同步時(shí)鐘到源同步時(shí)鐘以及串行(serdes)信號(hào)。在當(dāng)今的消費(fèi)類(lèi)電子,通信服務(wù)器等行業(yè),源同步和串行信號(hào)占據(jù)了很大的比重。串行信號(hào)比如常見(jiàn)PCIE,SAS,SATA,QPI,SFP+,XUAI,10GBASE-KR等信號(hào),源同步信號(hào)比如DDR信號(hào)。

串行信號(hào)在發(fā)送端將數(shù)據(jù)信號(hào)和時(shí)鐘(CLK)信號(hào)通過(guò)編碼方式一起發(fā)送,在接收端通過(guò)時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)得到數(shù)據(jù)信號(hào)和時(shí)鐘信號(hào)。由于時(shí)鐘數(shù)據(jù)在同一個(gè)通道傳播,串行信號(hào)對(duì)和對(duì)之間在PCB上傳輸延時(shí)要求較低,主要依靠鎖相環(huán)(PLL)和芯片的時(shí)鐘數(shù)據(jù)恢復(fù)功能。

源同步時(shí)鐘主要是DDR信號(hào),在DDR設(shè)計(jì)中,DQ(數(shù)據(jù))信號(hào)參考DQS(數(shù)據(jù)選通)信號(hào),CMD(命令)信號(hào)和CTL(控制)信號(hào)參考CLK(時(shí)鐘)信號(hào),由于DQ的速率是CMD DDR2/ DDR3.DDR4預(yù)計(jì)在2015年將成為消費(fèi)類(lèi)電子的主要設(shè)計(jì),隨著DDR信號(hào)速率的不斷提高,在DDR4設(shè)計(jì)中特別是DQ和DQS之間傳輸時(shí)延對(duì)設(shè)計(jì)者提出更高的挑戰(zhàn)。

在PCB設(shè)計(jì)的時(shí)候?yàn)榱藭r(shí)序的要求需要對(duì)源同步信號(hào)做一些等長(zhǎng),一些設(shè)計(jì)工程師忽略了這個(gè)信號(hào)等長(zhǎng)其實(shí)是一個(gè)時(shí)延等長(zhǎng),或者說(shuō)是一個(gè)‘時(shí)間等長(zhǎng)’。

2.傳輸時(shí)延簡(jiǎn)介

Time delay又叫時(shí)延(TD),通常是指電磁信號(hào)或者光信號(hào)通過(guò)整個(gè)傳輸介質(zhì)所用的時(shí)間。在傳輸線上的時(shí)延就是指信號(hào)通過(guò)整個(gè)傳輸線所用的時(shí)間。

Propagation delay又叫傳播延遲(PD),通常是指電磁信號(hào)或者光信號(hào)在單位長(zhǎng)度的傳輸介質(zhì)中傳輸?shù)臅r(shí)間延遲,與“傳播速度”成反比例(倒數(shù))關(guān)系,單位為“Ps/inch”或“s/m”。

從定義中可以看出時(shí)延=傳播延遲*傳輸長(zhǎng)度(L)

其中v為傳播速度,單位為inch/ps或m/s c為真空中的光速(3X108 m/s)

εr為介電常數(shù)PD為傳播延遲,單位為Ps/inch或s/m TD為信號(hào)通過(guò)長(zhǎng)度為L(zhǎng)的傳輸線所產(chǎn)生的時(shí)延L為傳輸線長(zhǎng)度,單位為inch或m

從上面公式可以知道,傳播延遲主要取決于介質(zhì)材料的介電常數(shù),而傳播時(shí)延取決于介質(zhì)材料的介電常數(shù)、傳輸線長(zhǎng)度和傳輸線橫截面的幾何結(jié)構(gòu)(幾何結(jié)構(gòu)決定電場(chǎng)分布,電場(chǎng)分布決定有效介電常數(shù))。嚴(yán)格來(lái)說(shuō),不管是延遲還是時(shí)延都取決于導(dǎo)體周?chē)挠行Ы殡姵?shù)。在微帶線中,有效介電常數(shù)受橫截面的幾何結(jié)構(gòu)影響比較大;而串?dāng)_,其有效介電常數(shù)受奇偶模式的影響較大;不同繞線方式有效介電常數(shù)受其繞線方式的影響。

3.仿真分析過(guò)程

3.1微帶線和帶狀線傳輸時(shí)延

PCB中微帶線是指走線只有一個(gè)參考面,如下圖1;帶狀線是指走線有2個(gè)參考面,如下圖2。

帶狀線由于電磁場(chǎng)都被束縛在兩個(gè)參考面之間的板材中,所以走線的有效介電常數(shù)為板材的介電常數(shù)。

微帶線會(huì)導(dǎo)致部分電磁場(chǎng)暴露在空氣中,空氣的相對(duì)介電常數(shù)約為1.0006,板材如常規(guī)FR4的介電常數(shù)為4.2,那么微帶線的有效介電常數(shù)在1和4.2之間,可以利用下面的公式計(jì)算微帶線的有效介電常數(shù)「Collins,1992」:

εe = (εr +1)/2 + (εr -1)/2(1+12H/W)-1/2 + F -0.217(εr -1)T/√WH 3.1 F = 0.02 (εr -1)(1-W/H)2 (W/H 1) 3.2

其中,εe為有效介電常數(shù),εr為電路板材料的介電常數(shù),H為導(dǎo)線高于地平面的高度,W為導(dǎo)線寬度,T為導(dǎo)線厚度。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- PCB走線和過(guò)孔電流計(jì)算工具(MATLAB) 198次下載

- PCB設(shè)計(jì)布線中的3種特殊走線技巧 0次下載

- PCB直角走線的影響

- PCB特殊走線技巧——蛇形線

- 為了信號(hào)完整性,如何控制PCB的控制走線阻抗?資料下載

- PCB直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響?資料下載

- 直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響?資料下載

- PCB Layout中直角走線產(chǎn)生的影響解析 0次下載

- PCB Layout中的專(zhuān)業(yè)走線解析 0次下載

- 淺談PCB Layout中直角走線產(chǎn)生的影響 0次下載

- 淺談信號(hào)在PCB走線中傳輸時(shí)延 0次下載

- PCB走線與擺件規(guī)則 0次下載

- PCB_Layout中的走線策略 0次下載

- PCB_Layout中的走線策略 0次下載

- PCB走線鍍錫 0次下載

- 高速差分信號(hào)走線要點(diǎn)分析 570次閱讀

- 為什么在PCB layout時(shí)不能走直角線 1779次閱讀

- 高速信號(hào)的走線閉環(huán)規(guī)則 1170次閱讀

- 詳解PCB走線與信號(hào)完整性問(wèn)題 1774次閱讀

- PCB設(shè)計(jì)中如何實(shí)現(xiàn)等長(zhǎng)走線 1.9w次閱讀

- PCB板上多長(zhǎng)的走線才是傳輸線? 5777次閱讀

- PCB直角走線究竟會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響 5531次閱讀

- 高速信號(hào)PCB走線屏蔽設(shè)計(jì)方案 3186次閱讀

- 直角走線會(huì)對(duì)信號(hào)傳輸產(chǎn)生什么影響 1924次閱讀

- PCB走線對(duì)信號(hào)時(shí)延的影響分析 5809次閱讀

- 高速PCB設(shè)計(jì)中的走線技巧 5545次閱讀

- 行業(yè) | 為什么PCB走線中避免出現(xiàn)直角?直角走線真的那么可怕嗎? 2.1w次閱讀

- 高速PCB設(shè)計(jì)中走線屏蔽的各項(xiàng)規(guī)則解析 4884次閱讀

- 直角走線會(huì)對(duì)信號(hào)傳輸產(chǎn)生多大的影響 7484次閱讀

- PCB設(shè)計(jì)的直角走線,差分走線,蛇形線走線技巧 3433次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1497次下載 | 免費(fèi)

- 2TC358743XBG評(píng)估板參考手冊(cè)

- 1.36 MB | 330次下載 | 免費(fèi)

- 3單片機(jī)典型實(shí)例介紹

- 18.19 MB | 103次下載 | 1 積分

- 4S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 28次下載 | 1 積分

- 5筆記本電腦主板的元件識(shí)別和講解說(shuō)明

- 4.28 MB | 18次下載 | 4 積分

- 6開(kāi)關(guān)電源原理及各功能電路詳解

- 0.38 MB | 15次下載 | 免費(fèi)

- 79天練會(huì)電子電路識(shí)圖

- 5.91 MB | 6次下載 | 免費(fèi)

- 8100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專(zhuān)業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30321次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開(kāi)關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21540次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537794次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183278次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論